在高速成長的非揮發性記憶體(NVM)市場的推動下,十年來,世界上出現了幾項具有突破性的記憶體技術,將業界舊有標準淘汰出局,並擴大了快閃記憶體技術的應用領域[1]。目前一般業界認同任何一項技術如果取得成功,就會在未來十年內變為產品。業界現階段也針對兩大類全新的非揮發性記憶體進行了實際應用的研究,其中一類是基於無機材料的記憶體技術,如鐵電記憶體(FeRAM)、磁阻記憶體(MRAM)或相變化記憶體(PCM),另一類記憶體技術則基於有機材料,鐵電或導電開關聚合物。值得注意的是,眼看這個十年就要結束,在這些接替快閃記憶體的非揮發性記憶體當中,只有相變化記憶體具備進入廣闊市場的能力表現,被視為下一個十年的主流記憶體技術。

替代快閃記憶體的非揮發性記憶體

在目前研究的兩大類新的非揮發性記憶體技術中,由於鐵電或導電開關聚合體的有機材料的記憶體技術還不成熟,處於研發階段。部分從事這類記憶體材料研究的研發小組開始認為,這個概念永遠都不會變成真正的產品。事實上,使這些概念符合標準CMOS整合要求及其製造溫度,還需要解決幾個似乎難以逾越的挑戰。另一方面,業界對基於無機材料的新非揮發性記憶體概念的研究時間比較長,並在過去幾年發表了幾個產品原型。

FeRAM技術概念早在上個世紀90年代就已經出現。雖然在研究過程出現過很多與新材料和製造模組有關的技術難題,但經過十年的努力,即便固有的製程縮小限制,技術節點遠遠高於快閃記憶體,鐵電記憶體現階段仍已導入商業化。這個記憶體概念仍然使用能夠被電場極化的鐵電材料。溫度在居裏點(Curie point)以下時,立方體形狀出現晶格變形,此時鐵電體發生極化;溫度在居裏點以上時,鐵電材料變成順電相。到目前為止,業界已提出多種FeRAM單元結構(如圖一所示),這些結構屬於兩種方法體系,一種是把鐵電材料整合到一個單獨的記憶元件內,即鐵電電容器內(在雙電晶體/雙電容(2T2C)和單晶體管/單電容(1T1C)兩種元件內整合鐵電材料的方法)[2],另一種是把鐵電材料整合到選擇元件內,即鐵電場效應電晶體[3]內。所有的FeRAM架構都具有存取速度快和可以隨機讀取所有儲存單元的優點,而目前FeRAM技術研發的主攻方向是130nm製程的64Mb記憶體[4]。

《圖一 FeRAM單元架構方案》

|

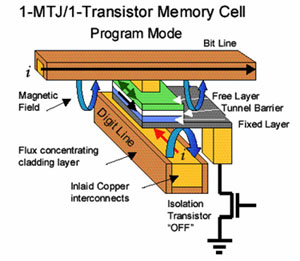

多年來,磁隧道結(MTJ)儲存單元(如圖二所示)一直是MRAM研發人員的主要研發工作[5],MTJ由一個電晶體和一個電阻組成(1T/1R)。這些技術是利用隧道結與磁阻材料整合產生的特殊效應:當施加一個磁場時,電阻就會發生變化。存取速度極快的無損性讀取效能是確保高效能、讀寫次數相同和低功耗操作的前提。MRAM的主要缺點是該技術固有的寫操作電流過高和技術節點縮小受限。為了克服這兩大制約因素,業界最近提出了SPRAM(Spin-transfer Torque RAM)解決方案[6],這項創新技術是利用自旋轉換矩(Spin-transfer Torque)引起的電流感應式開關效應。儘管這一創新方法在一定程度上解決了MRAM的一些常見問題,但是還有很多挑戰等待研究人員克服(例如:自讀擾動、寫次數、單元整合等)。目前MRAM的製造只局限於4Mb陣列180nm製程的產品[7]。

《圖二 採用MTJ 1T1R方法的MRAM單元架構[5]》  |

相變化記憶體

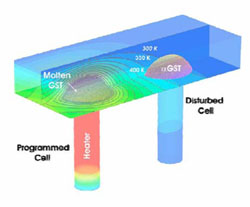

PCM是最好的快閃記憶體替代技術,能夠涵蓋不同的非揮發性記憶體應用領域,滿足高效能和高容量兩種應用要求。PCM利用溫度變化引起硫系合金(Ge2Sb2Te5)相態逆變的特性。基本單元結構由一個電晶體和一個電阻構成(1T/1R),利用電流引起的焦耳熱效應(圖三)對單元進行寫操作,透過檢測非晶相態和多晶相態之間的電阻變化讀取儲存單元。雖然這項技術最早可追溯到上個世紀70年代,但直到最近人們才重新嘗試將其用於非揮發性記憶體[9](採用相變合金的光電儲存設備達到商業成功,也促進了人們發現效能更優異的相變材料結構的研究活動),相變化記憶體證明其具有達到製造成熟度的能力[10]。我們在本文後面的表格中比較了相變化記憶體與其它的成熟的非揮發性記憶體技術。整合了非揮發性記憶體和DRAM兩大記憶體的優點於一身,PCM的新特性對新型應用極具吸引力,同時也是具備連續性和突破性的記憶體技術。從應用角度看,PCM可用於所有的記憶體系統,特別適用於消費電子、電腦、通訊三合一電子設備的記憶體系統 [11]。在無線系統中,PCM可用作代碼執行記憶體;PCM可用作可改寫唯讀記憶體,保存處理頻率最高的資料結構以外的全部資料結構,在固態儲存子系統中,保存經常讀取的頁面;在立即處理資料時,保存更容易管理的資料元素;其非揮發性也可運用電腦平臺中。

《圖三 PCM原型結構的被寫儲存單元的自加熱示意圖》  |

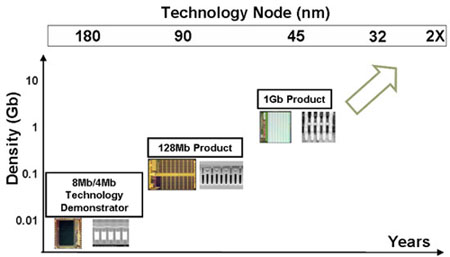

PCM的技術發展路線如圖五所示。業界利用180nm技術節點開發出了首個晶片測試載具,並驗證了此項技術的可行性[12]。BJT選定的單元被高效能和高容量記憶體選用,因為單元尺寸可以是~5F2 (其中F是儲存單元半節距最小值)。雖然單元尺寸較大(~20F2),但是整合記憶體只需在邏輯製程中增加很少的掩模(mask),極具成本優勢,因此,MOS選定的單元適用於系統晶片或嵌入式應用[13]。

《圖五 PCM技術發展路線圖》

|

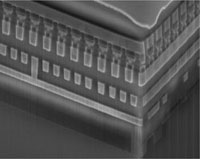

英特爾和意法半導體開發出一款名為Alverstone的128Mb的90nm相變化記憶體,該產品現已導入商業化應用[14]。另一款 45nm 1Gb PCM產品目前也已進入進階研發階段,該產品設計的單元尺寸為5.5F2 (圖四)。

《圖四 45nm技術PCM陣列的截面圖》  |

PCM技術研發將沿著不同的路線並行前進。主流的開發路線將是採用BJT選定的單元,沿著光刻技術發展路線,縮小現有技術架構,提供最小的單元尺寸。除廣泛使用的 Ge2Sb2Te5以外,利用新的硫系合金是另外一個重要的研究領域,因為這可能會開創全新的應用領域;結晶速度極快或結晶溫度更高的合金將會更具發展潛力[16]。

在記憶體架構方面,一條研究主線是利用交叉點陣列,達到一層以上的記憶體疊層。透過在後端製程中整合p-n結或肖特基二極體(Schottky diode)作為選擇元件,業界已經提出了不同的解決方法[17-18]。硫系材料特別適合這種堆疊方法,因為在硫系材料堆疊後,其相變特性(像Ge2Sb2Te5)可以構成記憶體元件,同時其電子開關特性(像OTS)構成選擇元件[19](圖六)。在這種情況下,單元尺寸可以達到4F2,位元大小是單元尺寸的幾分之一,實際大小取決於疊層數量[19],這項技術適用於高容量記憶體,特別是儲存應用。

《圖六 一層採用CMOS技術全整合的交叉點PCM陣列》  |

總而言之,現有的技術成熟度、技術節點縮小能力、持續開發的應用範圍,結合新的材料和架構可,這一切均為相變化記憶體技術未來十年在記憶體市場中的發展奠定基礎。

---Roberto Bez為恆憶研發中心技術開發部研究員,負責恆憶相變儲存技術(PCM)的研發工作---

參考文獻

[I]R.Bez, “Chalcogenide PCM: a memory technology for next decade”, IEDM Tech. Dig., 2009.

[2] S.-H. Oh et al., “Noble FeRAM Technologies with MTP Cell Structure and BLT Ferroelectric Capacitors”, IEDM Tech. Dig., 2003, p. 835, 2003.

[3] H. Ishiwara, ” Recent Progress in FET-type Ferroelectric Memories”, IEDM Tech. Dig., 2003, p. 263, 2003. [4] H. McAdams et al., “A 64Mbit Embedded FeRAM Utilizing a 130nm, 5LM Cu/FSG Logic Process”, Symp. On VLSI Tech., 2003.

[5] M. Durlam et al., “A 0.18µm 4Mb Toggling MRAM”, IEDM Tech. Dig., 2003, p. 995, 2003. [6] M. Hosomi et al., “A Novel Nonvolatile Memory with Spin Torque Transfer Magnetization Switching: Spin-RAM”, IEDM Tech. Dig., 2005. [7] See www.everspin.com

[8] A. Redaelli et al., “Threshold switching and phase transition numerical models for phase change memory simulations”, J. Appl. Phys., vol. 103, 111101, 2008.

[9] S. Lai and T.Lowrey., “OUM - A 180 nm Nonvolatile Memory Cell Element Technology for Stand Alone and Embedded Applications”, IEDM Tech. Dig. 2001, p. 803, 2001.

[10] A. Pirovano et al., “Self-Aligned µTrench Phase-Change Memory Cell Architecture for 90nm Technology and Beyond”, Proc. ESSDERC 07., p. 222, 2007.

[II] S.Eilert et al., “Phase Change Memory: a new memory enables new memory usage models”, 2009 IEEE IMW,

Monterey, pag.72 , 2009.

[12] F.Pellizzer et al., “Novel uTrench PCM cell for embedded and stand-alone NVM applications”, Symp. On VLSI

Tech., pag.18, 2004.

[13] R.Annunziata et al., “Phase Change Memory Technology for Embedded Non Volatile Memory Applications for

90nm and Beyond”, IEDM Tech. Dig., 2009.

[14] F.Pellizzer et al.,, “A 90nm Phase-Change Memory Technology for Stand-Alone Non-Volatile Memory

Applications”, Symp. on VLSI Tech., pag.122, 2006.

[15] G.Servalli, “A 45nm Generation Phase Change Memory Technology”, IEDM Tech. Dig., 2009.

[16] R.Bez, “Development Lines for Phase Change Memories”, EPCOS 2008, Prague (http//www.epcos.org).

[17] Y.Sasago et al., “Cross-point pcm with 4F2 cell size driven by low-contact-resistivity poly-Si diode”, Symp.

VLSI Tech., T2B1, 2008.

[18] G.Tallarida et al., “Low temperature rectifying junctions for crossbar non-volatile memory devices”, IMW,

Monterey, 2009.

[19] S.R.Ovshinsky, “Reversible electrical switching phenomena in disordered structures”, Phys. Rev. Lett. 21,

pag.1450, 1968.

[20] D.Kau et al., “A Stackable Cross Point Phase Change Memory”, IEDM Tech. Dig., 2009.