3D-IC 在90 年代被稱之為VIC (Vertically Integrated Circuits),或 CUBIC (cumulatively bonded IC)、3D integration、VIP (vertical interconnect package)、VIS (vertical system integration) 或者是 3d configuration。

3D IC的三種堆疊方式

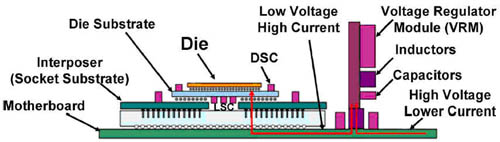

即使是3 維整合(3D integration),也有人稱之為垂直整合(Vertical System Integration; VSI)。或者稱之為方塊 「Cube」。 圖 1是IMEC 的 System in a Cube 概念,從圖上,我們可以看到在各個電路(看來像是PC 載版)的夾層中間,還可以提供 「側面」的銲錫隆點(solder bump)。因此,似乎在這個系統的前後左右還可以繼續「併接」相關電路。這種概念的確很新穎。如圖2,為一個水平封裝系統與垂直封裝系統的結合的實際電路圖,右邊垂直的電路是用來提供左邊電路所需要的電源,因此,其包含了電壓調整模組(Voltage Regulator Module; VRM),電感 (inductor),與電容(capacitor)。輸入為一個高壓低電流的訊號,輸出給左邊電路則是低壓高電流的訊號。這樣看來更像是一種3D 整合。

《圖一 IMEC 的System in a cube 觀念 (Source:IMEC)》  |

「Cube」的觀念,的確出現在很多電路中,Berkeley的無線通訊研究中心(Berkeley Wireless Re3search Center; BWRC)就嘗試將一個胎壓感測器(tire-pressure)以 Cube 觀念完成。該系統總共堆疊了5 層的電路,與歐盟的 e-Cube 不一樣的是該系統並無配備「能量攫取器」 (energy harvester),取而代之的是內含一個NiMH 電池以提供電力,再由內部的電源管理系統將所需的DC 電源供應給各系統。 Intel 早在1994 年,為了大量平行處理(massively parallel processing)也設計了一個EXECUBE的系統,只是系統裡面的Cube概念,也只是一邏輯概念,因為系統上的處理單元(processor element)還是以陣列的方式相互連結。

《圖二 水平封裝系統與垂直封裝系統的結合 (Source: RPI)》

|

從堆疊這個名詞來看,至少可以有下列三種不同的堆疊方式。

電晶體堆疊 (Transistor Stacking)

也就是將電晶體做成非平面(Non-planar)的電晶體。例如:平面式雙閘極電晶體 (Planar Double Gate Transistors),Flexfet,FinFET,Tri-gate transistors (Intel),Gate-all-around (GAA) FETs…等。

封裝層次的堆疊 (Package Stacking)

也就是將不同的封裝形式的「封裝」,再以另一個封裝堆疊起來。例如: SiP (System in Package),SoP (System on Package,PiP (Package in Package),SCSP (Stacked Chip Scale Package),CoC (Chip on Chip),內藏元件 (Embedded Device )…等。

晶元堆疊/晶元片堆疊 (Die Stacking/Wafer Stacking)

也就是將不同的晶粒或晶圓片針對Die-to-Die或Die-to-Wafer 或Wafer-to-Wafer 用鍵合(Bonding)的方式接合。這其中,又包含了一種稱之為無接觸型3D IC (Contactless 3D IC)。

TSV製程 關鍵名詞徹底解析

目前所謂的3D-IC就是以晶元堆疊/晶元片堆疊為主,並結合矽穿孔(Through Silicon Via; TSV) 技術的一種半導體製程技術。首先 TSV 的名詞隨著時代的演進,各家公司的技術不同,看法不同,所以定義並不太相同,更是相當混亂,可能只是黑道大哥的一些土語 (jargon)。以下是我們整理所看到的TSV製程中的相關不同名詞,從這些名詞我們可以更加了解3D-IC 的相關面貌。

銅釘貫通矽晶導孔(Copper-nail TSV)

或稱之為Copper Plug,此為 IMEC 2008 年的名詞。在IMEC 的文件中,IMEC 說明這個在前端製程(FEOL)製作後與後端製程(BEOL)前所挖的洞稱之為Copper nail。此製程只要用到單一鑲嵌結構 (Damascene)。銅釘的大小約1~5um。稱之為銅針,並不是沒有他的道理,這是因為挖洞的過程中並沒有貫穿,在金屬化過程後,看來只是像圖釘一樣釘住基底。

《圖三 IMEC 的Copper Nail 觀念》

|

銅栓(Copper Plug)

此為新加坡IME 2008 年的名詞。他們稱 Cu Plug 就是TSV,但是,這是因為在說明TSV 與下層的間的接觸墊(pad)之間關係,這個TSV 就像要拴住接觸墊,稱之為On-pad 設計。從製程的觀點來看,因為TSV 會被 Barrier Layer 與 Isolation Layer 所包圍,就像是一個類似一個可以套繩索的栓,這個名詞也挺傳神的。

《圖四 IME 的銅栓 (Copper Plug) 概念》  |

晶圓貫穿孔(Through-Wafer Via)

此為Stanford Univ. 的 E. L. Ginzton Laboratory and Center for Integrated Systems 在1999 年與Surface Technology Systems 2005 年 與Delft 大學2006 針對RF MEMS的名詞。這個名詞捨去Si, 就是在強調 「挖洞」的動作不一定是在 Si 的晶圓片上。如圖,是一家公司Skyworks Solutions Inc. 在GaAs 晶圓片上用RIE技術所挖的一個TWV。

晶圓貫穿接線(Through Wafer Interconnect; TWI)

此為 Micron 2006~2008 年名詞。這是 Micron OSMIMU技術中 TWI, RDL (Redistribution Layer),與WLE(Wafer Level Encapsulation)其中一環。TWI 的技術又可以分為前晶圓面TWI(frontside TWI)與後晶圓面TWI(backside TWI) (圖 10)。看這個名詞就知道 TSV 功能著重用於連線(interconnect)。

《圖五 Micron 的OSMIMU 技術的 TWI (左)Frontside TWI (右)Backside TWI。》 - BigPic:599x317  |

貫通中介層智慧連接(Smart Connection with Feed-Through Interposer ; SMAFTI)

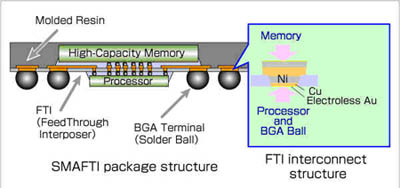

這是 2006 年,NEC 用此種SMAFTI 技術在影像處理系統所用的邏輯和記憶體晶片之間,建立起超過1,000個以上的三維互連。這其實是一種晶圓級封裝技術,它使用7um厚的聚醯亞胺樹酯(Polymide Resin)介電層和15um寬的銅互連,來建構對中介層的佈線路徑,因而產生間距為50um的縱向互連,能夠支援高達100Gbps的傳輸速率,並且可以降低功耗,高階手機、視訊遊戲或數位電視等應用。

圖6為 NEC SMAFTI 技術基本說明。這是一個堆疊記憶體(上層)與處理器(下層)的系統,從圖上可以知道上層的記憶體會透過外包的樹酯與下層的處理器相連,樹酯中間會有貫穿的電極導孔,這個電極導孔其組成是鎳 (Ni), 銅 (Cu)與無電解金 (Electroless Au)。上下兩層的電路便透過這個電極導孔作電器與機械的相連。最後透過下層的 BGA 錫球與外界相連。此技術顯然比傳統的 SiP 更簡單,因此可以較低的製作費用,更重要的是可以提供更高的記憶體資料寬度。根據NEC 的說明,這個技術可以堆疊高達8 層的記憶體。

《圖六 NEC 的 SMARFTI 3D IC 連線技術特性》  |

矽穿洞電極(Si Through-hole electrodes)

此為 Renesas 2008 的名詞。這個名詞的特點是他強調了「電極」(electrode),也就是穿過Si 的一個電極,這樣的概念與我們平常視覺上可看到的表面電極不同,他強調這個電極是穿洞的。圖 8是Renesas 所提供的圖,當然看來就是TSV。

《圖七 Renesas 的 Si Through Hole Electrodes 技術。》  |

穿洞電極 (Through-hole electrode)

此為 GSA (Global Semiconductor Alliance) 2007 與Renesas 2008 年的名詞。 此名詞與Resensas 的Si Through-hole electrodes 類似。

矽穿透式電極 (Si through-electrodes)

此為 NEC, Oki, Elpida 2008 年的名詞。此名詞與Resensas 的Si Through-hole electrodes 類似。

矽穿封裝孔(Through Package Via; TPV)

這是Georgia Tech. 2009 的名詞。這是因為 Georgai Tech. 成立了一個 「3D 全矽製程模組論壇」(3D All Silicon System Module (3DASSM) Consortium),這個論壇著重在 「封裝系統」,因此,挖洞的考量就不一定是在晶圓片上面。

Through Mold Via (TMV)

這種技術為 Amkor 所針對PoP 技術所發展,不同於 TSV是用來穿透矽基底,這種技術是穿透外模(Mold)。圖 10是Amkor 的TMV 技術(2009),這個技術號稱可以結合TSV 技術,使得PoP封裝的密度可以提升。

《圖八 Amkor 的 TMV 技術》  |

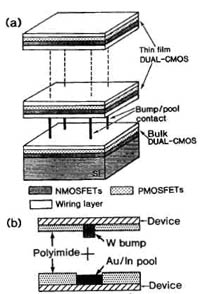

凸塊/凹槽 (bump/pool contact)

NEC 在 1991 年的名詞,這個凸塊/凹槽是ㄧ個上下對稱的結構,當上下結合的時候看來也像是內部的一個TSV(圖 11)。

《圖九 NEC 的 Bump/Pool 觀念(1991)(Source: NEC)》  |

矽對矽連線 (Silicon-Silicon Interconnection; SSI)

此為 IBM 2008 年名詞。IBM 的Silicon-Silicon Interconnection這個名詞不一定是在說TSV。它包含了 chip-to-chip assembly, chip-to-wafer bonding, wafer-to-wafer bonding with solder, thin-metal, copper-copper, 與 oxide-to-oxide boinding. 這個名詞是廣泛的3D Integration,也就是說3D Integration 除了要透過TSV 也要有RDL 或者是Interposer 間的繞線, TSV 只是Si 與Si 間的電路連接的一種選擇。

矽壕溝 (Si Trench)

此為日本東北大學小柳光正教授(Prof. Mitsumasa Koyanagi)在2000 年設計一個3D 分享記憶體 (Share Memory) 技術文章的名詞。 當時並無TSV 這個名詞,因此,他代表著是一個內埋連線(buried interconnect)。當初即已經做到2um 大小,60um 深的技術了。其實它應該說是Si trench 蝕刻。到了 2008 年,TSV 為大家所共用,確認其Si Trench為 形成TSV所需三個技術其中之一: 1) deep-trench etching, 2) dielectric layer formation, 與3) filling with a conductive material。