作為常見的電腦主記憶體,動態隨機存取記憶體(DRAM)現已發展出多元的標準,本文上篇已回顧了各種DRAM的特色,下篇則將進一步探討3D結構發展下的DRAM類型,並分享愛美科的DRAM發展途徑。

動態隨機存取記憶體(dynamic random access memory;DRAM)的類型多元,包含本文上篇所提到的常規DDR、LPDDR、GDDR等,然而上述DRAM發展之時並沒有3D革命。

藉由3D技術—我們這裡指的是運用矽穿孔(through-silicon-vias;TSVs),也就是晶片內部的垂直內連導線,這些導線能透過晶片之間的微凸塊(microbump)互連。運用多條尺寸極小的垂直內連導線,兩個相互堆疊的晶片就可能可以進行資料傳輸,這使得全新的晶片設計和架構成為可能。

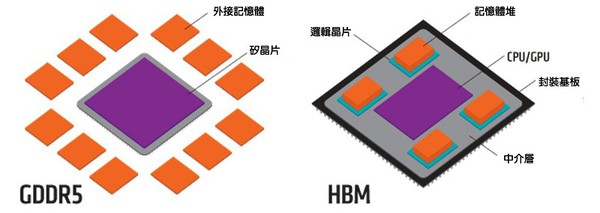

那我們就來看看先前討論的DRAM種類,他們有哪些3D架構的對應版本吧!最有名的就是高頻寬記憶體(high bandwidth memory;HMB),它也是GDDR的3D對應版;而混合記憶體立方體(hybrid memory cube;HMC)則由美光開發,是計畫要用於類似通用DDR應用的3D DRAM版本,但在2018年被取消了。Wide I/O記憶體則是三星所推動的一個國際固態技術協會(JEDEC)標準,作為系統單晶片(SoC)內LPDDR記憶體的3D對照版,但我們還未聽過任何的實際應用。

3D革命

HBM

HBM和GDDR多有雷同,它也與GPU緊密整合,而且也不放在GPU上方,畢竟我們還需要大量電容並將晶片降溫。那麼HBM差在哪?

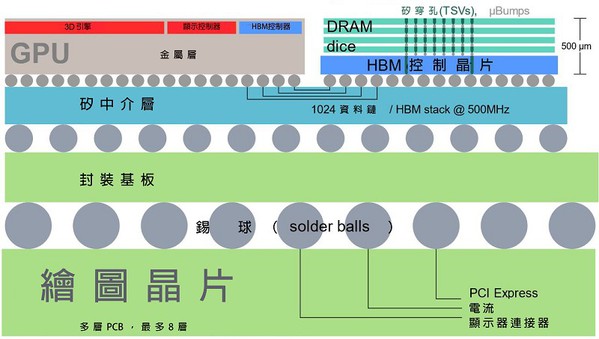

首先,HBM在PCB板的位置並不在GPU旁邊,而是在連接GPU與晶片的中介層(interposer)上。目前,通常使用的是被動式矽中介層,亦即一大片不含任何主動元件的矽晶片,只有內連導線。

這種中介層的優點是能在上面佈建更多平行導線,而不會耗費大量功率。因此,一個極寬的匯流排誕生了,以往這在PCB上是不可能實現的。然而,雖然這種中介層相當容易製造,但畢竟還是一大塊矽晶片,因此成本也較高。

再者,記憶體晶片可以相互堆疊,使得晶片在垂直面上能實現小面積仍具備高電容。這些晶片具有大量的矽穿孔,連結記憶體堆內的各個晶片,以及其底部的邏輯晶片。而該邏輯晶片也會連結到中介層上的寬匯流排,使得記憶體晶片和GPU之間具備高頻寬。事實上,該匯流排寬度充足,所以記憶體晶片的I/O時脈可以降至低頻。而降頻加上連接至GPU的導線長度極短,這兩個特點就能在使用HBM時將每位元的能耗大幅降低(大約三倍)。

| 圖一 : GDDR5和HBM的比較。(source:graphicscardhub.com) |

|

| 圖二 : HBM的晶片垂直面示意圖(source:widipedia.org) |

|

下表顯示了不同代HBM的重點規格。目前來說,HBM2仍在供應中。有趣的是,三星去(2019)年發佈了新款HBM2e記憶體,該產品跳脫常見規格,單位晶片具備更高電容(16Gb),並進一步提高資料傳輸率至每堆疊410GB/s。

HMC

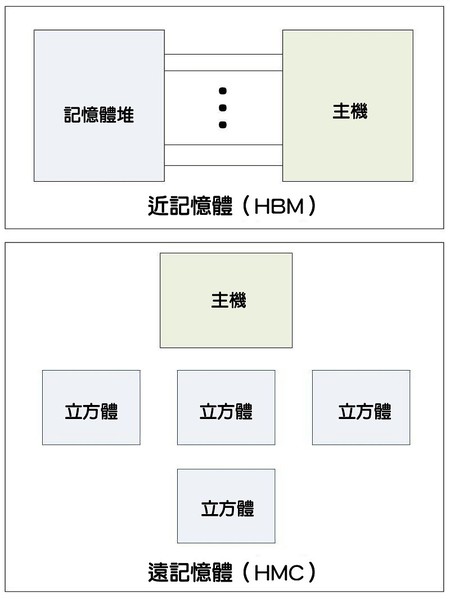

儘管美光不再努力開發HMC標準,我們還是想要稍微介紹一下。HMC是常規DDR記憶體的3D版,特別鎖定用在未來的伺服器上,雖然這個看法以往在業界並不總是很明確。HBM聚焦在頻寬上,因此需要進行高度整合,犧牲電容和晶片擴展性。這就是所謂的「近記憶體(near memory)」。

HMC的重點則在電容,以及將更多記憶體堆輕鬆整合至伺服器內,就像運用閒置插槽來將更多DDR記憶體安裝至主機板一樣。這種方式能提供鬆弛整合,滿足整體系統記憶體要實現高電容的需求。而這通常被稱作「遠記憶體(far memory)」。

| 圖四 : 近記憶體與遠記憶體的比較。(source:eejournal.com) |

|

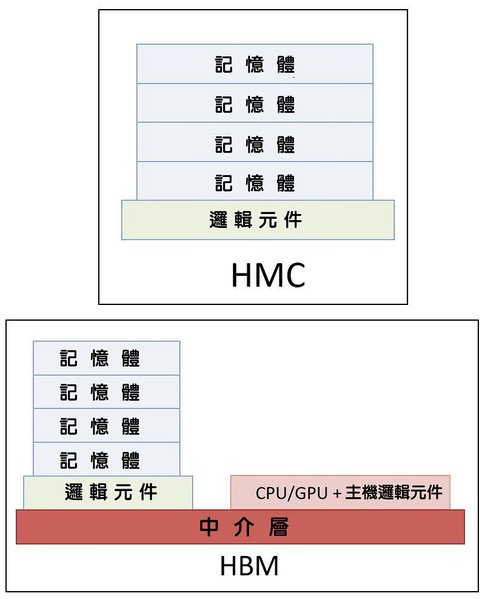

除了這點雷同之外,HMC是與DDR最不相同的記憶體標準,差異比其他任何在本文提到的標準都還大。HMC不使用DDR的匯流排傳輸方式,而是使用記憶體封包,這些封包以高速SerDes鏈接在處理器與記憶體立方體之間傳遞。如此就可能形成菊鏈立方體,以有限的內連導線達到更高電容。

此外,記憶體控制器完全整合在每個立方體的底座晶片,而不像DDR把控制器放在CPU晶片上,也不像HBM那樣分置在GPU和記憶體堆上。

| 圖五 : 比較HMC與HBM結構的示意圖(source:eejournal.com) |

|

Wide I/O

Wide I/O是LPDDR記憶體的3D對應版本,優先採用極端的整合方式來實現可能的最低功耗。這類記憶體應該要直接整合在SoC上方,透過矽穿孔直接連至CPU晶片。如此就能將內連導線變得極短,其所需功耗是所有標準中最低的。

此外,Wide I/O還可能具備極寬的匯流排,端視矽穿孔的密度與尺寸而定。然而,這種極端的整合也要求在SoC內導入矽穿孔,這就會佔去大片寶貴的邏輯晶片面積,因此成本極為高昂。這大概也是為什麼我們還未見過任何採用該技術的商用產品。或許有趣的是,第一代Wide I/O標準採用了軟體定義無線電(SDR)介面,但第二代標準改用DDR介面。

總結各類DRAM的特點

我們已經呈現了不同DRAM類型在設計本質上曾做出或將來會做出的一些必要取捨。每種標準最終都採用相同的概念來改善每一代版本的頻寬,相關技術例如包含更大的預取緩衝區、記憶體分組、通道分裂、差分時脈、指令匯流排優化,以及更新優化(refresh optimization)。

不同標準不過是擁有各自的發展重點,不論是聚焦電容和彈性整合(DDR和HMC),或最低功耗(LPDDR和Wide I/O),還是最高頻寬(GDDR和HBM)。看到3D技術帶給這幾個目標市場的優勢,其實頗富趣味。

將記憶體進行緊密的3D整合,是能提升頻寬的有效方式,但基本上還是會限制電容。首先,放在靠近運算單元的記憶體堆是有數量限制的,再者,每一堆疊能容納的記憶體晶片數量也有限。

未來我們也將會明白,單一DRAM晶片的儲存格數已經逼近極限了。隨著各式應用對資料量的需求增長,在面對記憶體與處理器之間出現頻寬落差的「記憶體牆(memory wall)」問題時,記憶體密度也成為一個更重要的考量點。

DRAM的未來展望:愛美科觀點

為了將DRAM技術推升至其最終極限,並解決記憶體牆的技術問題,愛美科探索了兩條可能的發展道路。這兩條發展途徑採用了完全迥異的技術,將需要全新的架構標準來促使下一代DRAM記憶體的誕生。

第一條發展途徑是提升DRAM位元格的動態性(dynamic nature)。如本文開頭所述,儲存在DRAM位元格電容內的電荷會緩慢流失。因此,DRAM需要被更新。每列通常64毫秒更新一次。這會增加性能與功耗的常態性負擔(overhead)。

採用鐵電材料的電容設計(ferro capacitor)就是一個頗富潛力的辦法,它能讓DRAM位元格儲存電荷的時間延長,這也有助於減緩選擇電晶體(select transistor)對關閉電流的嚴苛要求。此外,鐵電電容能改善DRAM的資料保存時間(retention time),這也帶來諸多益處,例如可忽略更新的負擔、快速開啟或關閉低功耗模式、實現更低的備用功耗,以及進一步推動DRAM的規模化。

在愛美科的鐵電研究計畫中,他們正在開發以鐵電材料為基礎的金屬—絕緣體—金屬(metal-insulator-metal;MIM)電容器,以探索提升DRAM動態性的途徑。為了有效發揮這項技術以達到最低功耗,就需要一套聚焦在這些非揮發特性的全新DRAM架構標準。

然而,要延續DRAM的規模化藍圖以開發出更多代的版本,上述的發展途徑可能並不是最佳選項。因為規模化的問題,晶片密度已開始在約8~16GB的範圍達到飽和,要將DRAM晶片的電容擴充至32GB以上變得相當困難。如果我們想要繼續邁向規模化,將需要更具破壞性的創新技術。

其中一個辦法是以低漏電流沉積的薄膜電晶體(thin-film transistor;TFT),像是氧化銦鎵鋅(indium-gallium-zinc-oxide;IGZO),來取代DRAM位元格內的矽基電晶體。這種材料的寬能隙能確保DRAM具備低關閉電流—這是DRAM儲存單元電晶體的必要特性。由於我們不再需要材料矽來製造儲存單元電晶體,現在就可以將DRAM儲存單元的周邊電路移至DRAM陣列下方。如此,儲存單元的面積就能大幅降低。

下一步我們會考慮堆疊DRAM儲存單元。儲存電荷所需的電容已經達到規模化的極限,但要是我們能用極小的電容來儲存電荷呢?甚至完全不用電容,又會怎樣呢?

IGZO電晶體具備的超低漏電流就有可能開啟一條全新道路,能夠建立不須電容的DRAM儲存單元。由於電容不再,加上IGZO電晶體所用之材料能與後段製程相容,甚至有機會採用可規模化的製程,將不同儲存單元垂直堆疊。這帶來許多好處,但也帶給不同抽象層各式挑戰,例如製程、技術、位元格設計、記憶電路設計與系統架構。

為了解決這些挑戰,愛美科正在思考可能的跨層解決方案,用於未來的高性能DRAM標準,可能提供方法將DRAM記憶體進一步規模化,遠遠超過目前所預期的極限。

(本文由愛美科授權刊登;作者Timon Evenblij(1)、Gouri Sankar Kar(2)為愛美科(1)系統記憶體架構師、(2)SCM/DRAM/MRAM等研究計畫的主持人;編譯/吳雅婷)

**刊頭圖(source:einfochips.com)