信息时代对数据的渴求,推动了数字汇整的发展。Triple-play、医学影像、图像处理、国防、航天、安全、以及加密,都需要更高效能的数字讯号处理(DSP)功能,让传统的解决方案、技术、以及技巧面临严苛的考验。

想了解这种情况,您仅需要研究技术发展,以及面临日趋复杂的算法令既有的解决方案相形见绌的现象。图一显示Shannon的极限点,也就是通讯频道在一定噪声值下,理论上最大的传输率上限。如图一所示,传统的通用处理器(GPP)与DSP解决方案,无法有效达到这个极限。

| 《图一 各时段所需的数字讯号处理效能》 - BigPic:571x306 |

|

其他替代方案是运用FPGA技术来建置讯号处理演算功能,让效能超越传统的解决方案。Xilinx Virtex-5 SXT系列组件就是针对这种FPGA替代方案量身设计,提供独特的资源比例,有效支持最高效能的数字讯号处理功能。

传统DSP 与FPGA DSP

把最复杂的DSP演算流程拆解成各个原子元素,就会得到乘法器、加法器、以及一些延迟元素。结合这些原子组件,就能建置出最复杂的DSP演算功能。

传统的DSP解决方案结合序列控制逻辑,以及许多算术逻辑单元(ALU)。ALU不仅提供加乘功能,序列控制逻辑组件还支持数据码转译与控制功能。传输带宽取决于系统的频率,以及平行处理ALU单元的数量。一个基础频率2 GHz的解决方案,以及ALU可并行操作的数量。一个以2GHz基础频率平行处理8个ALU的解决方案,可提供16 GMAC(每秒160亿次加乘运算)的DSP带宽。

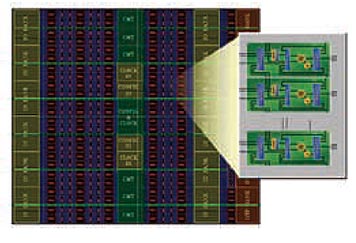

FPGA系列组件透过可编程的逻辑或一个硬式嵌入式处理器来提供用户定义的控制功能。决定效能的主要因素,是提供加乘功能,如图二所示的DSP slice变量。宽带则是由DSP slice的基础频率以及数量来决定。频率高达550 MHz的Virtex-5 SXT组件,搭配640 DSP slice,可提供352 GMAC的DSP带宽。Virtex-5 SXT解决方案在一定频率下,提供多出40倍的DSP资源,超越大多数传统的先进DSP解决方案。

| 《图二 Virtex-5 SX95T FPGA与DSP48E slice栏》 |

|

Virtex-5 SXT提供高效能DSP解决方案

让Virtex-5 SXT FPGA能达成更高DSP带宽的关键,在于设计完整架构的解决方案,可支持550 MHz的效能,并运用专属资源来降低系统瓶颈。建置这种完整解决方案的关键,包括以下重点:

- ●DSP48E运用一种收敛式建置技巧,在Virtex-5组件中,使用存在于每个slice中相同的互连组件,让每组640个自给自足的DSP48E slice能够独立运作,或是组合后再运作,如图三所示。

- ●Virtex-5组件内的DSP48E单元已针对65奈米几何制程进行优化,而且Arithmetica提供先进的MathIP,以达最大效能。

- ●整体系统:DSP48E单元、处理器系统、可编程逻辑、以及内存。这些都能运用一个大于550MHz的外部系统频率,一起搭配运作。系统效能可统筹规划、可控制的、而且是可维持的。

| 《图三 单一DSP48E slice》 - BigPic:705x405 |

|

运用Virtex-5 SXT 解决方案

业者必须在传统DSP解决方案以及运用Virtex-5 SXT FPGA的系统之间做出取舍。传统的DSP运用一个发展完善的基础程序代码,在序列控制逻辑组件或处理器上执行。这个解决方案能重复使用现有的程序代码,并提供一个容易使用的可编程模型。

FPGA提供更高的单芯片效能,不仅具备弹性且可扩充的特色,还需要运用一组新工具或FPGA设计技巧来建置。根据所需的应用和所需要效能,或是解决方案的历史,可选出较理想的解决方案。通常组合式解决方案是较佳的选择。为了说明各种可能的建置模式,我们来看下面三个不同的挑战、可行的解决方案以及这些解决方案的优势:

范例1:旧型系统运用整个算法函式库与建置技巧,却无法达到效能目标。

范例1的计划:找出DSP的效能瓶颈,并把这部份的设计建置在Virtex-5 SXT FPGA组件中。加快设计并达到所需的效能。

范例1的优势:这个解决方案让工程师能维持旧程序代码,达到弹性、容易使用、以及兼容的目标,同时还能提高系统效能。其中一个较小的Virtex-5 SXT组件,适合用来加速传统的DSP支持协同处理或前置处理功能。传统DSP解决方案与Virtex-5 SXT组件之间的通讯,可利用SelectIO技术,或运用GTP高速序列收发器来执行。根据设计的复杂度与建置在FPGA的算法,可运用外部的技术资源来进行建置作业。

下个范例为需要大幅增加的处理效能。

范例2:效能方面的需求,促使业者必须采用全新的建置方案来,达到更高的效能。

范例2的计划:把整个设计重新建置到一个更大的Virtex-5 SXT组件内。运用可编程逻辑、I/O、以及内部block RAM来建置相对应的控制功能。运用DSP slice来建置速度更高的DSP算法,并发挥收敛架构提供的大量平行设计方法。运用System Generator for DSP或是赛灵思提供的AccelDSP合成工具,来克服新设计方法的挑战。

范例2的优势:运用单芯片解决方案,来达到高出数个等级的效能。相较于使用多个DSP芯片来进行建置的传统解决方案,此范例可协助降低电路板空间与材料列表成本(如图4所示)。

| 《图四 比较运用多重DSP芯片与单一FPGA DSP解决方案之效能》 - BigPic:865x410 |

|

最后范例是关于重新设计现有的FPGA系统,以达到更高效能的DSP:

范例3:除了标准FPGA建置方案外,可运用任何Virtex-5 FPGA中的DSP slice,来建构高效能的DSP算法。当您需要更多的DSP资源时,可改用针脚兼容的Virtex-5 FPGA平台。

范例3的计划:重新设计现有的建置方案,且运用Virtex-5 SXT组件的DSP资源、参考设计方案、以及设计技巧。

范例3的优势:更高的效能以及一个整合型解决方案,运用Virtex-5 FPGA组件与平台包含的DSP slice,来充分发挥扩充性与平行处理功能。

虽然Virtex-5 FPGA系列内的DSP slice能开发出高速且弹性化的数字处理建置方案,但您还是必须将整体解决方案一并纳入考虑。高速数据处理需要的不只是高效能DSP,更需要高速输入、输出、以及储存数据与系数的内存效能。

Virtex-5 SXT是唯一结合高速multi-Gigabit序列收发器的FPGA组件,以串流模式把数据输入与输出到FPGA组件中,加上独特的block RAM与分布式RAM比例,适合用来储存采样数据与系数。最后,SelectIO界面搭配ChipSync技术,打造出易于使用且高效率的内存界面,能用来简化印刷电路板的配置。运用这个方案以及一个弹性化的可编程技术,能针对持续变迁的标准进行调整,而更短的设计时间,则可因应严苛的上市时程目标以及实时上市要求。

在降低成本方面,Virtex-5 SXT系列组件提供一个EasyPath程序,可降低高达40%的成本,而不会损耗DSP48E slice或multi-Gigabit收发器(MGT)的使用。

结论

在降低成本方面,Virtex-5 SXT系列组件提供一个EasyPath程序,可降低高达40%的成本,而不会损耗DSP48E slice或multi-Gigabit收发器(MGT)的使用。

<作者为赛灵思公司先进产品部门产品经理>