新一代的高效能系統正面臨資料傳輸的頻寬限制,也就是記憶體撞牆的問題,運用電子設計自動化與3D製程技術,愛美科證實3D SoC設計能大幅提升性能並降低功耗,成為備受矚目的異質整合解決方案。

展望高效能應用 加速開發3D SoC設計

資料密集的高效能系統用於先進運算、伺服器或深度學習應用,然而,現在卻面臨著所謂的「記憶體撞牆(memory wall)」問題,而且這項挑戰日益嚴峻,資料存取速度難以突破瓶頸。為了推倒這面高牆,3D系統單晶片(SoC)整合技術備受矚目。利用這套異質整合方法,晶片系統能自動分割為多個獨立晶片,並實現這些晶片的3D同步設計與互連(interconnect)。

在2021年IEEE國際電子元件會議(IEDM)上,愛美科的研究團隊發表了兩篇3D SoC與晶背互連技術的論文,其中一篇列舉了3D SoC這項設計概念的技術優勢,目標要實現多晶片的異質系統整合,超越時下炙手可熱的小晶片(chiplet)設計。

愛美科資深研究員,同時也是3D系統整合研究計畫的研發副主任Eric Beyne表示:「小晶片概念涉及了多個小晶片的獨立設計與製造,著名的例子就是高頻寬記憶體(HBM),它把多個DRAM晶片堆疊起來,接著透過介面匯流排,把堆疊連接到處理器晶片,因此在應用上必須容忍一定的延遲時間。有鑑於此,小晶片設計永遠無法在邏輯單元與一級和二級快取記憶體之間實現快速存取。」

3D SoC整合技術採用直接連接且距離更短的互連導線來進行記憶體與邏輯單元的分割,最終能顯著改善傳輸性能。在論文中,愛美科團隊展示了一項經過優化的3D SoC設計,將記憶體巨集(memory macro)置於最上層晶片,其餘邏輯單元則在底層,其運作頻率與2D設計相比,提高了40%。

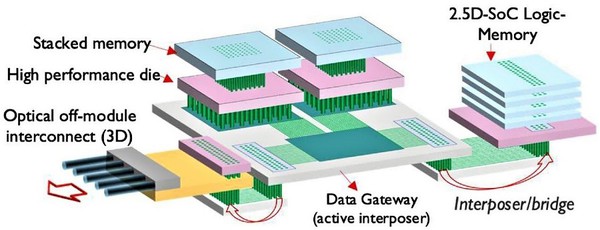

| 圖一 : 愛美科於2021 IEDM展示的未來高效能系統抽象視圖:高效能晶片與3D SoC記憶體堆疊佈建於主動式中介層上方,並將中介層作為閘道,以2.5D的方式連接到局部HBM和光學收發器模組。 |

|

為了實現全功能化的3D SoC,關鍵的技術挑戰也納入了討論。愛美科主任研究員,也是布魯塞爾自由大學教授的Dragomir Milojevic指出:「從設計面來看,在進行邏輯單元和記憶體的分割時,都要採取3D SoC協同設計的策略。這就會用到專屬的電子設計自動化(EDA)工具,才能同時顧及兩方的設計,並在佈局與佈線時,利用自動化工具完成系統分割與3D關鍵路徑優化。透過與益華電腦(Cadence)合作,我們已經取得這些先進工具。」

他接著分享,在技術層面,晶圓對晶圓的異質接合解決方案將會持續發展,進一步提升晶片之間的互連導線密度,這對一級和二級快取分割來說是必要技術。

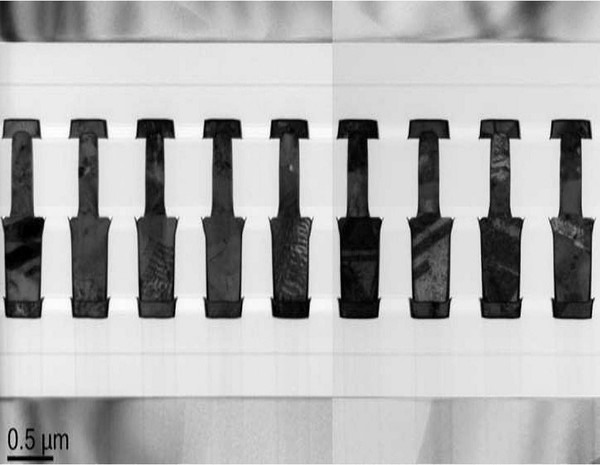

| 圖二 : 愛美科於2021 IEDM展示間距為700nm的晶圓對晶圓異質接合技術。 |

|

下一步計畫:開發晶背

高效能3D SoC的系統分割可能會將部分或全部的記憶體巨集佈建在最上層晶片,邏輯單元則置於最下層。在技術上要做到這點,可以將放置邏輯單元的晶圓主動側正面,以低溫晶圓對晶圓的接合技術,鏈結到記憶體所在的晶圓主動側正面。在這種配置下,原本的兩面晶背會變成3D SoC系統的外側。

Eric Beyne點明:「現在我們可以考慮利用這些『空出來的』晶背,用於訊號繞線,或是直接供電給邏輯單元晶圓上的電晶體。傳統製程通常把繞線和電源供應設計在晶圓正面,所以在處理複雜互連導線的後段製程中,必須努力爭取空間,而晶背在這類設計中僅僅作為封裝用的晶片載體。」

他進一步說明,2019年Arm的模擬結果首次證明在CPU設計中導入晶背電源供應網路(power delivery network;PDN)所帶來的正面效益。該CPU設計採用愛美科開發的3nm製程,位於薄型化晶背的互連導線連接到晶圓正面的3nm電晶體,兩者透過落在埋入式電源軌(buried power rail;BPR)結構上的矽穿孔(through silicon via;TSV)相連。根據模擬結果,晶背PDN的傳輸效率比傳統的正面PDN還高出7倍。

因此,可以預期在記憶體與邏輯單元堆疊(memory-on-logic)的3D SoC應用上,運用晶背PDN來供電給位於底層且功耗較大的核心邏輯電路,將能額外加強性能。甚至還能設計替代的3D SoC系統分割方案,把像是一級快取SRAM等的部分記憶體晶片置於底部,從晶背實現電源供應。

晶背PDN除了擴展3D SoC設計的潛能,還曾被提議可用於積層型單晶片邏輯與SRAM的SoC應用,協助達成元件與晶片的進一步微縮。愛美科3D系統整合研究計畫負責人Geert Van der Plas說道:「研究結果顯示,將電源供應網路轉移到晶圓背面是個有趣的解決方案,不僅能用來面對後段製程的佈線壅塞挑戰,還能減低壓降。」

「3D SoC方案的主要差別是將一片虛擬晶圓接合到目標晶圓,以利進行晶背研磨和金屬化。」他進一步解釋。愛美科的合作夥伴近期就宣布在其中一款先進製程晶片中採用這種晶背PDN設計。

晶背互連技術 讓性能再升級

晶背PDN的技術優勢已在特定設計中獲得驗證,而善用晶背的其它效益還可望在全域訊號繞線的應用上浮現。愛美科已聯手益華電腦,針對在晶背進行部分繞線的SRAM巨集與邏輯電路設計,首次進行評估與優化。SRAM巨集不僅與記憶體單元陣列有關,還包含位址解碼器、控制單元等與處理器設計相關的周邊電路。

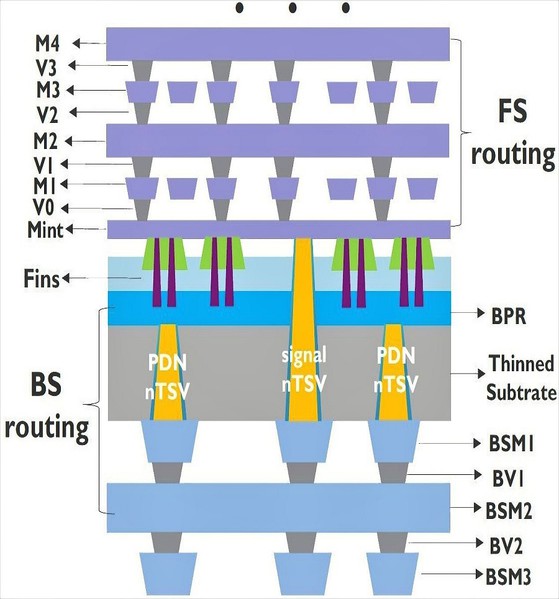

| 圖三 : 愛美科於2021 IEDM展示傳統製程的晶圓正面後段製程、背面PDN和訊號佈線。其中,晶背利用奈米矽穿孔(nano-TSV;nTSV)將導線向外連接,包含連至BPR的PDN佈線,以及連至晶圓正面導線的訊號佈線。 |

|

SRAM巨集和邏輯單元的訊號繞線最多需要3層晶背金屬層,而奈米矽穿孔負責將晶背導線連接至晶圓正面。SRAM巨集的設計導入了2nm奈米片電晶體,而且只有用於周邊電路的全域繞線會與晶背導線相連。邏輯單元則運用環形振盪結構來評估利用晶背進行訊號繞線所帶來的影響,邏輯標準單元也採用2nm製程的叉型片。實體佈局方面,愛美科選用了同樣以2nm叉型片製程設計套件(PDK)製成的64位元Arm CPU,以確保環形振盪器的模擬結果能夠發揮作用。

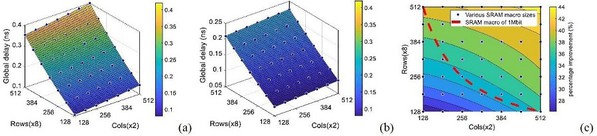

Geert Van der Plas解釋:「根據研究,與正面佈線相較,晶背佈線在改善長距離訊號繞線的延遲和功耗上,出乎意料地表現突出。我們成功展示了SRAM巨集的性能最高能提升44%,功耗最多降低30%,邏輯單元的傳輸則能加速至2.5倍,功耗效率增加60%。」

| 圖四 : SRAM巨集在不同列行設計下的全域佈線讀取延遲時間:(a)晶圓正面(b)背面(c)從正面至背面的延遲差距。巨集大小涵蓋128*128*16=256kbit~512*512*16=4Mbit。 |

|

為了評估這些電路的性能與功耗,愛美科進行了多項實驗並建立模型。Dragomir Milojevic指出:「實驗涉及了奈米矽穿孔製程在電容與電阻方面的優化,以確保晶圓正面與背面的導線之間能夠維持良好的電氣連接。這些參數也被饋入模型以進行模擬。最後我們採用設計—技術偕同最佳化(design-technology co-optimization)策略驅動的佈線優化技術,可望在未來持續精進。」成果顯示,透過降低晶背導線的電容,性能可再提升20%。

結語

這套異質3D SoC方案透過改良系統架構設計與3D整合技術來實現,經證實,是可以有效提升系統性能的可行方法。利用底層晶背進行電源傳輸或訊號繞線,還能達到其它效能提升。愛美科首度展示了在SRAM巨集與邏輯電路導入晶背互連技術的正面效果。這些晶背導線還能為高效能3D SoC與積層型單晶片SoC實現性能升級。

(本文由愛美科授權刊登;作者為Dragomir Milojevic1、Geert Van der Plas2和Eric Beyne3為愛美科1主任研究員、23D系統整合研究計畫主持人、33D系統整合計畫研發副主任;編譯/吳雅婷)