資訊時代對資料的渴求,推動了數位匯整的發展。Triple-play、醫學影像、影像處理、國防、航太、安全、以及加密,都需要更高效能的數位訊號處理(DSP)功能,讓傳統的解決方案、技術、以及技巧面臨嚴苛的考驗。

想瞭解這種情況,您僅需要研究技術發展,以及面臨日趨複雜的演算法令既有的解決方案相形見絀的現象。圖一顯示Shannon的極限點,也就是通訊頻道在一定雜訊值下,理論上最大的傳輸率上限。如圖一所示,傳統的通用處理器(GPP)與DSP解決方案,無法有效達到這個極限。

| 《圖一 各時段所需的數位訊號處理效能》 - BigPic:571x306 |

|

其他替代方案是運用FPGA技術來建置訊號處理演算功能,讓效能超越傳統的解決方案。Xilinx Virtex-5 SXT系列元件就是針對這種FPGA替代方案量身設計,提供獨特的資源比例,有效支援最高效能的數位訊號處理功能。

傳統DSP 與FPGA DSP

把最複雜的DSP演算流程拆解成各個原子元素,就會得到乘法器、加法器、以及一些延遲元素。結合這些原子元件,就能建置出最複雜的DSP演算功能。

傳統的DSP解決方案結合序列控制邏輯,以及許多算術邏輯單元(ALU)。ALU不僅提供加乘功能,序列控制邏輯元件還支援資料碼轉譯與控制功能。傳輸頻寬取決於系統的頻率,以及平行處理ALU單元的數量。一個基礎頻率2 GHz的解決方案,以及ALU可平行作業的數量。一個以2GHz基礎頻率平行處理8個ALU的解決方案,可提供16 GMAC(每秒160億次加乘運算)的DSP頻寬。

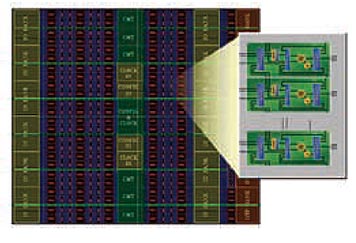

FPGA系列元件透過可編程的邏輯或一個硬式嵌入式處理器來提供使用者定義的控制功能。決定效能的主要因素,是提供加乘功能,如圖二所示的DSP slice變數。寬頻則是由DSP slice的基礎頻率以及數量來決定。頻率高達550 MHz的Virtex-5 SXT元件,搭配640 DSP slice,可提供352 GMAC的DSP頻寬。Virtex-5 SXT解決方案在一定頻率下,提供多出40倍的DSP資源,超越大多數傳統的先進DSP解決方案。

| 《圖二 Virtex-5 SX95T FPGA與DSP48E slice欄》 |

|

Virtex-5 SXT提供高效能DSP解決方案

讓Virtex-5 SXT FPGA能達成更高DSP頻寬的關鍵,在於設計完整架構的解決方案,可支援550 MHz的效能,並運用專屬資源來降低系統瓶頸。建置這種完整解決方案的關鍵,包括以下重點:

- ●DSP48E運用一種收斂式建置技巧,在Virtex-5元件中,使用存在於每個slice中相同的互連元件,讓每組640個自給自足的DSP48E slice能夠獨立運作,或是組合後再運作,如圖三所示。

- ●Virtex-5元件內的DSP48E單元已針對65奈米幾何製程進行最佳化,而且Arithmetica提供先進的MathIP,以達最大效能。

- ●整體系統:DSP48E單元、處理器系統、可編程邏輯、以及記憶體。這些都能運用一個大於550MHz的外部系統時脈,一起搭配運作。系統效能可統籌規劃、可控制的、而且是可維持的。

| 《圖三 單一DSP48E slice》 - BigPic:705x405 |

|

運用Virtex-5 SXT 解決方案

業者必須在傳統DSP解決方案以及運用Virtex-5 SXT FPGA的系統之間做出取捨。傳統的DSP運用一個發展完善的基礎程式碼,在序列控制邏輯元件或處理器上執行。這個解決方案能重複使用現有的程式碼,並提供一個容易使用的可編程模型。

FPGA提供更高的單晶片效能,不僅具備彈性且可擴充的特色,還需要運用一組新工具或FPGA設計技巧來建置。根據所需的應用和所需要效能,或是解決方案的歷史,可選出較理想的解決方案。通常組合式解決方案是較佳的選擇。為了說明各種可能的建置模式,我們來看下面三個不同的挑戰、可行的解決方案以及這些解決方案的優勢:

範例1:舊型系統運用整個演算法函式庫與建置技巧,卻無法達到效能目標。

範例1的計畫:找出DSP的效能瓶頸,並把這部份的設計建置在Virtex-5 SXT FPGA元件中。加快設計並達到所需的效能。

範例1的優勢:這個解決方案讓工程師能維持舊程式碼,達到彈性、容易使用、以及相容的目標,同時還能提高系統效能。其中一個較小的Virtex-5 SXT元件,適合用來加速傳統的DSP支援協同處理或前置處理功能。傳統DSP解決方案與Virtex-5 SXT元件之間的通訊,可利用SelectIO技術,或運用GTP高速序列收發器來執行。根據設計的複雜度與建置在FPGA的演算法,可運用外部的技術資源來進行建置作業。

下個範例為需要大幅增加的處理效能。

範例2:效能方面的需求,促使業者必須採用全新的建置方案來,達到更高的效能。

範例2的計畫:把整個設計重新建置到一個更大的Virtex-5 SXT元件內。運用可編程邏輯、I/O、以及內部block RAM來建置相對應的控制功能。運用DSP slice來建置速度更高的DSP演算法,並發揮收斂架構提供的大量平行設計方法。運用System Generator for DSP或是賽靈思提供的AccelDSP合成工具,來克服新設計方法的挑戰。

範例2的優勢:運用單晶片解決方案,來達到高出數個等級的效能。相較於使用多個DSP晶片來進行建置的傳統解決方案,此範例可協助降低電路板空間與材料清單成本(如圖4所示)。

| 《圖四 比較運用多重DSP晶片與單一FPGA DSP解決方案之效能》 - BigPic:865x410 |

|

最後範例是關於重新設計現有的FPGA系統,以達到更高效能的DSP:

範例3:除了標準FPGA建置方案外,可運用任何Virtex-5 FPGA中的DSP slice,來建構高效能的DSP演算法。當您需要更多的DSP資源時,可改用針腳相容的Virtex-5 FPGA平台。

範例3的計畫:重新設計現有的建置方案,且運用Virtex-5 SXT元件的DSP資源、參考設計方案、以及設計技巧。

範例3的優勢:更高的效能以及一個整合型解決方案,運用Virtex-5 FPGA元件與平台包含的DSP slice,來充分發揮擴充性與平行處理功能。

雖然Virtex-5 FPGA系列內的DSP slice能開發出高速且彈性化的數位處理建置方案,但您還是必須將整體解決方案一併納入考量。高速資料處理需要的不只是高效能DSP,更需要高速輸入、輸出、以及儲存資料與係數的記憶體效能。

Virtex-5 SXT是唯一結合高速multi-Gigabit序列收發器的FPGA元件,以串流模式把資料輸入與輸出到FPGA元件中,加上獨特的block RAM與分散式RAM比例,適合用來儲存採樣資料與係數。最後,SelectIO界面搭配ChipSync技術,打造出易於使用且高效率的記憶體界面,能用來簡化印刷電路板的配置。運用這個方案以及一個彈性化的可編程技術,能針對持續變遷的標準進行調整,而更短的設計時間,則可因應嚴苛的上市時程目標以及即時上市要求。

在降低成本方面,Virtex-5 SXT系列元件提供一個EasyPath程式,可降低高達40%的成本,而不會損耗DSP48E slice或multi-Gigabit收發器(MGT)的使用。

結論

數位匯流讓數位訊號處理效能,超越了傳統解決方案的能力極限,促使業者轉而使用FPGA解決方案。不論是加速傳統DSP解決方案,運用新型高效能設計,或是重新檢討目前運用的FPGA,賽靈思都有最適合的技術、工具、IP、以及參考設計方案,協助您達成任何嚴峻的目標。

<作者為賽靈思公司先進產品部門產品經理>