毫無疑問的,資訊產業正積極於消費性電子化,Comdex Fall(國際電腦展)式微,業者將心力焦點轉向CES(消費性電子展),Dell(戴爾)也開始販售LCD TV(液晶電視),甚至Apple(蘋果)改名去掉「Computer」一字等,都是此趨的例證。

資訊產品朝CE化發展,連帶的過去在資訊領域的晶片設計業者也必須因應風氣,設計出更切合消費性需求及市場的晶片,不過這對晶片業者可說是一大挑戰,因為消費性電子領域有別於資訊產業,CE市場變化快速、產品少量多樣、產品生命週期短、價格低廉,相對的,過去的資訊產品變化較緩、多量少樣、生命週期長、價格較高,雖說兩種產業都根基於半導體/電子工程技術,但特性取向卻是天差地別。

更簡單地說,晶片設計業者必須能提供應用業者更低廉的晶片、更快速提供切合需求與應用的晶片、以及能更靈活彈性運用的晶片,重點就在「成本、速度、彈性」等三項表現,而晶片業者如何因應與滿足更高標的要求,本文以下將對此進行更多的討論。

OTP(一次性燒錄)

許多簡單的消費性電子內都會使用微控制器(Microcontroller,簡稱uC),多數微控器的內部具有程式記憶體,記憶體內存放著應用設計者的控制程式,並搭配上微控器外部的控制電路,以此來實現一項應用產品。

重點就在於控制程式,由於CE產品少量多樣、市場變化快速且講究低價,控制程式若是要以Mask ROM的型態放入uC內必須建立光罩,而建立時間須等上數十天,且光罩成本高昂(視製程而定,先進製程達上百萬美元之譜),必須有足夠的量產規模才足以均攤光罩成本,同時光罩缺乏彈性,倘若程式驗證不足而出現錯誤,或需要調修改版等,都必須重新建立光罩,並再次等待數十天、再次支付百千萬以上的光罩花費。

很明顯的,Mask ROM作法的漫長等待與CE市場的快速、及時上市相左,最低量產規模的要求也與小量需求相違背,而不能再變動的程式內容也無法滿足多樣性的需求。

如果不用Mask ROM,而使用可進行多次燒錄的EEPROM、Flash Memory記憶體,如此雖然可讓uC具有修改彈性,且不用等待數十日的時間,但卻有成本增加的麻煩,所以可重複燒錄的EEPROM/Flash Memory型uC多用於前期驗證試製,或做為投入市場的先期嘗試,或用來滿足少量的個別專案,但仍難以用於CE的主流市場。

| 《圖一 OTP型微控器即是將原有透光窗式的EPROM型微控器,改以非透光的傳統封裝而成,由於剛出廠的晶片內是全新未用的EPROM,因此仍可進行一次程式燒錄,之後無法將資料清除,圖為傳統使用透光窗封裝的微控器:8749(2KB EPROM型的8048微控器)。》 |

|

真正更適合CE市場的作法是OTP(One-Time Programmable)的一次性燒錄,OTP是用EPROM記憶體,EPROM特性上允許多次燒錄,但需要紫外光的照射以清除原有已寫入的程式才能進行令一次的寫入,而為了讓紫外光能照到EPROM表面必須使用具有透光窗的晶片封裝,且此種封裝成本較高,而OTP方式是將EPROM以不透光的方式進行封裝,如此剛出廠的EPROM仍是空白未曾寫入過,仍可寫入一次程式。

OTP型的uC在寫入次數上不如EEPROM型、Flash型,但在價格上卻更低廉,同時也不用等待光罩建立時日與受限於最低量產需求等,是最兼顧「成本、速度、彈性」的選擇。

如果各位難以體會箇中特性,或許也可用今日的光碟片來比喻,店頭所賣的音樂光碟、影片光碟是在出廠前就已決定內容,無法再改變內容,這如同Mask ROM,而CD-R、DVD-R/+R等可以燒錄一次的光碟則類似OTP,至於可重複燒錄的即是CD-RW、DVD-RW/+RW/RAM,很明顯的目前用量最大的是CD-R、DVD-R/+R,因為彈性勝過工廠壓製的光碟,同時成本低於可重複燒錄的光碟,CD-R、DVD-R/+R的成功原因與OTP相同。

FPGA(現場可程式化邏輯陣列)

與ASIC相較FPGA具有靈活改變電路組態的特點,然相對的它的電路面積利用率較低(意味著成本較高、功效較高)、電路執行速度較慢等,使的FPGA過去很長一段時間只適合用在一些特殊運用,例如特定的專案、大幅且頻繁改變電路設計的應用、ASIC設計完工後的試製驗證等,除此之外沒有太多的應用,也很少用於消費性電子領域。

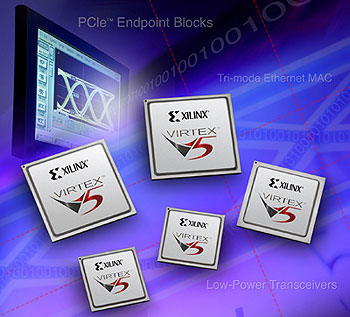

不過,就特性表現而言,FPGA滿足彈性修改變化、快速交付生產等要求,只有在成本上較不合CE市場的需求,但是這樣的情形在逐漸在改變,由於光罩成本隨先進製程而不斷增高,許多ASIC晶片產品已無法像過往般用較高的價格或較大的用量來均攤光罩成本,相對的FPGA卻因先進製程而讓價格更加低廉,如此致使許多價格與用量較低的晶片放棄開光罩,而改以FPGA方式量產,改以FPGA方式量產的結果是讓FPGA的用量增加,量價均攤後使FPGA的成本更加低廉,目前為止FPGA仍持續在此一良性循環的路子中發展。

FPGA價格更低廉後,在CE的「成本、速度、彈性」三取向上都能切合,如今正有愈來愈多的晶片設計者及CE產品設計者捨ASIC而就FPGA。

| 《圖二 美國國家半導體公司(National Semiconductor, NS)的COP8SAC家族微控器即有提供一次性燒錄用的EPROM型版本,圖為COP8SAC微控器與迴紋針的尺寸比較。(圖片來源:National.com)》 |

|

Structured ASIC(結構化ASIC)

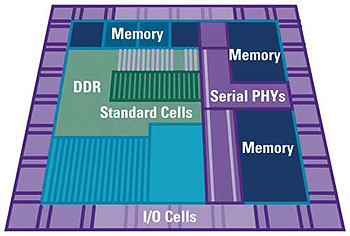

Structured ASIC(也稱Platform ASIC)可說是ASIC業者的一種修正作法,Structured ASIC依然要開設光罩,然光罩的張數減少,在一顆多層電路的晶片上,部分電路層仍使用光罩式的訂製作法,但也有部分電路層改採FPGA的標準制式量產作法,如此使Structured ASIC的各項特性都介於ASIC與FPGA,好處是執行上比FPGA省電、比FPGA快速,缺點則是彈性程度不如FPGA、仍不可免除光罩的花費與時間,只是花費及時間因光罩層數的減少而獲得部分縮減。

| 《圖三 光罩成本不斷高升的結果,使許多中低價位、中低用量的晶片開始改以FPGA型態供貨,圖為賽靈思(Xilinx,過去稱為智霖)公司的FPGA:Virtex-5 LXT家族系列。(圖片來源:Xilinx.com)》 |

|

所以,Structured ASIC是介於ASIC與FPGA間的晶片,對晶片設計者而言等於多一項選擇,針對CE領域中不同的產品與不同的市場風向,適時使用ASIC、FPGA、或Structured ASIC。或許有人認為特性居中的Structured ASIC將如同OTP一樣最具優勢,但目前來看似乎相反,由於Structured ASIC是2001、2002年開始的產物,在開發工具、驗證程序等方面都不如已成熟運用多年的FPGA與ASIC,因此發展空間仍待觀察,最終無論Structured ASIC是否為CE市場接受,短時間都不影響FPGA在CE領域的擴展使用。

| 《圖四 由於先進製程的光罩成本呈指數攀升,使晶片設計業者(在此指無晶圓廠的半導體業者,Fabless)開始尋求其他低廉化量產的方案,「結構化ASIC」即是可選方案之一,圖為AMIS公司的結構化ASIC:XPressArray-II,XPressArray-II使用0.15um製程、1.5V工作電壓,適合取代原屬中等密度、高速執行的ASIC應用。(圖片來源:AMIS.com)》 |

|

IP(矽智財)

消費性電子除了多樣化的特性外,近年來也積極強調多功能,如此也意味著晶片必須整合更多的功效,然更多功效使晶片電路更加複雜,此不單是增加設計心力,包括驗證心力也高度攀升,連帶使晶片的開發時間、心力、成本也攀升。

如果不增加開發人手,那麼開發時間就會增長,使晶片較晚發表並喪失市場獲利先機,然增加人手也會增加成本。

關於此,解決的方式多半是向外尋求矽智財電路,由其他業者提供成熟、已完成驗證、甚至是已經過市場實證考驗的電路,將電路做為新開發設計晶片中的子模塊,以此來加速開發時間、減省驗證程序。

額外一提的是,矽智財電路又概分成兩種型態:軟式與硬式,軟式智財電路只針對邏輯功效等進行描述,而沒有最後真正實製投產的具體電路,反之硬式智財電路則是已完成實製電路的型態。對晶片設計者而言,軟、硬各有其優缺點,軟式具備較大的再修改空間(與硬式相較),且與晶圓製程技術的相依性低(較具換廠、換製程彈性),缺點是需要比硬體更多的設計與驗證心力,相對的硬式的設計與驗證需求少於軟式,但電路再修改的自主性與修改彈性就較低。

就過去而言,晶片業者多半為了自主性與更佳的整合度,因而偏向選擇軟式,不過近年來產品及時上市的時間壓力愈來愈大,自主彈性修改的主張逐漸在降低,並逐漸選擇較無彈性但立即可用的硬式智財電路。

| 《圖五 適當運用矽智財電路可加快晶片的開發時程、減省驗證心力,而近年來晶片及時上市的壓力日增,矽智財的需求也從自主修改性較高的軟式矽智財,逐漸轉向更快速合用的硬式矽智財,圖為ARM公司收併Artisan公司後所推展的週邊矽智財電路示意圖。(圖片來源:ARM.com)》 |

|

Design House(設計代工業者)

除了尋求現成矽智財電路外,如果需要設計的電路功效並沒有現成矽智財合用時,且又有上市時間壓力,是否有其他的加速、省力法?關於此答案是肯定的,那就是尋求設計代工業者的合作。

「設計代工」言下之意是依據客戶的需求來設計電路,之後再將設計完成的電路交付給委託客戶,且代工業者多半要對委託內容保密,完成的設計成果也完全歸委託業者所有,代工完全是不具名的背後工作。

如前所述,當晶片所含括的功效、設計的構面愈來愈大時,晶片設計業者很難完全用自有的技術團隊來完成設計,為了加速開發時間與程序,在使用矽智財電路外,尋求設計代工也是可搭配選用的一種方案。

當然,設計代工業者雖然要對每個委託內容守密,但如果晶片設計業者委託的是新晶片產品中的關鍵性電路,則難保日後代工業者不會將此次委託設計的技術經驗與實務複製運用到其他客戶的委託案中,也因為有這一層顧慮,目前委外設計的電路多半不是關鍵性電路,關鍵部分多半仍是由自有團隊負責。

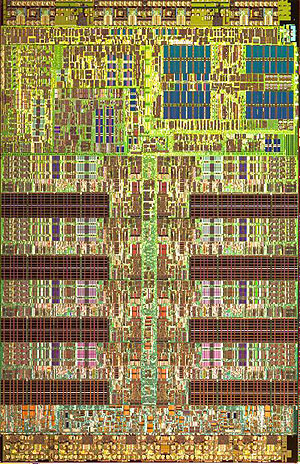

| 《圖六 晶片電路的不斷龐雜化發展,如今已少有單一業者能獨自在時限內完全自主設計,因此逐漸需要借重其他業者的智財電路,以加速整體設計進度並減少驗證心力,圖為IBM、Sony、Toshiba等共同合作研發的Cell 處理器,該處理器就使用上Transmeta公司的LongRun2省電技術功效的智財電路,以及Rambus公司的高速記憶體介面智財:XDR,以及高速I/O介面智財電路:FlexIO。(圖片來源:www-03.ibm.com)》 |

|

多組團隊並行研發

「多組團隊並行研發」的作法事實上也行之有年,甚至在過去的資訊用晶片就有例證,例如Intel的x86 CPU就同時有兩組設計團隊,一組團隊專門從事運算架構的變革,另一組團隊則專注在效能的提升,兩團隊交替推出新的CPU,例如A團隊推出80386、Pentium,B團隊則推出80486(加速型的80386)、Pentium Pro/II(加速型的Pentium)等。

類似的,設計一套晶片組可能需要9個月的時間,但面市之後真正能在市場賣的時間只有6個月,為了解決研發時間長,可賣時間短的問題,同時啟動兩組以上的研發團隊成為不得不的作法。

更多因應CE市場的技術、策略

在上述的各種市場因應策略中,OTP、FPGA、Structured ASIC等是較偏向量產選擇面的策略,而外購IP、委託Design House、多組團隊並行研發等則偏向設計面的策略,除此之外其實還有許多的變通策略,例如在效能與功耗允許下可借重嵌入式軟體來增加晶片的功效彈性,或善用封裝技術來降低設計風險,或運用介面標準來增加變換彈性等,在此無法逐一詳述。

不過,無論是何種因應策略與技術,都仍然必須合乎前述的「成本、速度、彈性」三項要求,在三種取向上獲得最高且最均衡的表現,該項策略與技術才能適用在CE市場中。