??创科技开发了一种新DRAM架构-RPC DRAM技术,提供x16 DDR3 - LP DDR3数据频宽,采仅使用22个开关信号之40引脚FI-WLCSP封装,256 Mb DRAM体积为2 x 4.4 mm,所有40个引脚均采用业界标准之400微米锡球间距安装在周边,使其成为许多可穿戴的影音物联网设备的理想记忆体。

|

| ??创科技新DRAM架构-RPC DRAM技术,提供x16 DDR3 - LP DDR3数据频宽,采仅使用22个开关信号之40引脚FI-WLCSP封装 |

??创指出,新一代的智慧型消费性电子产品皆具备多元功能交互应用,例如智慧通讯、资料影音即时传输等功能,而影音多媒体串流往往由於占据大量频宽及记忆容量,使之成为系统架构瓶颈之一,也是系统设计者面临的最大的挑战之一 。

??创之新型RPC DRAM具备特殊应用(ASIC)记忆体的优点,它采??创RPC DRAM之实体层(Physical Layer,PHY),可有22个开关信号,而输出共有40PHY接合垫;比一般相同频宽之DDR3 PHY,所须的47个开关讯号 (x16 data bus)及达100 PHY接合垫,使用不到一半的接合垫,用在特殊应用之记忆体接囗。

缓冲记忆体常被用於影音多媒体系统中,作为视讯画面播放速率转换、显示缓冲、镜头去扭曲及阴影校正、慢动作缓冲等。最常见的需求是存储一两个视讯帧(即视频速率转换和显示缓冲),其它如慢动作视讯缓冲则较无硬体限制,这样情况下,DDR3 DRAM x16 BGA 封装即可满足其需求。

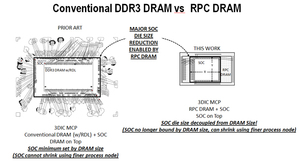

然而,此设计却常会遇到穿戴式装置的物理极限,以眼镜型的影音传输播放系统为例,DDR3所提供数据频宽已足以作为影像显示缓冲,但受限於9x13mm BGA封装之体积,而不易导入至小型AIOT系统架构中。

DDR3记忆体若采用x16规格於96引脚BGA封?,体积大约9 x 13 mm,即使改采0.8 mm间距6列16引脚,或改用256 Mb至8Gb任何容量之晶粒,其最小封?体积维持不变。

不同於BGA封装,一种先进封装技术:扇入型晶圆级晶粒尺寸封装(Fan-In Wafer Level Chip Scale Packaging,FI-WLCSP),先在整片晶圆上进行封装及测试,然後才切割成单一晶片,无需经过打线及填胶程序,封装後的晶片尺寸与晶粒几??一致;其没有基板,也没有引线接合或倒装晶片等封装步骤,取而代之的是:沉积的电介质、光定义的导体、接着是电镀和锡球落下测试,所有程序都在完整的晶圆上处理完成。?

因为所有锡球必须适配於半导体晶粒的周边,所以极不可能会将体积小晶粒用高引脚数封装。因此,低容量记忆体较不可能采FI-WLCSP封装,因其球间距太小而无法制造。另一方面,大容量DRAM晶粒可支持可制造的球间距,但因矽尺寸太大而无法承受热循环应变:矽和PCB具有太大的热膨胀系数而不匹配。

根据特殊应用之ASIC系统设计,假设的接合垫限制了边缘旒合晶粒具有240个引脚,每侧有60个接合垫,为DDR3接囗预留了100个接合垫。

??创PRC DRAM实体层总共可节省60个(每侧少15个)接合垫。比较此两种记忆体方案,采用??创RPC DRAM的ASIC系统明显小了56.25%。