鈺創科技開發了一種新DRAM架構–RPC DRAM技術,提供x16 DDR3 – LP DDR3數據頻寬,採僅使用22個開關信號之40引腳FI-WLCSP封裝,256 Mb DRAM體積為2 x 4.4 mm,所有40個引腳均採用業界標準之400微米錫球間距安裝在周邊,使其成為許多可穿戴的影音物聯網設備的理想記憶體。

|

| 鈺創科技新DRAM架構–RPC DRAM技術,提供x16 DDR3 – LP DDR3數據頻寬,採僅使用22個開關信號之40引腳FI-WLCSP封裝 |

鈺創指出,新一代的智慧型消費性電子產品皆具備多元功能交互應用,例如智慧通訊、資料影音即時傳輸等功能,而影音多媒體串流往往由於佔據大量頻寬及記憶容量,使之成為系統架構瓶頸之一,也是系統設計者面臨的最大的挑戰之一 。

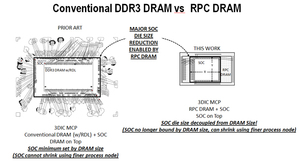

鈺創之新型RPC DRAM具備特殊應用(ASIC)記憶體的優點,它採鈺創RPC DRAM之實體層(Physical Layer,PHY),可有22個開關信號,而輸出共有40PHY接合墊;比一般相同頻寬之DDR3 PHY,所須的47個開關訊號 (x16 data bus)及達100 PHY接合墊,使用不到一半的接合墊,用在特殊應用之記憶體接口。

緩衝記憶體常被用於影音多媒體系統中,作為視訊畫面播放速率轉換、顯示緩衝、鏡頭去扭曲及陰影校正、慢動作緩衝等。最常見的需求是存儲一兩個視訊幀(即視頻速率轉換和顯示緩衝),其它如慢動作視訊緩衝則較無硬體限制,這樣情況下,DDR3 DRAM x16 BGA 封裝即可滿足其需求。

然而,此設計卻常會遇到穿戴式裝置的物理極限,以眼鏡型的影音傳輸播放系統為例,DDR3所提供數據頻寬已足以作為影像顯示緩衝,但受限於9x13mm BGA封裝之體積,而不易導入至小型AIOT系統架構中。

DDR3記憶體若採用x16規格於96引腳BGA封?,體積大約9 x 13 mm,即使改採0.8 mm間距6列16引腳,或改用256 Mb至8Gb任何容量之晶粒,其最小封?體積維持不變。

不同於BGA封裝,一種先進封裝技術:扇入型晶圓級晶粒尺寸封裝(Fan-In Wafer Level Chip Scale Packaging,FI-WLCSP),先在整片晶圓上進行封裝及測試,然後才切割成單一晶片,無需經過打線及填膠程序,封裝後的晶片尺吋與晶粒幾乎一致;其沒有基板,也沒有引線接合或倒裝晶片等封裝步驟,取而代之的是:沉積的電介質、光定義的導體、接著是電鍍和錫球落下測試,所有程序都在完整的晶圓上處理完成。?

因為所有錫球必須適配於半導體晶粒的周邊,所以極不可能會將體積小晶粒用高引腳數封裝。因此,低容量記憶體較不可能採FI-WLCSP封裝,因其球間距太小而無法製造。另一方面,大容量DRAM晶粒可支持可製造的球間距,但因矽尺寸太大而無法承受熱循環應變:矽和PCB具有太大的熱膨脹係數而不匹配。

根據特殊應用之ASIC系統設計,假設的接合墊限制了邊緣粘合晶粒具有240個引腳,每側有60個接合墊,為DDR3接口預留了100個接合墊。

鈺創PRC DRAM實體層總共可節省60個(每側少15個)接合墊。比較此兩種記憶體方案,採用鈺創RPC DRAM的ASIC系統明顯小了56.25%。