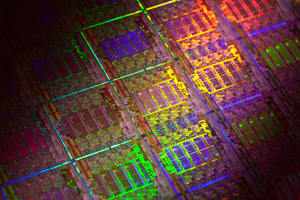

Mentor Graphics公司(明导)宣布与三星电子合作,为三星代工厂10奈米FinFET制程提供各种设计、验证、测试工具及流程的优化。其中包括Calibre物理验证套件、Mentor Analog FastSPICE(AFS)平台、Olympus-SoC数位设计平台和Tessent测试产品套件。这些工具皆经过优化和认证,使系统晶片(SoC)设计工程师能够快速适应三星代工厂先进的10奈米制程,并且对第一次试产就能成功有极大的信心。

|

| Mentor Graphics优化工具和流程,协助设计工程师成功应对三星代工厂10奈米FinFET制程 |

设计风格和制造制程之间的相互作用在10奈米会变得更为重要,因此可制造性设计(DFM)工具在验证流程中发挥关键作用。三星代工厂已对Calibre YieldEnhancer产品,特别是其SmartFill和ECO/Timing-Aware Fill功能进行认证,帮助设计工程师在多次更改设计的情况下,仍能满足制造制程平坦化要求,赶上交付制造期限。为了帮助设计工程师发现和解决潜在的微影相关问题,三星支援Calibre LFD工具的使用,该工具是基于Mentor的制程process-window modeling、光罩合成、光学邻近效应修正(OPC)和解析度增强( RET) 的量产制造方案。

由于设计团队可同时处理多个 DFM 元素,他们可使用建在Calibre Yield Analyzer工具上的三星 DFM评分和分析解决方案以简化决策权衡流程。最后为把制造结果快速回馈到客户设计流程中,三星使用 Calibre Pattern Matching 作为识别造成低良率的图形并予以修正的解决方案。

在物理验证方面,Calibre nmDRC平台经认证可用于10奈米制程,并成为三星研发、IP验证和无晶圆厂客户设计交付制造的生态系统中标准验收签核方案。三星使用Calibre Multi-Patterning 作为三重曝光和四重曝光的制造制程开发在多年的合作后得到成功。

三星代工厂已认证 Calibre xACT能够于10奈米中提供高精度和高性能的寄生参数提取。 Calibre xACT工具使用整合的场求解器(field solver)来计算复杂三维 FinFET结构的寄生参数。它经由高度可扩展的平行处理方法进行性能优化。

其他认证则有助于IC设计工程师进行电路验证、物理应用和IC测试。例如,AFS平台得到三星10奈米制程元件模型和设计套件的认证。共同的客户使用AFS,为类比、射频、混合信号、记忆体和客制化数位电路的验证,提供比传统SPICE模拟器速度更快的奈米级的SPICE精确度。

Olympus-IC布局和布线平台也已经过认证,可用于10奈米制程,具有全面的著色设计方法,包括底层规划、布局、寄生参数抽取、布线和晶片完成要求。为了解决FinFET制造制程中的特殊挑战,该平台支持M1三重曝光、色移(color shifting)、非一致布线通道、光罩和宽度依赖间距规则以及其他新增功能。有多个共同客户正在使用该工具进行设计。

在测试方面,Mentor和三星已展开合作,使Tessent测试产品套件可为新单元结构提供10奈米级更佳的测试品质,同时为更大规模的10奈米设计测试提供更高的测试图形压缩率进而控制成本。两家公司还利用生产测试诊断来快速识别和消除设计试产扩量阶段出现的特定于设计和影响良率的单元特征。

「我们与三星代工厂的合作远非仅仅是将这一先进的制程带给我们共同的客户,」Mentor Graphics Design to Silicon部门副总裁兼总经理Joe Sawicki说道,「此整合解决方案贯穿于设计验证、制造和测试中,为无晶圆公司和三星代工厂之间建立起了高度整合的桥梁。」