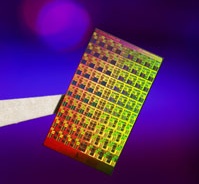

英特尔(Intel)于周二(2/13)发表一个内含80颗核心的兆级运算(Tera Scale)可编程处理器(programmable processor)。该芯片面积仅指甲般大小(275平方公厘),却拥有同于超级计算机等级的运算能力,能提供每秒数兆次浮点运算(Teraflops)的效能,同时耗电量更低于目前的家电产品。该芯片目前仍处于实验室开发阶段,未来将有可能应用至计算机、手机等其他电子装置上。

|

| 英特尔(Intel)发表80核心具备兆次级运算的处理器,每个核心内皆含有两个浮点运算的引擎(图片提供:Intel) |

此芯片是英特尔兆级运算研究项目其中一个研发成果。该项目成立至今仅约1年多,目前已有100多个研究项目正在进行中,主要范畴是在微处理器(Microprocessor)、平台(Platform)、程序设计(Programming)等三个领域上,目前着重的研究方向为处理器的多核心架构、弹性设计、电能节省,以及平台模块的3D内存架构研发。

英特尔中国研究中心总经理杜江凌博士表示,此芯片的研发成功乃是处理器设计上的一大突破。它是以瓷砖(Tiled)的方式拼贴而成,共结合了80颗相同的处理器,而每个核(Core)上都具备运算及通讯单元,能单独进行运算并与周遭的处理器进行沟通,串成一个网状的运算网络。

这样的设计方式将可大幅缩减处理器的设计时程,更可以达到模块化(Modular)及客制化(Scalable)的目的。杜江凌博士表示,未来工程师只要”copy and pasted”就能完成处理器的设计。但杜江凌博士也指出,多核心架构的设计并不在于核数的多寡,而在于应用的效能上,这就取决于设计者的能力,看其是否具备良好的应用弹性。

除了设计简捷之外,新的处理器也具备优越的节电效能,由于每个核心内都具有控制单元,能自由控制运作与否,因此只要将在待命及暂时无作用的核关闭,便可大幅缩减电力的消耗,在节能上具有极高的效能。以目前的设计来说,要达到1.01兆级浮点运算的性能,大约只需消耗62W的电力。

杜江凌博士并指出,此多核心架构未来还会更进一步发展,将在其上堆栈内存(3D Stacked Memory),也就是利用核心上预留的Z轴通讯线路,来连接内存,届时将可更大幅的提高处理器的效能,而这个技术约有可能在1年内实现。

目前此芯片仍未有具体的产品及上市计划,但杜江凌博士表示,将有可能应用在复杂而小型的产品,如手机上。杜江凌博士也强调,产品并不是此芯片的研发重点,重要的是技术的提出,并且促使更多的应用需求被实现。