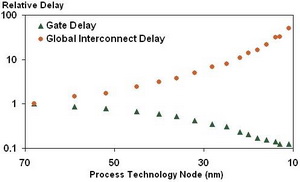

为了使集成电路组件的性能跟上摩斯定律(Moore’s Law),集成电路设计人员在驱策技术节点缩小化时必需减缓RC迟滞效应。为达到组件缩小所带来的应有的积效进而增加45奈米以下导线间的空间缩小所带来的挑战。在过去几年里,研究人员研究了替代材料和更复杂的整体整合方法以解决RC迟滞问题。虽然在研究环境中看到了成效,但大多数这些材料和整合技术最终还是面临转移到量产时之过程控制和生产成本的挑战。

|

| 剖面测试架构中显示了诺发系统的介电薄膜和其特有薄膜接口 |

诺发系统最近已开发出一套突破性技术来导入介电薄膜沉积和其薄膜接口控制制程,它提供需无复杂的重大变化来降低百分之五的有效介电常数(keffective)价值超过各种途径。图中的剖面测试架构中显示了诺发系统的介电薄膜和其特有薄膜接口。

这些在薄膜沉积的创新方法就是利用诺发的PECVD系统,VECTOR的多站连续沉积架构来实现。开发小组对影响薄膜沉积堆栈及其薄膜接口控制参数实施优化的调整,使诺发系统的客户在面对未来新技术节点需求条件下还能够继续延用。

诺发PECVD事业群的技术总长Mandyam Sriram 说明,RC迟滞效应所重视的是有效的介电常数值(keffective),而不是每一薄膜层的绝对K值。现今业界中最快和最先进的集成电路组件就是使用诺发的介电薄膜还制造。进而证明我们可为我们的客户提供简单化的制程整合流程及同时拥有低成本及量产就绪的解决方案。