近期有數家晶圓廠宣布,其3奈米或2奈米邏輯晶片的量產技術將轉移陣地,從主流的鰭式場效電晶體(FinFET)製程,改以奈米片(nanosheet)的電晶體架構製造。imec將於本文回顧奈米片電晶體的早期發展歷程,並展望其新世代架構,包含叉型片(forksheet)與互補式場效電晶體(CFET)。

晶片產業從未為了量產而急於採用全新的電晶體架構,因為這會帶來錯綜複雜的新局面和投資成本。但在近期,像是三星、Intel、台積電和IBM等公司的公開聲明都在在顯示,我們正面臨製程技術的關鍵轉折。

自2022年或2023年起,這些半導體大廠都將從長期採用的鰭式場效電晶體(FinFET)製程中逐漸轉移,在3奈米或2奈米邏輯晶片的生產規劃中,導入奈米片(nanosheet)形式的電晶體架構。

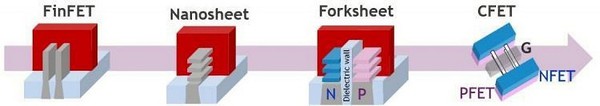

本文將解釋驅動此次歷史性轉折的主要因素,也會介紹不同世代的奈米片架構,包含奈米片、叉型片(forksheet)和互補式場效電晶體(CFET),同時針對這系列架構在CMOS微縮進程中的個別競爭優勢進行評比,並探討關鍵的製程步驟。

從FinFET轉移到奈米片製程的考量因素

為了進一步微縮CMOS邏輯元件,半導體產業投入了大量心力,持續縮減邏輯標準單元的尺寸。降低標準單元的高度是一種作法。該數值被定義為每標準單元的導線數(或軌道數)與金屬層間距的乘積。

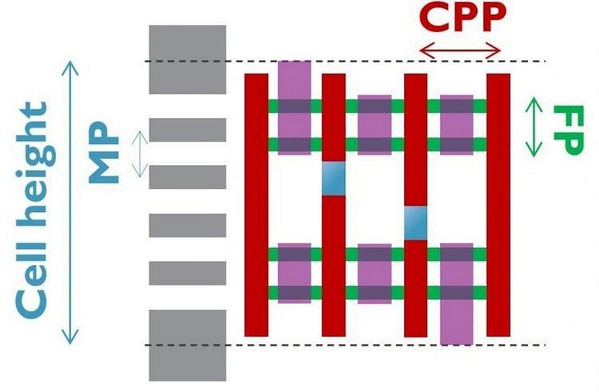

| 圖一 : 邏輯標準單元佈局的示意圖:接觸式多晶矽閘極間距(contacted poly pitch;CPP)、鰭片間距(fin pitch;FP)、金屬層間距(metal pitch;MP),以及標準單元高度(cell height)。 |

|

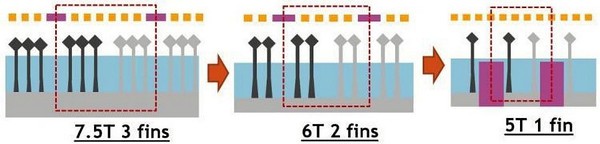

透過減少軌道數,就能縮短標準單元的高度。就FinFET架構來說,新一代的設計是透過減少鰭片數量來實現微縮,從三鰭減至雙鰭,分別構成7.5軌和6軌的標準單元。以6軌的設計為例,指的是每個標準單元高度可容納6條金屬導線。不過如果在減少鰭片數量的同時,維持其尺寸不變,就會降低驅動電流並增加變異性。因此,為了補償這些性能損失,鰭片的構形會被拉長,最終可以實現單鰭5軌的設計。

| 圖二 : 為了進一步微縮標準單元,FinFET架構必須減少鰭片數量,新一代設計的鰭片構形會更長、更薄且更緊密,驅動電流會隨之降低,變異性也會增加。 |

|

然而,要想進一步改良單鰭5軌FinFET元件的驅動電流,其實極有難度,這時就輪到奈米片架構登場。透過垂直堆疊多個單鰭標準單元的奈米片導電通道,就能形成一條更廣的有效通道寬度。如此一來,奈米片可以在相同尺寸下,提供比鰭片還要高的驅動電流,而這正是持續微縮CMOS元件的關鍵優勢。

此外,奈米片架構也提供了調整通道寬度的彈性,在設計上更自由。也就是說,設計人員可以選擇不去調高驅動電流,而是進一步降低元件尺寸與電容:採用較窄的通道設計,通常可以降低層片之間的寄生電容。

奈米片勝過FinFET的另一個顯著特點,就是採用「環繞閘極(gate-all-around;GAA)」結構。在此結構下,導電通道完全被包圍在高介電係數材料或金屬閘極之中,因此,閘極在縮短通道的情況下,仍能展現更佳的通道控制能力。

關鍵的製程模組

如同過去從平面MOSFET轉移至FinFET的過渡時期,目前從FinFET轉移到奈米片結構時,也要面對全新的製程整合挑戰。幸運的是,奈米片可以視為FinFET的自然演變,所以很多為了優化與開發FinFET製程的模組,都能沿用至奈米片製程。這也促使業界更容易接受這套新架構。儘管如此,imec指出,FinFET與奈米片製程仍有四大關鍵差異,需要特別研發創新技術。

首先,為了建構通道的輪廓,奈米片結構會利用矽(Si)與矽鍺(SiGe)進行多層的磊晶成長。由於使用了不同的成長材料,還產生了相應的晶隔不匹配問題,致使傳統的CMOS製程不再適用。在採用多層架構的堆疊中,矽鍺是犧牲層,在除去替代金屬閘極(replacement metal gate;RMG)並釋出通道的步驟中會被移除。接著,整個堆疊會進行圖形化,製成高深寬比的鰭片,因此如何確保奈米片的構形就是個挑戰。

imec在2017年國際電子元件會議(IEDM)上就提出了一套關鍵的優化方案,採用低熱預算的淺溝槽隔離(shallow trench isolation)製程來導入一層襯墊層(liner),結果可以有效抑制氧化誘發的鰭片變形現象。這也強化了對奈米片的材形控制,進而提升元件性能,包含DC與AC效能,前者指的是增加驅動電流,後者則是在相同功率下加快開關速度。採用新型奈米片製程的首個應用案例是環形振盪電路,其AC效能的升級成功反應在更短的閘極延遲上。

奈米片結構與FinFET的第二個差別,是需要導入一層內襯層,也就是透過增加一層介電層來隔離閘極與源/汲極,進而降低電容。在這個製程步驟中,矽鍺層的外部會在進行橫向蝕刻後形成凹陷,隨後,這些小孔洞會以介電材料填充。而整合內襯層就是奈米片製程中最複雜的步驟,對蝕刻技術要求嚴格,需要高選擇比與準確的側向控制。這項挑戰受到各地研究團隊的關注,包含imec在內都在著手解決。

第三個差異在於奈米片製程包含了釋出通道的步驟,奈米片在這之後會相互分離。方法是利用蝕刻移除矽鍺層,過程中需要高度選擇性,才能把少量的鍺留在奈米片之間,並降低矽材的表面粗糙度。此外,為了避免這些微型化奈米片相吸附著,還必須控制靜摩擦力。imec對不同的蝕刻方法進行了基礎研究,包含乾式與濕式製程,目前成果已能大力協助解決上述問題。

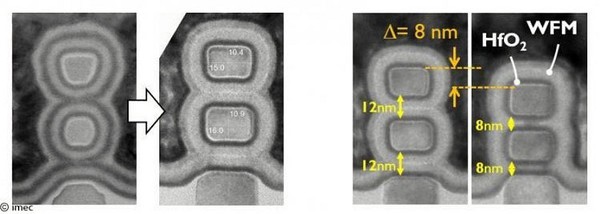

最後一點是替代金屬閘極的整合,包含在奈米片周圍與彼此間的間隙內沉積金屬,並進行圖形化。imec在2018年指出,為了縮短奈米片之間的垂直間距,導入具備功函數調變範圍的金屬材料至關重要。imec團隊也展示相關成果,把奈米片的垂直間距從13nm縮短為7nm,結果AC效能提升了10%,可見微縮替代金屬閘極的重要性。

| 圖三 : 針對垂直堆疊的環繞閘極奈米片進行優化:(左)材行控制,(右)垂直間隙縮減。 |

|

叉型片登場

要提升奈米片的DC效能,最快速有效的方法是增加通道的有效寬度。然而,在一般的奈米片架構下,實現這點並不容易。主要問題是,n型與p型MOSFET之間必須保留大範圍的間隙,因此,當標準單元的高度經過微縮,容納更寬的有效通道就會越來越難,而且n-p間隙在金屬圖形化時還會變小。

叉型片能夠解決n-p間隙的問題。該架構由imec提出,首次亮相是在其2017年國際電子元件會議(IEDM)發表的SRAM微縮研究,在2019年會議發表的研究中則作為邏輯標準單元的微縮解決方案。叉型片製程實現了縮短n-p間隙的目標,在閘極圖形化前,先在n型與p型元件之間導入一層介電牆,圖形化的硬光罩就能在該介電牆上進行,相較之下,奈米片製程則將其置於閘極通道底部。

導入介電牆能大幅緊縮n型與p型元件之間的距離,通道的有效寬度隨之增加,同時提升驅動電流,也就是DC效能。此外,n-p間距微縮除了可以達成通道有效寬度的最大化,還能選擇用來減少標準單元的軌道數,從5軌降至4軌。這就需要開發後段與中段製程的創新技術,採用全新的微縮加速器,例如埋入式電源軌(buried power rail)與自對準閘極接點(self-aligned gate contact)。

根據模擬結果,叉型片的AC效能還有可能勝過奈米片,增加10%。對此,imec團隊也提出解釋,由於閘極與汲極之間的重疊區域縮小,米勒電容或寄生電容也會降低,進而提升元件的開關速度,這也可能有助於製造出更高效節能的元件。

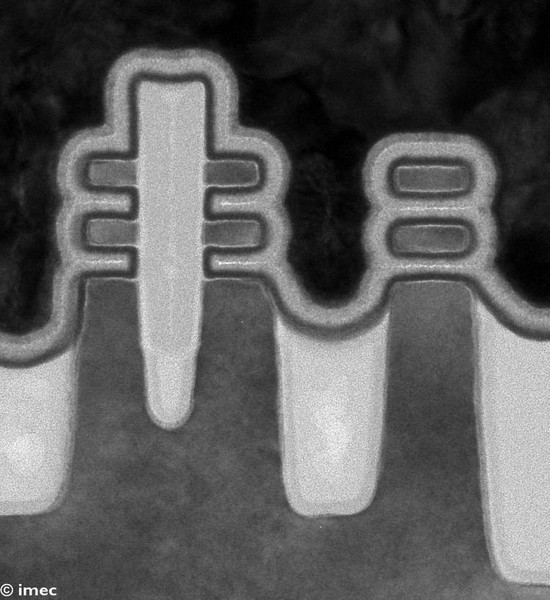

從製程的觀點來看,叉型片源自於奈米片,是進階的改良版本,主要差異包含導入介電牆、改良內襯層與源/汲極的磊晶成長、進一步微縮替代金屬閘極。imec在2021年國際超大型積體電路技術研討會(VLSI)首度展示了以300mm奈米片製程整合的場效型元件,並公開其電氣數據。其中,該元件在僅僅17nm的n-p間距內,成功整合了雙功函數的金屬閘極,顯現採用叉型片架構的最大優勢。

不過叉型片架構還有靜電力的問題。奈米片最受關注的特點,就是其四面環繞的閘極架構,藉此可以大幅提升對通道的靜電控制能力,但叉型片卻似退了一步,改成三面閘極架構。儘管如此,imec在上述實驗中將奈米片與叉型片共同整合在同片晶圓上,結果發現,叉型片在閘極長度為20nm的情況下,展現了可與奈米片媲美的短通道控制能力(SS SAT=66-68mV)。

| 圖四 : 整合於同片晶圓的奈米片與叉型片之穿透式電子顯微鏡(TEM)影像。其中,叉型片的n-p間距只有17nm,並成功整合了雙功函數的金屬閘極。 |

|

奈米片系列的長跑選手:CFET架構

若要實現有效通道寬度的最大化,互補式場效電晶體(Complementary FET;CFET)是個可行的架構,以垂直堆疊n型與p型元件。也就是說,n-p間距轉成垂直方向,所以不需考量標準單元的高度限制。而垂直堆疊元件後釋出的新空間除了可以進一步延伸通道寬度,還能用來縮減軌道數至4軌以下。

模擬結果顯示,CFET架構能助益未來的邏輯元件或SRAM持續微縮。其通道的構形可以是n型或p型的鰭片,或是n型或p型的奈米片。最終,CFET架構會是奈米片系列中最完善的架構,成為CMOS元件的最佳選擇。

| 圖五 : CMOS元件架構的演變流程,先後依序為FinFET、奈米片、叉型片與CFET。 |

|

CFET架構因為必須垂直堆疊nMOS與pMOS,製程會更複雜。現有兩種垂直整合方案,分為單片式(monolithic)與序列式(sequential),各有優劣。對此,imec開發了相關的製程模組與整合方案,並量化這些製程在功耗、性能和尺寸方面的各自表現,並評估其技術難度。

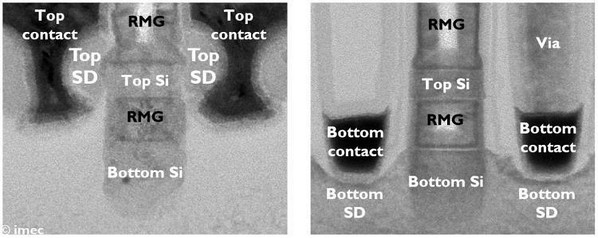

| 圖六 : 採用單片式製程的CFET元件之穿透式電子顯微鏡(TEM)影像:(左)元件頂部(右)元件底部。 |

|

單片式CFET:成本低,但垂直整合製程複雜

製造單片式CFET的第一步,就是底部通道的磊晶成長,再來是沉積中間的犧牲層,最後長成頂部通道。如果要採用奈米片架構,從底部到頂部通道的製造可以選用矽材鰭片,或者矽或矽鍺的多層堆疊。

不論選擇上述何種配置,元件在垂直堆疊後就會形成超高深寬比的架構,因此在進行後續圖形化的多道步驟時,包含鰭片、閘極、內襯層與源/汲極接點,都將面臨嚴峻考驗。舉例來說,整合替代金屬閘極的步驟尤其繁複,因為n型與p型元件需要用到具備不同功函數的金屬材料。

在2020年國際超大型積體電路技術研討會(VLSI)上,imec利用優化的製程模組,首度展示採用單片式CFET架構的整合元件。

序列式CFET:通道可混合材料,但晶圓轉移難度高

序列式CFET製程包含多個模組。首先會先從底部向上製造元件,直至接點,接著是運用介電材料的晶圓接合技術(dielectric-to-dielectric wafer bonding),覆蓋一層未經圖形化的半導體層,最後進行頂部元件的整合,並連接上下閘極。整個過程在中段與後段製程完成。

就整合難度而言,序列式比單片式還要容易,因為其底部與頂部元件能沿用傳統的「平面結構」分別製造。序列式製程還有一大優勢,就是提供n型與p型元件整合不同通道材料的彈性,進而提升元件性能。例如,nMOS採用矽材,pMOS採用矽鍺或鍺,甚至是導入二硫化鎢(WS2)等二維材料。

然而,這些全新製程也帶來了一些特定挑戰,需要各自開發。第一個挑戰與晶圓之間的接合有關,也就是介電材料氧化層的厚度。如果設計得太厚,AC效能就會下降,這也與imec在2020年國際超大型積體電路技術研討會(VLSI)上的展示成果相符。相反地,氧化層若是太薄,就可能會造成接合缺陷,產生更多的孔洞。imec權衡兩種作法,已經針對薄型氧化層開發了一套零孔洞的接合製程。

第二個問題是採用晶圓轉移製程時必須考量的熱預算限制。頂部元件製程的溫度必須降到500℃左右,避免損及底部元件。然而,某些製程步驟因為考量到閘極堆疊的可靠性以及活化摻雜物所需,溫度必須達到900℃。imec近期提出了一些解決方案來滿足兩者需求。

首先,imec團隊開發了兩套新方法,能在低溫環境下確保閘極堆疊的可靠度。一方面,利用低溫氫電漿製程,把位於矽氧化物介電質層的缺陷鈍化,另一方面,在矽通道與二氧化鉿閘極之間導入介面偶極,以抵銷介電材料缺陷狀態與電子導帶之間的能量差距。此外,imec也研發了一套創新的磊晶成長製程,能在低溫狀態下高度活化nMOS與pMOS元件的摻雜物。

不論是單片式或序列式CFET,imec將會持續研究優化的整合模組與製程,提供業界最佳的解決方案。

結語

本文列舉了奈米片系列架構的競爭優勢與技術挑戰,以期延續CMOS邏輯元件的微縮進程。每個新世代架構,包含奈米片、叉型片與CFET,皆各有所長,有的透過優化通道的有效寬度來提升性能,有的進一步微縮標準單元的高度,有的兩者皆然。就製程發展來看,從FinFET轉移到奈米片架構是漸進演變的結果,但不同的奈米片架構必須面對不同的整合挑戰,imec也會持續探索並評估解決方案。

(本文由imec授權刊登;作者Naoto Horiguchi為imec邏輯CMOS微縮研究計畫組長;編譯/吳雅婷)