AI最近因与ChatGPT等自然语言处理器的惊人能力而受到更多关注,但当应用在晶片设计的各个阶段,包括设计最隹化、布局、模拟和验证下,人工智慧演算法可以帮助更有效地探索设计空间,能比传统方法更快地发现最隹设计配置。

晶片业者正利用AI来突破严格的设计约束

由於数十亿个电晶体被置放在一个很小的区域内,因此工程师的设计目标尽管受到严格的限制,仍要达到最隹化设计。

这是由於晶片面积必须不断的被极小化,以满足当今产品对於外形尺寸的要求,以及降低制造成本。这使得布局的功耗备受关注;功耗同样会影响部署成本以及晶片对环境的影响。某些电路密集区域或配置容易过热,无法大量使用需要外部冷却装置来获得解决,需要更巧妙的电路布局。因此考虑到这些和许多其他因素下,往往工程师需花费大约8~9个月的时间来开发出能符合每项严格要求的电路布局。

另外,根据Deloitte Global预测,到2023年,全球半导体业者将投资高达3亿美元,用於提高晶片设计效率,和人工智慧工具上,在未来四年内将在这一数字基础上每年成长20%,到2026年预计将超过5亿美元。对於2023 年市场规模达到6,600亿美元的全球半导体产业而言,这并不是非常庞大的支出,但这对於投资回报来说却是非常巨大与意义重大。

人工智慧设计工具不仅协助晶片业者能够突破摩尔定律的界限、节省时间和金钱,以及缓解人才短缺,同时,还可以提高供应链的安全性,并有助於缓解下一次晶片短缺的危机。换句话说,虽然设计晶片所需的人工智慧软体工具的单机授权许可证可能只需数万美元,但由透过此类工具所开发的晶片产品价值可能高达数十亿美元。

因此,为了加快和最隹化晶片设计流程,已经有愈来愈多的晶片业者导入人工智慧的设计工具,来完成一些繁重且高精细度的的电路设计工作。

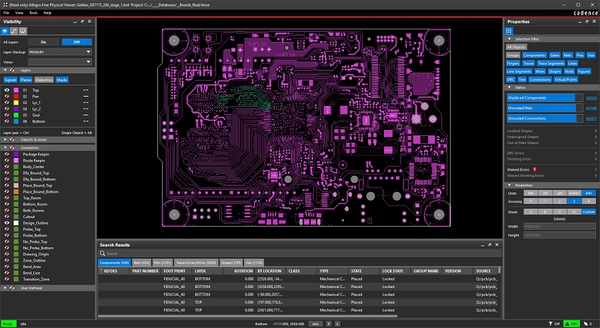

| 图一 : 愈来愈多的晶片业者导入人工智慧的晶片设计工具。(source:Cadence) |

|

时间就是金钱:AI以指数方式加速晶片设计

晶片需要经历三个主要设计阶段:系统级设计、暂存器传输级设计(RTL)以及最後的物理电路设计。而最後阶段,更是先进的人工智慧工具才能真正发挥作用。

晶片设计最隹化了三个变量功耗、性能和面积(PPA)获得:1.最大限度地减少电力消耗;2.最大限度地提高处理速度;3.尽可能小的晶片尺寸。

使用传统工具最隹化PPA速度缓慢且需耗费大量人力,设计迭代(Design Iteration)可能需要数周时间,而且迭代通常只能略微改善PPA。因此设计一款新晶片可能需要花费数年时间进行:透过物理形式设计,对设计和实现进行评估、测试和模拟。

晶片内部被置入了数十亿个电晶体,并且以模组化形式安排,包含了暂存记忆体子系统、运算单元、控制逻辑系统和电源等。在高度复杂布线的晶片中,这些模组须透过长达50公里的导线连接。当模组没有获得最隹排列时,模组间的连接需要更多的布线和空间,同时模组间的寄生电容更可能会影响性能并降低功耗。

先进的人工智慧工具可以通过寻找出增加功耗、妨碍性能或低效使用空间的布局错误,来测试人工设计问题,并且分析及建议改进;最後再进行模拟和测试。这些工具从之前的迭代中学习,以改进PPA,一直到达设计的极限。但真正革命性的是,先进的人工智慧可以自主地完成这项工作,产生出比使用传统EDA工具的人类工程师更好的PPA。

这些先进的人工智慧功能可分为两类:图神经网络(Graph Neural Networks;GNN)和强化学习(Reinforcement Learning;RL)。GNN是一种专门用於分析图的数据结构,其中包含「节点」(可以是任何对象)和「边」(定义节点之间的关系)。

传统的深度学习神经网路很难处理图形,但GNN却可以从图形中获得讯息,对其连接做出有用的预测,并在保留关键关系的同时重新排列节点。由於晶片结构本质上是类似图形的(巨集模组块和标准单元是类似节点的,而连接它们的导线是类似边缘的),因此GNN非常适合分析和最隹化晶片。

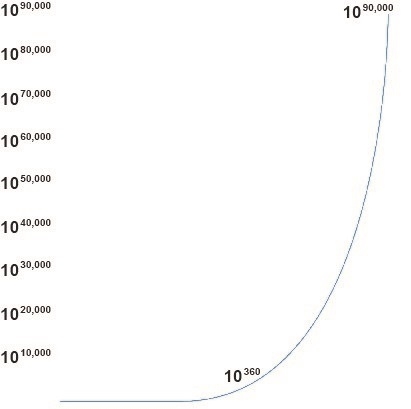

RL是将物理晶片设计转变为图形最隹化「游戏」。这与Google在围棋中击败人类冠军所使用的技术相同,围棋比国际象棋更复杂,被认为超出了人工智慧的能力。而物理晶片设计的复杂性仍然呈指数级增长(图二),因此RL能以同样的方式解决这个问题。它对数千个「游戏」(晶片平面图)进行训练,模拟晶片设计以找到最隹的PPA安排。

| 图二 : 人工智慧在国际象棋和围棋上战胜人类令人印象深刻,晶片设计比国际象棋和围棋可达到更多的可能配置。(source:Deloitte Global;作者整理) |

|

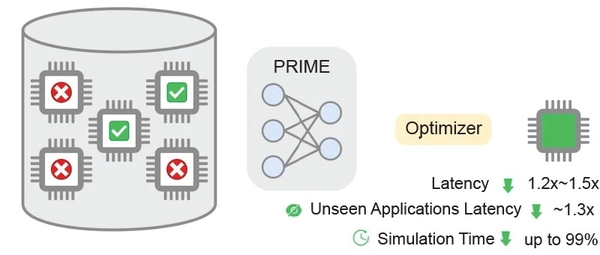

Google的人工智慧可在几个小时内设计晶片

Google发表结合了深度学习(DL)和强化学习(RL)的技术可以在远少於人工设计时间内完成有效的电路布局,并且在品质验证下的结果毫不逊色。2022年3月,Google Research又推出了PRIME,这是一种深度学习方法,它利用现有的功率和延迟等数据,来建立出比传统方设计法更快、更小的加速器设计(图三)。

Google研究人员利用10,000个晶片布局来训练他们的模型,让人工智慧在不到六个小时内,完成晶片的设计。而这种方法已经被用来实现Google的张量处理单元(Tensor Processing Unit;TPU),这也是Google基於云端的机器学习应用平台的一部分。

| 图三 : Google的PRIME利用记录加速器数据,来训练设计加速器的保守模型。(source:google;作者整理) |

|

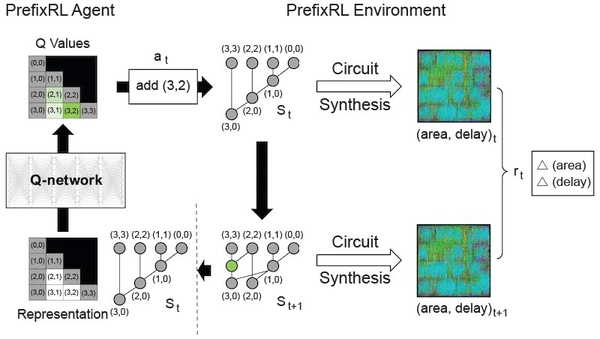

NVIDIA利用GPU的AI架构来进行新绘图晶片开发

而NVIDIA也设计了一种用於晶片设计的深度学习方法。一套名为PrefixRL的RL模型,证明人工智慧可以从头开始学习电路设计,并使用最新的EDA工具来开发出更小、更快的电路。而这个架构是由13,000个使用AI技术设计的电路所组成。此外,NVIDIA还利用AutoDMP让晶片布局的速度提高30倍(图四)。

| 图四 : PrefixRL流程的描述。(source:Nvidia;作者整理) |

|

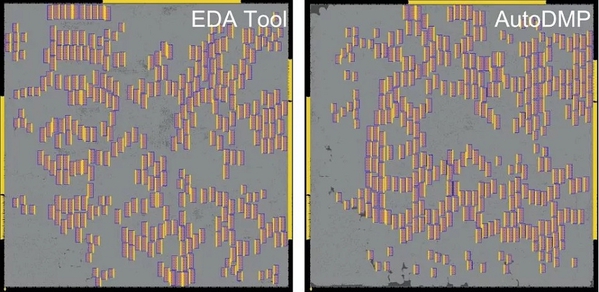

AutoDMP是Automated DREAMPlace-based Macro Placement的缩写,提供晶片工程师使用EDA工具时,在处理器构建模型时,来缩短布局的时间,并且达到最隹化。例如,在解决确定256个RSIC-V内核的最隹布局工作上,AutoDMP仅花费3.5小时就获得NVIDIA DGX Station A100的布局最隹化(图五)。

| 图五 : 透过AutoDMP所得到的布局计划,与资深工程师所设计的布局非常相似。更可证明人工智慧将提供节省大幅时间的革命性。(source:Nvidia) |

|

巨集布局(Macro Placement)对晶片的布局有着重大影响,包括直接影响许多设计目标,例如面积和功耗,更进一步的影响到客户。AutoDMP的工作原理是,将布局问题视为,布局密度限制下的线长最隹化问题,并利用数值方式来获得解决。与以前的放置方法相比,可提高30倍的GPU加速演算。

结语

虽然人工智慧可以自动执行传统上由IC工程师执行的某些任务,例如布局设计和优最隹化,但它也减少了设计过程中对手动方面的需求。虽然这提高了整体效率,但也可能导致IC设计某些领域的人力被取代。

另一方面,人工智慧还可以帮助工程师更有效地完成工作。例如,人工智慧可以分析大量数据并提供分析,为工程师以前可能没有考虑过的设计方案提供建议。这种趋势可以不仅提高了资深IC工程师的价值,使他们能够专注於开发更复杂和更具创意的产品,并最终生产出更好的产品。

以现阶段而言,人工智慧不太可能完全取代对资深IC工程师。更随着人工智慧在行业中变得越来越普遍,或许对此类工程师的需求甚至可能会增加,因为需要这些资深IC工程师在设计过程中,更准确验证和利用人工智慧工具,以及更各种演算法。