透過整合深寬比捕捉(ART)技術與奈米脊型工程(nano-ridge engineering),愛美科成功在300mm矽基板上成長出砷化鎵(GaAs)或磷化銦鎵(InGaP)的異質接面雙極電晶體(HBT),實現5G毫米波頻段的功率放大應用。

前四代的行動通訊技術在傳輸頻率方面的變革,一向呈現逐步演進,而非革命性的。操作頻率從僅不到十億赫(GHz),躍升至好幾十億赫,而頻寬也從幾十千赫(kHz)擴展至幾十百萬赫(MHz)。

從這些傳輸特性來看,第五代行動通訊技術(5G)可說是脫離過往所有技術的激進變革。5G的部分傳輸工作仍會使用一些GHz頻率—也就是sub-6 GHz頻段,但除此之外,它還使用了毫米波頻段,也因此,現行的網路頻段需要處理相關的頻寬限制問題。

| 圖一 : 全球5G網路的頻譜分配情形。(source:gsma.com) |

|

使用毫米波的缺點之一,例如以28GHz與39GHz為主的頻段,在於訊號功率會出現明顯衰減。為了解決這項痛點,5G網路開始出現部署小型基地站的需求,還需開發全新的行動裝置設計,使得元件的前端設計變得更加複雜。

以砷化鎵(GaAs)或磷化鎵銦(InGaP)製成的異質接面雙極電晶體(HBT),是目前行動裝置的關鍵元件,其成長於造價不菲的GaAs基板上。這類電晶體被用來製造功率放大器,該元件特色是具備多個獨立模組,不同模組處理不同頻段。

隨著5G網路開始支援毫米波頻段,HBT元件的射頻性能勢必要維持水準,甚至進一步提升,同時還要降低成本、增加電路設計彈性、減少功率耗損與元件尺寸。不幸的是,目前的商用技術還在努力開發出優良的射頻前端模組,滿足上述所有需求,因此改用創新材料與元件架構,成為時勢所需。

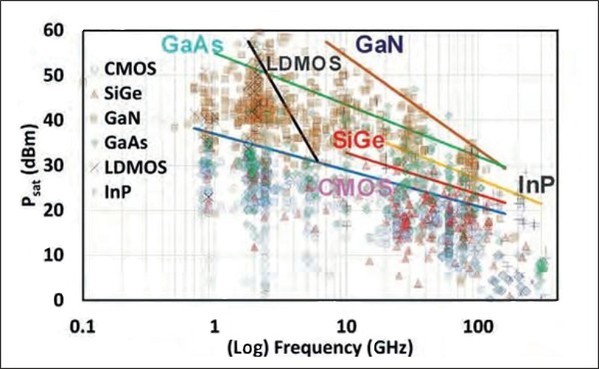

愛美科已經開發出異質三五族CMOS技術,能夠滿足毫米波射頻應用的小尺寸、低成本需求。這項技術在高頻狀態下操控三五族元件系統的功率負載(圖二)以及線性度,並利用先進的CMOS後段製程來製造複雜的控制電路。

此外,多虧了共整合(co-integration)技術,這項技術還有可能進一步改善整體電路的能耗效率,實現可供量產的高能耗效率、低成本的毫米波技術。

| 圖二 : 不同元件技術在不同操作頻率下的輸出功率趨勢;實線僅供輔助瀏覽。(source;gems.ece.gatech.edu) |

|

要將像是GaAs的三五族材料與矽材整合,其中一項的最大挑戰,就是嚴重的晶格不匹配。在晶格不匹配的矽基板上進行磊晶成長會產生缺陷—多半是穿隧差排(threading dislocation)。這些缺陷會導致不被樂見的漏電流,折損元件性能。

有些研究團隊在矽基板與元件之間導入一層應力鬆弛的緩衝層,持續努力降低這些缺陷密度。但是增加元件層就會加諸龐大的成本。這些增設的元件層以矽鍺(SiGe)、鍺或三五族變晶堆疊製成,且堆疊厚度需達至少10μm,才能有效將缺陷密度降至可接受的數值。

事實是,不論要用什麼方法來開發CMOS三五族技術,為了控制元件的複雜度與製造成本,勢必要採用標準矽基板。

深寬比捕捉技術

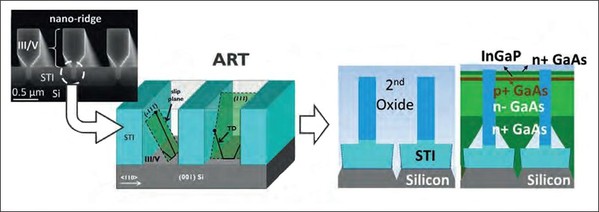

愛美科的解決方法是結合深寬比捕捉技術與奈米脊型工程,前者將缺陷侷限在窄溝底部,後者可實現零缺陷且可增加產量的三五族元件製造(圖三)。隨後採用完全相容於CMOS的製程來進一步處理奈米脊結構,製出最終的元件,並實現與矽基CMOS元件的共整合。

| 圖三 : 利用深寬比捕捉技術(aspect ratio trapping;ART)技術與奈米脊型工程來成長奈米脊(nano-ridge)結構的示意圖。可以發現,穿隧差排因為ART技術而得以捕捉在窄溝內,同時,相對零缺陷的奈米脊得以成長於第二層氧化層內。 |

|

這項作法的優勢之一是,能在不需成長厚緩衝層或使用昂貴基板的情況下,將矽基版與三五族材料進行整合。況且愛美科還能善用其以300mm晶圓製造三五族元件(III-V-on-300 mm)的專業技術—當初開發是為了要持續微縮CMOS技術和研究矽基CMOS元件。

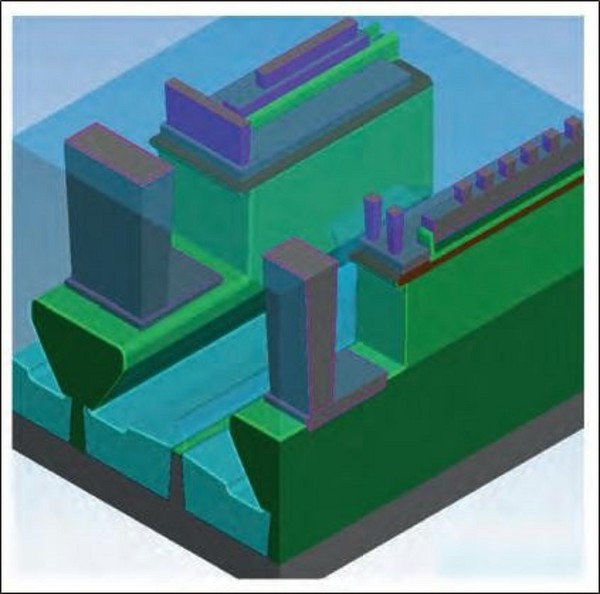

為了製造奈米脊,愛美科將三五族材料成長於300mm的(001)矽晶圓上,採用雙層氧化層的結構(圖四)。第一層二氧化矽(SiO2)層是400nm的淺溝隔離(shallow trench isolation;STI)模板,其特色在於80nm寬的窄溝圖形,且底部有{111}矽晶向的V型槽,間隙為800nm。

| 圖四 : 三五族HBT元件可以愛美科開發的CMOS相容製程,整合在300mm矽晶圓上。 |

|

在這之上,愛美科加了第二層氧化層,厚度為1000nm,成長出600nm寬的溝槽,位於下層窄溝的中間。

之後,運用選區成長(selective-area growth)技術,愛美科將三五族材料沉積在窄溝內。三五族材料與矽材之間的嚴重晶格不匹配會產生缺陷,但這些缺陷,因為高深寬比的結構,會被侷限在溝槽底部。這就確保了窄溝外成長的材料能免除穿隧差排的缺陷。

接下來是進行奈米脊型工程,藉由拓寬奈米脊來維持(001)長晶面,製出平坦的接面。倘若奈米脊型工程能成長出獨立式的元件架構,會導致大的盒型圖形。為了避免這個現象,愛美科加了第二層氧化層模板。一旦奈米脊碰到第二層氧化層,就會減少元件主動區的側壁沉積。

愛美科在低壓的金屬有機化學氣相沉積(MOCVD)腔體中,在300mm矽晶圓上成長出這些三五族材料,由於反應物來源是三五族材料,因此使用傳統的液相前驅物。另加入四溴化碳(carbon tetrabromide)與矽烷(silane)進行摻雜。

要注意的是,奈米脊型工程不僅能製造傳統三五族上矽元件的盒形成長(box-like growth),還能透過仔細調整成長條件來製出不同圖形,進而能以奈米等級準確操控奈米脊的輪廓。

缺陷的特徵分析

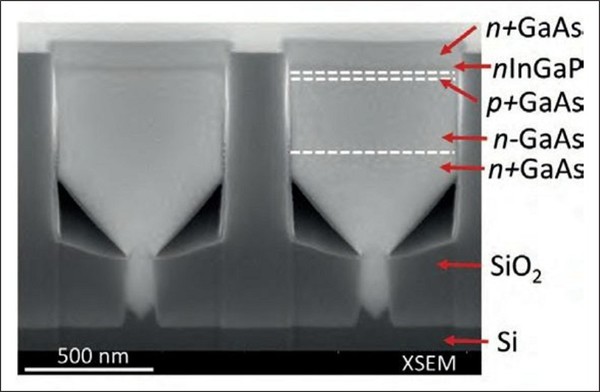

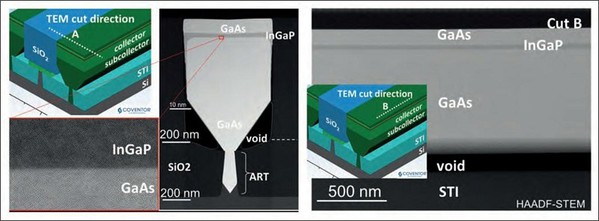

為了評估這套方法的有效性,愛美科進一步分析奈米脊內的缺陷密度。而檢視材料最常用的技術之一,就是穿透式電子顯微鏡(TEM)。愛美科使用的是TEM中的高角度環型暗場掃描(high-angle annular dark-field scanning),它能揭露溝槽內的缺陷。結果顯示,愛美科的三五族堆疊中並沒有錯合差排(misfit dislocation)(圖五、圖六)。

雖然傳統的TEM能提供更準確的缺陷偵測,但其掃瞄範圍很小,若要以此取得可靠的缺陷密度,過程會相當繁瑣。

| 圖五 : 利用深寬比捕捉技術(aspect ratio trapping;ART)技術與奈米脊型工程來成長奈米脊(nano-ridge)結構的示意圖。可以發現,穿隧差排因為ART技術而得以捕捉在窄溝內,同時,相對零缺陷的奈米脊得以成長於第二層氧化層內。利用奈米脊型工程,在300mm矽基板上成長砷化鎵(GaAs)與磷化鎵銦(InGaP)脊型結構的掃描電子顯微截面圖(XSEM)。注意主動區元件堆疊內並無缺陷。 |

|

| 圖六 : 利用深寬比捕捉技術(aspect ratio trapping;ART)技術與奈米脊型工程來成長奈米脊(nano-ridge)結構的示意圖。可以發現,穿隧差排因為ART技術而得以捕捉在窄溝內,同時,相對零缺陷的奈米脊得以成長於第二層氧化層內。運用高角度環型暗場掃描,奈米脊的寬邊(左)與長邊(右)的穿透式電子顯微(TEM)影像。 |

|

另一項常用來檢視材料的技術是電子通道對比影像(electron channeling contrast imaging),它能相對迅速地產生具備統計相關意義的資料集。藉此,愛美科發現,在GaAs奈米脊表面的穿隧差排密度低於3x106 cm2。由於缺陷密度的數值受限於掃描區的大小,愛美科預計,GaAs奈米脊內的穿隧差排密度,實際上還會比上述數值更低。

基於這項研究結果,可以知道愛美科開發的奈米脊,穿隧差排密度低,足以防止元件受到重大的負面影響。

晶格常數不匹配的磊晶系統,也可能會因為面缺陷(planar defect)而佈滿孔洞。愛美科的方法,是將這類缺陷捕捉在與側壁平行的{111}晶面上,但是當面缺陷與側壁垂直時,面缺陷有可能會落入元件堆疊內。這個情況下,密度可能介於0.14μm-1~0.45μm-1。慶幸的是,由於面缺陷不包含開放的晶體鍵(open crystal bond)或應變場,因此對元件性能的影響比差排缺陷小。

300mm矽上HBT元件

愛美科利用其零缺陷矽上三五族元件層的成長技術,已經展出以單晶整合於300mm標準矽基板上的GaAs/ InGaP材料HBT元件,成功在超越5G時代的應用中,為基於InGaAs的元件提供技術跳板。

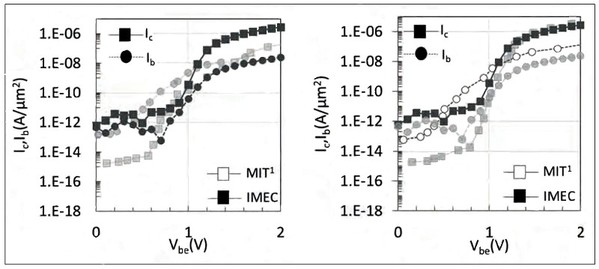

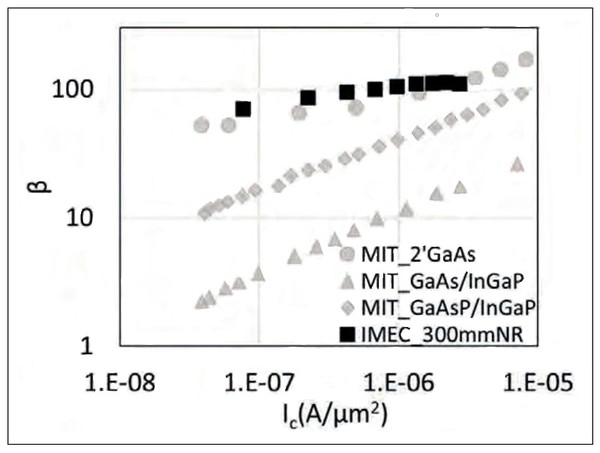

這項技術取得重大進展的基礎,在於採用n-InGaP/p-GaAs/n-GaAs架構的一組堆疊,其展現了HBT的元件特性。該堆疊的射極-基極二極體,以及基極-集極二極體,理想因子分別約為1.2和1.4,顯現了在接面與成長材料方面的優異品質。此外,其DC電流增益可高於110,集極-基極的崩潰電壓為10V,也能證明這個架構具備優良的材料品質。

| 圖七 : 利用深寬比捕捉技術(aspect ratio trapping;ART)技術與奈米脊型工程來成長奈米脊(nano-ridge)結構的示意圖。可以發現,穿隧差排因為ART技術而得以捕捉在窄溝內,同時,相對零缺陷的奈米脊得以成長於第二層氧化層內。比較愛美科開發之HBT元件與導入應力鬆弛緩衝層的參考元件,圖為兩者的電氣特性差異(Gummel plots特性曲線圖)。 |

|

為了衡量元件的標準,愛美科針對元件轉換特性,比較這款HBT元件與採用類似設計的其他HBT元件;參考元件在2吋GaAs基板上製造,其應力鬆弛且厚的緩衝層,具備與愛美科HBT元件相似的缺陷密度(圖七)。結果令人振奮,愛美科元件的性能勝過具備厚緩衝層的參考元件,且愛美科元件的性能特點,與成長於2吋高品質GaAs基板的元件極為相似(圖八)。

這項研究結果與愛美科所言相符,其提出的奈米脊型工程,以300m矽基板製造,能充分提供所需的材料品質—也就是說,不論是應力鬆弛且厚的緩衝層,或昂貴的基板,其實都不需要。

| 圖八 : 利用深寬比捕捉技術(aspect ratio trapping;ART)技術與奈米脊型工程來成長奈米脊(nano-ridge)結構的示意圖。可以發現,穿隧差排因為ART技術而得以捕捉在窄溝內,同時,相對零缺陷的奈米脊得以成長於第二層氧化層內。以奈米脊型工程製造的GaAs/InGaP材料HBT元件,以及具備應力鬆弛緩衝層的參考元件;圖為兩者的DC電流增益比較。 |

|

愛美科的矽上三五族元件成功取得了優異的研究成果,因此對這項技術抱持了高度期待。這項技術的優勢之一,展現在三五族材料與CMOS矽基製程的整合能力,進而實現5G與毫米波應用。它可以在300mm矽基板上成長出採用InGaAs材料的HBT元件,部署在5G世代之後的射頻應用中。

愛美科的異質三五族CMOS技術,從初期的元件性能表現,逐漸改良至現今堪比高品質GaAs基板製成的元件性能。愛美科將持續開發奈米脊型工程技術,充分發揮其潛力。

(本文由愛美科授權刊登;作者Amhitosh Vais為愛美科研究員/編譯:吳雅婷)

**刊頭圖(source:imec-int.com)