3奈米儼然成了一個新的關卡,誰能先突破,誰就有希望在202x之後的半導體代工市場,取得領先位置。而目前率先揭露3奈米技術進程的則是三星電子(Samsung Electrics),該公司預計會在2021年導入量產,並聲稱領先台積電1年的時間。

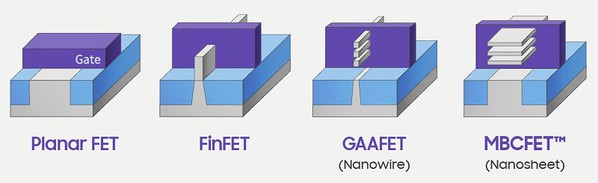

| 圖一 : 從結構的發展可明顯看出,3奈米將會走向一個新的、更複雜的結構。(source:三星電子) |

|

放眼市場,目前有能力將半導體製程推進到7奈米以下的業者,僅剩下三星電子和台積電,因此在先進製程的對抗,也就是這兩家業者之間的競爭,甚至可以說,誰能勝出,誰就有希望取得絕對的市場優勢。

面對三星電子的叫戰,台積電絲毫聞風不動,仍持續穩步的推進微縮製程,依據台積電的規劃,將會在2020年量產5奈米製程,至於3奈米,目前仍沒有公布具體的時程表和技術細節。唯一確定的,就是其3奈米的新竹廠房將會在今年底動工,以時間推估,能夠量產的時間也會是在2021年之後。

FinFET將退場 3奈米帶起新製程之戰

而為什麼3奈米製程如此關鍵,最主要的原因就是當前的微縮製程走到3奈米,將會面臨新的物理極限,除非改用新的結構,否則摩爾定律就很難再維持下去。

目前三星和台積電的7奈米和5奈米製程,都是使用鰭式電晶體(FinFET)的立體架構。該製程的問世就是因為平面的微縮技術在25奈米以下遇到瓶頸,為了持續推進摩爾定律,同時改進電力損耗的問題,因此轉採用這種立體的架構。

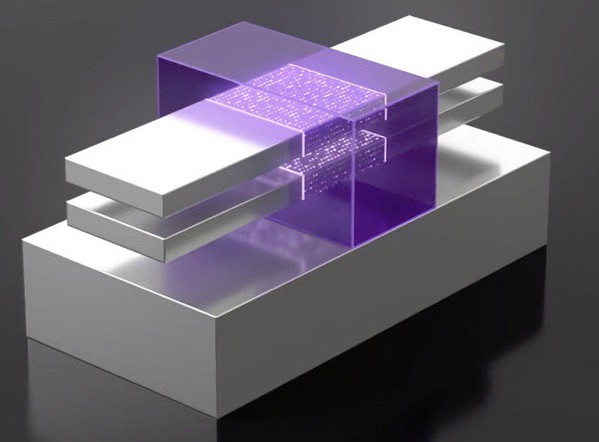

| 圖二 : 三星電子MBCFET製程技術的示意圖。(source:三星電子) |

|

但使用突出鰭式設計的FinFET架構,到了3奈米之後也將面臨微縮的問題,過細的鰭片也將會遭遇電流控制的問題,同時也會失去對某些電場效應的抗性(例如靜電),因此提出新架構就成了3奈米製程的兵家之地。

目前業界的共識是在FinFET架構上來做突破,而兩種分別被名為「Nanowire FET」和「Nanosheet FET」的技術,則是最有希望的接班人,且兩個技術都會使用一種閘極全環(Gate-All-Around,GAA)的製程。

GAA製程興起 考驗代工廠生產技術

首先,必須要先理解一下何謂GAA製程。顧名思義,GAA就是整面都是閘極的意思,而這是相對於FinFET來說,因為在FinFET的架構中,金屬閘極只包覆了三面,而GAA則是全面性的包覆,一種環狀的結構。

而有別於側邊鰭片式的結構,Nanowire FET改以奈米線來取代,藉以增加更多的半導體電路,然後再以閘極來包覆奈米線,以提高對於電路的控制和穩定性;而不同於Nanowire FET,Nanosheet FET是使用更寬更薄的「sheet」來取代,但同樣也使用閘極來包覆。這兩者各有優勢,但從量產的設備相容性以及難度來說,Nanosheet FET似乎多了些青睞。

以三星電子為例,該公司日前公布的3奈米技術內容裡就特別指出,將使用一種閘極全環(Gate-All-Around,GAA)製程為基礎的MBCFET架構。而MBCFET則是多橋通道場效電晶體(Multi-Bridge Channel Field-Effect Transistor),並透過所謂的GAA製程來包覆。從三星的示意圖裡,它應該是一種Nanosheet FET架構的技術。

依照三星電子的說法,使用MBCFET的好處之一,就是它能相容於目前的FinFET製程,因此對客戶來說,具有能直接升級的好處,而且所使用的設計工具與製程方法也都相同,對於成本來說,也不會有太多的提升。

而使用新製程所生產的3奈米晶片的效能也相當卓越,從三星電子公布的測試資料顯示,相較於7奈米製程,使用其MBCFET的3奈米產品效能提升了35%,功耗則大幅下降了50%,同時面積也縮減了45%。其躍進的幅度可說是十分驚人。

三星電子也已在今年5月釋出3奈米GAA MBCFET的製程設計套件(PDK) 0.1版。

而反觀台積電,儘管沒有針對3奈米技術有太多的說明,但台積電對於其製程微縮的能力依然非常有自信,不僅表示3奈米的研發正如期進行中,而且1奈米的門檻目前看來也有望跨越。

但在現階段,台積電則是全力推進5奈米的製程,並加重在極紫外光(Extreme Ultraviolet,EUV)的使用。而從其近期的資本投資來看,全面性的使用EUV來推進其微縮製程已經是必然的方向。

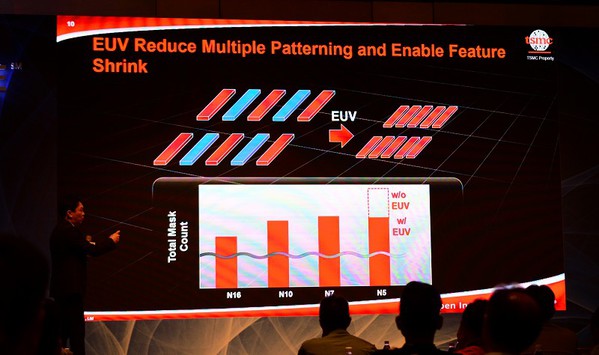

| 圖三 : EUV能減少多重光照的次數,是台積電力推的技術。(攝影/籃貫銘) |

|

台積電也在幾個技術論壇上指出,透過使用EUV,可以大幅減少多重曝光(multi-patterning)所用到的光罩數目,而這對客戶來說是一大福音;EUV同時也能讓間距更細緻,讓更小的微縮製程得以實現,是目前晶圓代工的關鍵生產設備。

EDA也備戰3奈米 精確驗證是挑戰

然而,要實現3奈米製程光靠晶圓廠自己努力是不夠的,尤其是現在晶片生產的流程非常倚重EDA工具,因此勢必要在EDA工具端也有所應對才能算是真正完成量產的準備。

目前主要的EDA工具商也正在準備3奈米製造的相關解決方案,尤其是解決更複雜的半導體結構所衍生的驗證問題。

針對3奈米製程可能衍生的製程挑戰,Mentor IC EDA執行副總裁Joseph Sawicki

在台灣的年度技術論壇上指出,要達到3奈米製程,就必須透過EUV多重曝光的方式來達到更高的解析度。另外,GAA製程也會帶來新的取樣需求和物性錯誤模式(Physical Failure mode)。

| 圖四 : 目前EDA工具商也正在準備3奈米製造的相關解決方案,圖為Mentor IC EDA執行副總裁Joseph Sawicki正講述相關的挑戰。(攝影/籃貫銘) |

|

再者,PPA指標也會推動3奈米光刻製程的精準度要求,多電子束光罩(Multi Beam Mask)寫入技術也會被用來開發曲線光罩的功能,以達成更先進的光刻製程。而上述這些新的製程與技術也會需要透過EDA來進行模擬與驗證,因此EDA供應商就需要與設備和晶圓代廠商緊密的合作來發展相對應的工具。

Joseph Sawicki表示,目前最大的挑戰就是新的更多層堆疊的半導體結構在驗證上非常複雜,如何精確的對每一層進行模擬和驗證將是一大難題。他也預計大約到明年中之後,相關的工具才會比較成熟。

結語

從製程結構來看,3奈米將是一個全新的世代,而作為新時代的開創者,它的優勢也完全反應在效能上。從目前的進展來看,3奈米的實作和量產都已有了解決方案,剩下的只是時間和生產設備到位的時程問題。

至於市場會不會有人買單?答案應該是非常肯定,當然是有,而且可能還會引起搶購,畢竟5G和AI應用的想像空間實在太大了,3奈米晶片也只是剛剛好彌補了他們的需要。

最後,台積電與三星電子的兩虎相爭誰會勝出,目前真的很不好說,只能說三星電子的好勝心和企圖心,不得不讓人尊敬。