可程式邏輯裝置(Programmable Logic Devices;PLD)發展至今已有數十年的歷史,過去以來一直未有太大重視,然而到了近年來PLD的身價逐漸走揚,原因在於半導體製程不斷縮密後,光罩的製造複雜度、難度呈指數性攀升,連帶光罩價格也大幅飆升。

以往光罩便宜時,晶片業者投產的ASIC(Application-specific integrated circuit)晶片,可以透過量產銷售的「量價均攤」效益來承擔最初的光罩開設費用,畢竟光罩只要開設一次就可讓晶片投產,屬一次性花費,然而光罩愈來愈貴後,就無法再以過去的量價均攤法來承擔。

無法承擔高昂光罩費的結果是,只有數種高量、高價的晶片(如CPU、GPU)仍有經濟規模,仍可持續以開光罩方式生產,其他僅高量(如MCU)或僅高價的晶片都無法用傳統ASIC方式生產。若無法使用先進的光罩技術來投產,就只剩兩種方式來投產,一是使用較舊的製程技術,如此光罩費用比先進製程低廉,另一則是使用PLD方式生產。

回過頭來看PLD,多年來PLD就一直使用在非主流的特有領域,特別是一些少量多樣的產品,或是市場變化速度極快的產品,或者是針對某一專案而設計的電路產品,或是一些有機密性要求的電路產品(如軍方專案)等,甚或是在產品仍處於新市場的前期,尚無法瞭解晶片的銷售潛力時,這時無法以光罩方式投產晶片,只好先用PLD晶片來小量生產,以此試市場水溫。上述的各種PLD應用方式都不是大量大宗的主流應用市場,但因為先進光罩的開銷陡斜攀升,使的許多晶片業者不得不選擇用PLD來投產晶片。

在PLD領域中,有簡單的可程式化晶片,如SPLD(Simple PLD,如PAL、PEEL等),也有較SPLD擁有更多邏輯閘、可編組出電路複雜度更高的CPLD(Complex PLD),然還有比CPLD更複雜的,即是FPGA(Field-Programmable Gate Array),由於FPGA是各種PLD中,邏輯閘最多、可程式化電路資源最豐富的一種,因此也最適合用來取代原先想以ASIC投產的晶片。

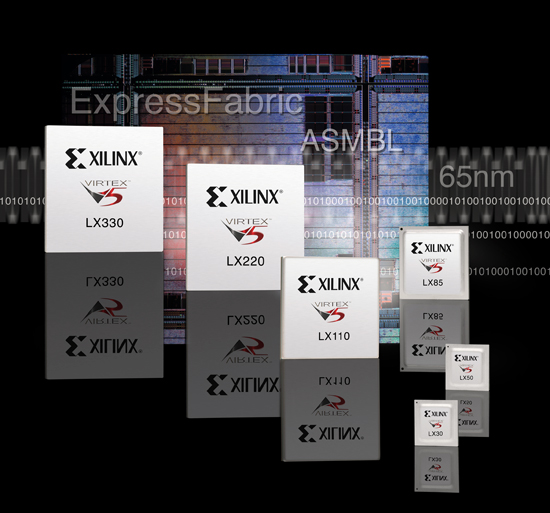

也因為有愈來愈多的晶片捨棄以ASIC方式投產,而改以FPGA方式投產,此使的大型(指邏輯閘、電路資源的大量)的FPGA愈來愈走俏,為了滿足晶片從ASIC轉換成FPGA的需要,FPGA業者無不卯足氣力發展更大量(邏輯資源)、更高階的FPGA晶片,因此在積極使用先進製程的晶片類型中,除了前述的CPU、GPU外又多了一種:高階FPGA,例如Xilinx的Vretex 5、Altera的Stratix III等,都使用了極先進的65奈米製程。

很明顯的,Xilinx Virtex系列與Altera Stratix系列依然會持續使用最新的半導體製程,由於Xilinx、Altera皆是無晶圓廠(Fabless)的半導體業者,設計好的FPGA晶片皆是透過台積電(TSMC)、聯電(UMC)等晶圓代工業者生產,所以一旦TSMC、UMC研發出更先進的製程,Xilinx Virtex、Altera Stratix幾乎都會搶先使用。

現在,Xilinx Vretex 5、Altera Stratix III先後使用了65nm製程後,接下來的必然是45nm製程,只要TSMC、UMC的45nm技術成熟,未來Virtex、Stratix也會積極採用,並有可能因此更替世代編號,變成Virtex-6、Stratix IV等。

先進製程FPGA之運用難題

雖然愈來愈多中量、中價以下的ASIC開始改用FPGA投產,但FPGA在運用上也有一些困難存在。第一是功耗用電問題,FPGA為了能夠可程式化,所以電路必須保持彈性,且為了讓電路運作能夠快速,因此其程式記憶部分多半是用SRAM,理由是SRAM是各種記憶體中速度最快的(也有部分FPGA不是使用SRAM,而是使用Flash Memory或Anti-fuse的反熔絲單次燒寫記憶),然正因為「保持彈性、使用SRAM」使FPGA的功耗比ASIC大很多。

到底大多少?若以實現相同的電路而言,FPGA的功耗約是ASIC的12倍之多,甚至達15、16倍,這是FPGA的致命弱處,也因此FPGA至今都難以運用到行動式、手持式的裝置內,即便是電路複雜性較低的PLD或CPLD,也僅有少數運用到手持式裝置內。所以FPGA仍以固接電源的運用為多,即是用在電源來自電源插座的地方。

即便如此,FPGA依然要極力克制用電,因此今日有許多電源管理晶片業者提出針對FPGA的電源方案,如NS就有針對Xilinx的Virtex、Spartan等FPGA提出參考性的供電設計。

附帶一提的,製程愈縮密後,電晶體的漏電狀況也愈嚴重,使晶片的靜態功耗、整體功耗增加,關於此只能從半導體製程中解決,此目前有兩種常見作法,一是使用矽絕緣(SOI)技術,另一則是使用高介電值(High k)的閘極絕緣技術,且使用高介面值的閘極絕緣物後,原有的閘極材料:多晶矽已不再適用,而必須換成金屬材料,例如鉿,此稱為Metal Gate(金屬閘極)技術,使用High k技術的場合通常也併用Metal Gate技術。

第二個問題是時序收斂,FPGA的設計是數位邏輯工程師完全不用去理會邏輯層以下的物理層特性,包括供電、時序等等,然在大型、複雜化的FPGA電路設計中時序問題依然不可免,若不對時序進行收斂則整體電路的效能無法發揮到極致。

關於此FPGA業者也是尋求與協力業者(Third Party)合作來解決此一問題,例如Xilinx與Synplicity合作,Synplicity是電子設計自動化(EDA)工具的業者,由該公司提供設計工具來幫助設計者對其邏輯電路進行時序收斂。

第三是電路佈局的問題,雖然大型FPGA內已具有相當充沛的邏輯電路資源,但在高度複雜的設計應用中,也是會出現資源不敷使用的情形。而所謂的不敷使用,並非是真的資源不足以滿足設計,而是在電路佈局上未進行最佳化所致。

所以此問題依然要透過EDA工具來解決,透過工具的輔助讓電路的配佈設計達到最佳化,使原本可能要用2顆FPGA晶片才能實現的電路,經過最佳化後只要1顆就可實現,或者6顆減成4顆、或3顆減成2顆等等。

第四,此一樣與大型複雜化設計有關,在高度複雜的電路設計中為了加速設計進度,通常須將整體晶片電路分拆成數個區塊,每個研發團隊就各自分配到的區塊進行設計,同時間多組設計團隊一起進行研發,最後再將各區塊合併成完整的電路。

然一個完整的大型複雜電路該如何進行區塊切割?如何切割才能達到最快的開發速度?或如何切割才能使分工的爭議減至最小、使驗證程序減至最少、使整合平順性達到最大,這些也都同樣要考驗設計工具及晶片專案主持者的能耐。

先進製程FPGA應用:晶片模擬驗證

先進製程(大型)FPGA晶片的應用非常廣,除了做為ASIC的代用品外,近年來還有許多新應用方式出現。

首先是用在新晶片開發時的邏輯功效驗證,過去沒有使用FPGA前,新晶片的新設計驗證多使用兩種方式進行驗證,一是使用EDA的模擬軟體,另一是進行晶片試製。不過這兩種方式各有優缺點,使用EDA模擬軟體的好處是成本低廉,但模擬的速度緩慢,使驗證時間拖長。相對的晶片試製可以快速模擬,但試製的成本高昂。

為何過去不用FPGA進行功效模擬驗證?原因是過去FPGA內的邏輯閘不夠多,要完整模擬一個新晶片需要使用許多顆FPGA晶片才成,然近年來FPGA積極使用先進製程,使其內部邏輯閘大增,模擬一顆新晶片只要若干顆FPGA即可,所以現在愈來愈多晶片開發業者使用FPGA晶片來模擬、驗證新晶片的設計功效,例如Cell處理器最初即是用6顆FPGA來模擬、驗證其設計。

使用FPGA進行模擬的好處是成本低於試製晶片,速度又快於模擬軟體,主要可取代晶片試製,事實上晶片試製不僅花錢也要花時間等待,須等候數個星期才能試製出晶片,而FPGA則是可立即驗證,有了FPGA後,EDA模擬軟體就更專注在局部模擬驗證,而非整體晶片的驗證,過去FPGA的邏輯閘不夠多時,也只能充作局部驗證之用。

先進製程FPGA應用:高效能運算

先進FPGA的另一個應用是高效能運算(High-Performance Computing)的加速,更直言即是超級電腦(Supercomputer)的科學性運算。

超級電腦多是用許多機櫃的電路所併成,且多半用來執行科學性的模擬,如氣候模擬、核子試爆模擬等等,這類型運算的特性是資料量龐大,但都使用同一種演算方式,且各筆資料的運算相互間沒有太大關連性,因此可平行運算,但仍需要極大的運算力才能在限定的時間內完成模擬運算,例如氣候模擬即是要提供晚間的天氣預報之用,必須在24小時內算出,若要3天時間才能算出,則該模擬就毫無意義。

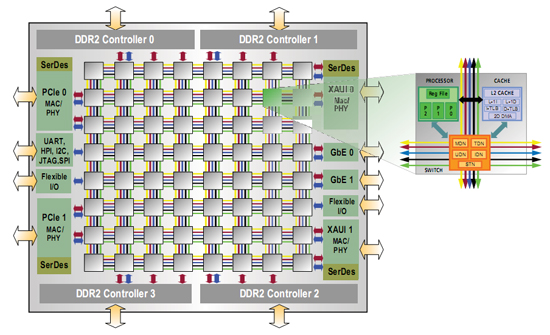

為了加速模擬運算,超級電腦開始使用大型FPGA,例如Cray Research在其XD1超級電腦內使用的RapidArray技術,就是使用FPGA來實現,FPGA在RapidArray技術中充當通訊處理器,讓超級電腦的各運算機櫃間的通訊傳遞更加快速。

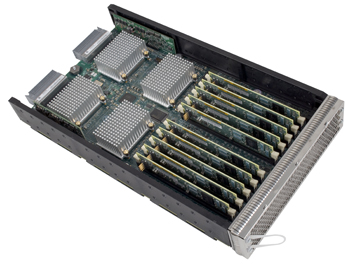

Cray的RapidArray主要在於加速超級電腦內的溝通傳遞,但不負責運算,而SGI(視算科技)的RASC(Reconfigurable Application-Specific Computing)則真的運用FPGA進行運算加速,SGI的RASC是一種加搭模組(稱為RC100 Blade),該模組直接加裝在SGI原有的超級電腦機櫃上,並使用SGI的NUMAlink 4介面與超級電腦相連。

模組中使用2顆Xilinx Virtex 4的FPGA,之後將超級電腦常用的函式(Function)轉化成FPGA可用的邏輯電路程式,再將程式載到FPGA內,往後超級電腦一有函式呼叫(Call)時,就直接改由RASC來運算函式,之後將結果傳回給超級電腦。此種方式與過去不使用FPGA,而是使用超級電腦內的CPU、記憶體來運算函式,至少快上數十倍效能,甚至達一百多倍的效能。

從效能加速來看FPGA確實效力驚人,但也並非全無缺點,要將常用的軟體函式改成FPGA可用的邏輯電路程式,這個轉化需要許多心力、時間,即便是擁有原始程式碼(高效運算屬研究領域,所執行的程式多由研究機構自行開發,因此多擁有原始程式碼)也需要很長時間,且任何一點小程式調修都要耗上數小時的時間,此方面有待更有效的轉化工具出現。

類似的,DRC Computer公司的Reconfigurable Processor Unit(RPU)也是相同,同樣是使用FPGA來加速高效運算,與SGI RASC的差別只在連接方式,RASC是以模組化的小型機箱附搭在原有超級電腦上,並用SGI獨家的NUMAlink 4進行連接,而RPU是以模組子卡(小型電路板)的方式直接插置在與AMD Opteron相容的CPU接座上。

先進製程FPGA應用:無線基地台

先進FPGA的第三種應用是無線基地台,過去基地台多半使用許多的數位信號處理器(DSP)來進行收發信號的傅立葉轉換(FFT)運算,且同時間需要多筆FFT運算,各FFT運算間屬高度平行、相依性低,此也適合用FPGA來進行運算。

為何過去用DSP運算,現在要改用FPGA運算?答案是價格效能比,過去FPGA尚未大型化、先進化發展前,以滿足無線基地台的運算需求為基準,用多顆DSP來滿足需求,其成本低於使用FPGA來滿足需求。

不過現在不同,FPGA內部邏輯閘、電路資源愈來愈豐沛後,一顆FPGA內可以同時規劃、執行多筆FFT運算,一顆FPGA等同於多顆DSP的FFT運算效能,且價格低於使用多顆DSP,因此已有基地台開始用FPGA來取代DSP,或與現有DSP並用。

結語

雖然大型FPGA的應用愈來愈廣泛,但不表示沒有隱憂,其中結構化ASIC(Structured ASIC)就對FPGA產生威脅,特別是結構化ASIC的功耗低於FPGA、速度快於FPGA,使許多晶片業者在確定晶片用量規模增加後,將逐漸放棄使用FPGA而改用結構化ASIC,同時也要求EDA盡可能提供FPGA轉化成Structured ASIC的工具。

另外多核化的處理器也對FPGA產生威脅,在此並非指AMD、Intel的2、4核處理器,而是指Cavium、RMI、TILERA等業者的8核、16核、64核處理器,這些多核處理器與FPGA相同,都極適合用在大量平行的運算中,且許多網通設備已經採用。

往未來看,大型FPGA將持續積極使用更先進的製程,持續增加晶片內的電路資源,但同時要對功耗進行收斂,及提升運作速度,如此才能確保前述各項新應用的運用價值。

| 《圖一 Xilinx的Vertex 5家族FPGA是高階FPGA,電路資源最多,因此多用最先進的半導體製程來生產。(圖片來源:Xilinx.com)》 |

|

| 《圖二 隨著半導體製程的不斷縮密,半導體光罩的費用也不斷飆漲,圖為IBM光罩技術中心(位在美國佛蒙特州的伯靈頓)的工程師正在端詳光罩的模樣。(圖片來源:www-03.ibm.com)》 |

|

| 《圖三 Cell處理器在設計階段,就使用FPGA來加速晶片邏輯功效驗證,總共使用6個FPGA來模擬整個Cell晶片的電路功效,圖為Cell實體裸晶與一般文具圖釘的體積比較。(圖片來源:www-03.ibm.com)》 |

|

| 《圖四 SGI的RASC RC100 Blade附加模組,散熱片下方即是FPGA晶片(Xilinx Virtex 4),右邊的記憶體模組則在FPGA運算時供FPGA存取之用。(圖片來源:sgi.com)》 |

|

| 《圖五 今日許多無線基地台機箱內的信號運算已從DSP改成FPGA,或在新加裝的模組電路板上使用FPGA,圖為台灣東訊公司的WiMAX基地台機箱:WM5071,該基地台使用了3組方位性天線。》 |

|

| 《圖六 TILERA的TILE64處理器,該處理器具有64個64位元的MIPS執行核心,適合網通運算、數位多媒體運算。(圖片來源:tilera.com)》 |

|