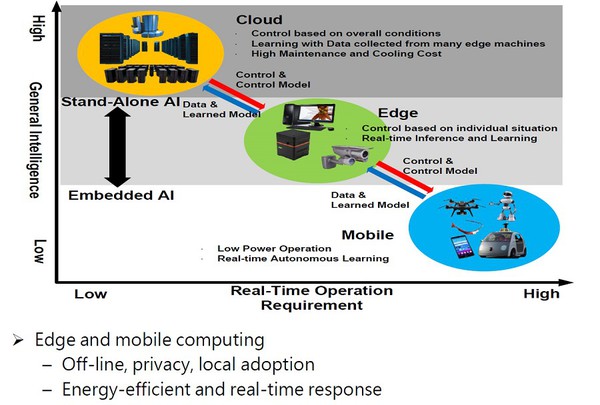

過去AI晶片幾乎是運用在雲端。不過,從2018年開始,出現了一個很大推波助瀾的效應,也就是說,Edge運算的出現,造就Edge端跟雲端有很大的差異。

5G時代來臨代表的是一個高頻通訊的概念,而人工智慧則是代表高度的概念,所以高頻和高度這2個名詞,將會是代表未來晶片的封裝技術在新一代的研發過程當中,所需要面對的挑戰。

過去AI晶片幾乎是運用在雲端,因此大多是掌握在Facebook、Amazon或是Google上,因此在AI晶片製程的技術與市場規模上面,並沒有太大的推動力。不過,從2018年開始,出現了一個很大推波助瀾的效應,也就是說,Edge運算的出現,造就Edge端跟雲端有很大的差異。

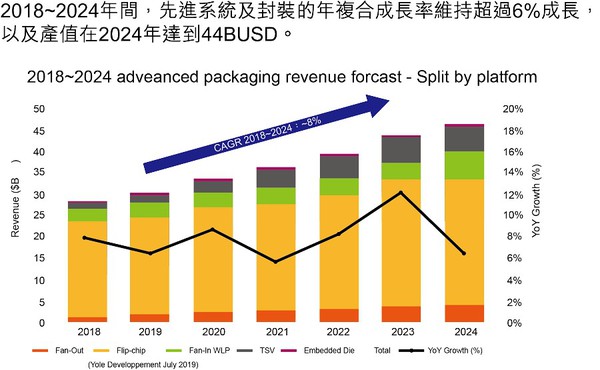

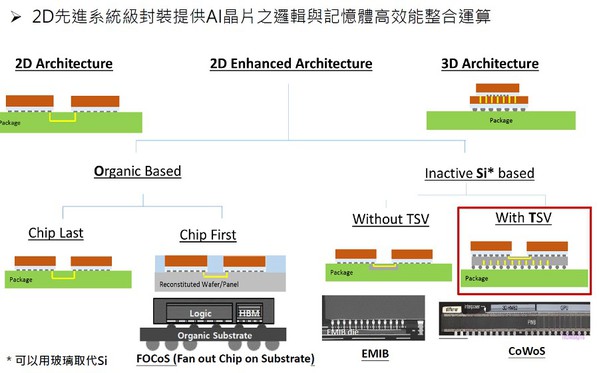

基於這樣的趨勢帶動之下,全球封測與晶圓廠都爭相開發高速運算晶片的封裝技術,例如透過邏輯及記憶體晶片整合在矽中介層上,來高晶片整合效能,並且利用晶片切割後再整合,來達到降低製程成本(圖1)。

| 圖1 : 先進封裝產值趨勢。(source:工研院,智動化整理) |

|

新到來的Edge市場 刺激新技術的研發

Edge端應用所帶來的挑戰和變化是,首先,在Edge端的市場裡通常AI晶片的單價不能太高,因為來自消費者市場階層的要求,不可能拿雲端的AI晶片在手機裡面,因為雲端的AI晶片價格最少一顆要1000美元,而目前高階手機的均價也都是在1000美元左右,所以不可以為了一支具有AI能力的手機,來加購一顆1000美元的AI晶片,所以晶片成本永遠是一個很重要的因素。

其次是,在Edge端會有耗電的問題,不像雲端的取電是經由市電或電源供應器,可以己乎永無止盡的獲得電力支援。因此對於Edge端所需的AI晶片耗電量就需要考量的。因此成本、耗電量跟體積這些事情,造就了面對新一代AI晶片的封裝呢,就不能用雲端的概念去思考(圖2)。

| 圖2 : AI運算從Cloud端到Edge端。(source:H-J Yoo(KAIST), ISSCC 2017) |

|

因此在面臨高速通訊與AI的需求來說,Edge端的市場結構必須和雲端的思考做一個切割,把跟Edge端獨立變成一個商業市場來看,但是要面對這樣的一個新到來的Edge端市場,就免不了又要出現數量、價格的競爭需求,以及被期待的龐大市場商機。所以可以發現吸引了台灣業者先後湧入開發相關的產品。

但是就目前來說,AI晶片有4大問題,首先AI晶片不是一個通用型,而僅是半通用的架構,需要面對各種不同的運用跟情境設定,因此AI晶片需要客製化。其次,內建的memory要更低的耗電能力,可攜式產品的運用情況之下,就會有電池供電的問題存在,因此你的記憶體就不能耗太多力量。第三就是如何將這些AI晶片記憶體、CPU甚至未來所需的感測器整合在一起,因為這是把不同的Node整合在一起,因此這對於封裝來說是一個很大的挑戰。

最後就是一個AI系統的軟體開發,因為AI的應用幾乎都是客製化,因此不可能為了每一個客製系統,去反覆修改、測試和調整,因此最佳的期望是在軟體的開發過程當中,就可以把各種條件和要求做出來,再確認這樣設計是可行的,才開始進行晶片的設計開發,進而縮短整個設計過程。

透過更先進的3D封裝技術來達到期望

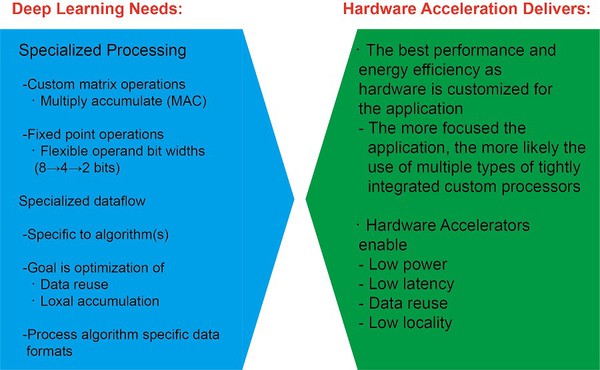

面對上述的種種問題,未來AI的硬體加速器會有幾個趨勢和要求,包括Low Power、Low Latency、Data Reuse和Data Locality。尤其是Low Power和Low Latency這2項就需要讓封裝業者花很多時間去解決(圖3)。

| 圖3 : AI硬體加速器需求 (source:工研院) |

|

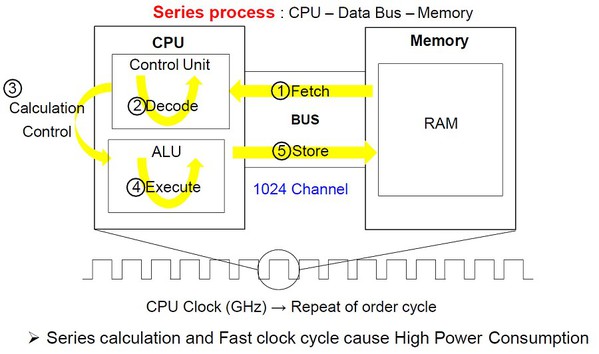

就Von-Neumann影像辨識架構AI晶片來看,在HPC裡面的系統需要置入CPU與Memory。當從CIS獲得影像之後,先存放到Memory,然後再去把原來放在裡面的資料取出,再送到GPU裡面進行 prediction後再回傳,如果比對有誤,就需要重新再找一筆資料,所以基本上來它的整個cycle是1到5的一個循環(圖4)。

| 圖4 : 利用逢紐曼架構產生高耗工運算(source:KAIST) |

|

基本上,需要1024個Channe個I/O來進行傳送。因此整個運算過程當中,需要這麼多的步驟被執行,假設能夠將功率消耗降低的話,才有辦法能夠讓資料量變快。對於以PCB與IC所設計出來的雲端AI系統來說,根本不會擔心電力問題,但是對於應用在可攜式產品上的EDGE來說,就沒辦法了。

因此必須透過更先進的3D封裝技術來達到期望,因為3D的話,晶片之間傳送的路徑最短,也就代表耗電量最低。但是,以目前的技術層次來說,3D基本上還有很多問題。因此,目前眾多業者仍舊把大部分的精力放在改善2.5D封裝技術上,透過各種方法來改善耗電量,然後能夠真正在可攜式產品端使用。對於這方面,目前TSMC和INTEL都有一些概念提出來,希望能夠解決這樣的問題跟成本。例如,TSMC提出了一個SoIC概念,而INTEL則是提出EMIB(圖5)。

| 圖5 : 多晶片異質整合SiP方式。(source:工研院) |

|

面對更高速的應用 AiP封裝技術正積極發展

因此相信在短時間的1、2年之內,會有很多2.5D、2.1D甚至2.XD被提出。所以基本上整體來看,其實都是因為運算所帶來的需求,前述的AI兩個大問題,一個是功耗,另一個是速度的問題。那速度的問題除了將配線做的更細之外,因為同時間要有更多的記憶體,所以Die的厚度會變的更薄,這就是一個大問題。

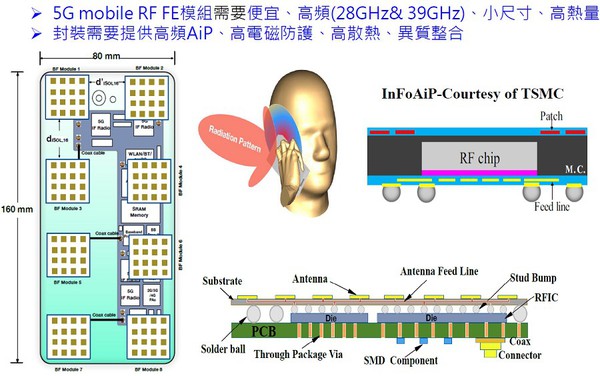

在晶片中Data的部分,因為5G的頻段比較高,因此呢它容易受到一些所相關的阻隔,因此在手機晶片設計上,晶片在封裝時都會加上AiP(Antennas in package),為什麼Antennas in package變成非常重視?這個因為基本上利用傳統的PCB沒有辦法實現天線的結構,所以才會利用封裝的Wafer Level Processes將天線置入,並且將天線縮小,因為現有的4G通訊環境之下只需要一個天線就夠了,一個大片的天線就可以進行訊號的傳送接受了,但是相對的呢整個功率跟能量的損耗會比較大。

不過,面對更高速的應用,就無法以目前的技術來因應,因此在最近這幾年全球的晶片業者都相當積極的開發AiP的封裝技術,就是因為在系統端面對28 GHz、38 GHz的頻段時,是無法利用single pattern的方式達到,所以一定要用陣列方式,但又無法放入封裝裡,因此這是一個很大的挑戰。

圖6是一個RF chip上面有天線,而另外一種較簡單用Fan Out的模式,把模封材料(Molding Compound)整個應用在AiP,但是高頻的情況之下會有電磁干擾,因此模封材料原先不是用來做電磁干擾,只是用來做保護。

| 圖6 : 因5G帶動的RF FE模組新需求。(資料來源:工研院) |

|

封裝從DIP等技術開始, 模封材料本來的責任就是指要保護晶片不要受到外面的傷害,但是到現在,不僅僅保護的功能還能在上面做線路的置劃。在這種情況之下,模封材料現在責任越來越大,以前只是配角,但是現在已經快變成主角,因為有很多的應用都會利用模封材料來當作一個載板,以及高頻的隔離和散熱,所以呢對於整個來說,因為新的需求,所以模封材料會有一個很大的挑戰。