於本周举行的2023年IEEE国际内连技术会议(IITC)上,比利时微电子研究中心(imec)展示其实验成果,首次证实导体薄膜的电阻在12寸矽晶圆上可超越目前业界使用的金属导线材料铜(Cu)和??(Ru)。例如,厚度为7.7奈米的镍铝二元合金在经过晶粒工程後,可测得的最低电阻为11.5μWcm。这些研究成果是在线宽10奈米以下实现低电阻内连技术的里程碑。

|

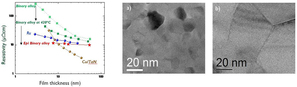

| (左)在不同制程条件下沉积镍铝合金(NiAl)的电阻值,并与铜材及物理气相沉积法制成的??金属进行基准测试。红色星形所标示的是7.7奈米二元合金磊晶薄膜所测得的最低电阻,其在50奈米薄膜上沉积并随後进行薄化。 |

为了跟上元件微缩的进度,先进逻辑与记忆体晶片的最小线宽很快就会接近10奈米。在这种微缩尺寸下,铜材的电阻会急遽升高,可靠度也随之下滑,迫使内连技术研发人员去寻找替代铜材的导线材料。最初的开发重点是金属元素,但後来逐渐延伸到二元及三元有序介金属。这些研究在2018年IEEE国际内连技术会议(IITC)由imec先行展开。

imec透过建立一套基於第一原理(ab initio)计算的独特方法来拣选最具发展潜能的材料,并以块材电阻与电荷载子平均自由路径(mean free path)(r0 xl)的乘积为主要的品质因子(FOM)来排序分级。这套基於理论的性能评估是後续在12寸晶圆上进行技术实验的开端。imec研究员暨奈米导线研究计画主持人Zsolt T?kei表示:「为了深入了解这些选定的二元合金材料在小尺寸下的电阻表现并为其建模,我们在2023年IEEE国际内连技术会议(IITC)上提出一种有效电阻率,考量了合金成分变化及有序和无序材料所带来的影响。进一步分析後发现,由於导体薄膜本身的晶粒尺寸小,所以二元合金薄膜的电阻主要受到晶界散射影响,而无序结构也会增加薄膜厚度。」

在一项镍铝合金(NiAl)的化学计量研究中,7.7奈米的薄膜经过测量後,电阻最低可达11.5μWcm,比铜材还低了23%。其做法是在後段制程容许的操作温度下,在诌(Ge)磊晶层上沉积一层50奈米的大粒径镍铝薄膜,然後进行薄化实验。这些实验留用较大的粒径(45.7奈米),所以能减缓晶界散射对电阻的影响。Zsolt T?kei表示:「这项实验展示了在12寸晶圆上制造导体薄膜可以达到低电阻值,进而推动我们持续探索二元及三元合金作为导线材料。同时,我们也在研究这些合金的成分控制,以及未来整合至导线蚀刻制程的相容性。」

imec将在今年IEEE国际内连技术会议(IITC)举行10场讲座,探讨内连微缩技术的主要挑战。此次发表的论文除了两篇有关替代金属材料(其中一篇为受邀发表),其它内容聚焦先进内连堆叠的半镶嵌导线制程、可靠度、热效应,以及中段导线制程等。