由國際光學工程學會(SPIE)舉辦的2023年先進微影成形技術會議(2023 Advanced Lithography and Patterning Conference)上,比利時微電子研究中心(imec)展示了一套先進IC圖形化製程的環境影響量化評估方案。在imec.netzero模擬平台上開發了一座虛擬晶圓廠。利用該平台的分析結果,imec與其夥伴就能評估現有的製程方案,識別開發的重點領域,並推算未來數據。

|

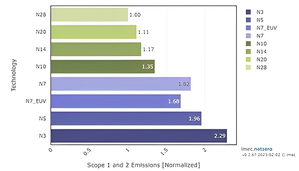

| imec.netzero模擬平台針對不同邏輯晶片世代的每片晶圓碳排量進行分析的結果。值得注意的是,7奈米製程引進EUV技術,透過精簡多道製程步驟,成功減少碳排。 |

imec在其實體晶圓廠探索各式高影響力(high impact)領域的環境友善製程方案,包含減少使用含氟的蝕刻氣體,致力於極紫外光(EUV)曝光機的產量最大化,以及減少氫氣用量與用水。

IC製造所衍生的二氧化碳排放量預計在未來10年翻漲4倍,一來先進製程技術漸趨複雜,二來晶圓總產量估計會增加。為了逆轉未來局勢,領先業界的半導體大廠已經承諾在2030年~2050年前達到碳中和或淨零。有鑑於此,imec啟動了永續半導體技術與系統(Sustainable Semiconductor Technologies and Systems)研究計畫,廣邀半導體供應鏈以晶片製造的淨零碳排為發展目標。該計畫的其中一項目標是提供業界一套獨到的由下而上(bottom-up)設計方法,提供可付諸行動的高度細化資料,以便在製程與流程開發階段進行影響評估。

imec.netzero模擬平台是這項計畫的產物,imec與其夥伴合作,利用該平台,首次成功量化不同邏輯晶片世代的圖形化製程所帶來的環境影響。imec技術研究主任Emily Gallagher解釋:「透過應用『虛擬晶圓廠』這項工具,我們展示了生產3奈米邏輯晶圓的微影與蝕刻製程,在範疇1(自有或自行操作資產的直接碳排)與範疇2(外購電力的間接碳排)的碳排佔比共達45%。另外,該模擬工具還能在晶圓廠實際操作實驗時量化收益。舉例來說,減少10%的EUV曝光劑量,相當於每片晶圓減少0.4kg的二氧化碳排放量。這能為大型晶圓廠省下每月40噸的二氧化碳排放量,等同於美國舊金山與波特蘭來回飛行100趟的碳排量。

imec將自有的實體晶圓廠作為試驗環境,從而探索高影響力領域的製程與設計方針。Emily Gallagher表示:「我們與愛德華先進科技(Edwards)合作,近期在我們的12吋晶圓廠無塵室架設了一套EUV蝕刻的氫氣回收系統,最多能回收與再利用70%的氫氣。此外,我們越來越專注在開發數值孔徑為0.33與0.55的低劑量EUV蝕刻解決方案,藉此降低蝕刻成本。為了強化永續發展,我們也指明蝕刻技術的未來動向,目前焦點放在降低傳統蝕刻氣體的整體消耗量。接下來,我們將攜手合作夥伴來量化分析上述解決方案對半導體製程完整流程的影響。

imec先進圖形化製程與材料研究計畫的研發VP Steven Scheer表示:「過去開發的圖形化技術是掀起半導體革命的主要成因,為了趕上對運算效能不斷升級的需求成長幅度,持續改良至關重要。要在訂定減碳策略的同時,維持圖形化技術的水準,勢必要付出許多努力,現在我們立下了第一座里程碑。在imec.netzero模擬平台上開發的模型經由設備與材料廠商不斷進行基準測試與驗證。這些廠商扮演關鍵要角,除了推行SSTS先導計畫,還能強化可行的圖形化解決方案,以減少全球半導體業的碳足跡與環境影響。」

Steven Scheer接著補充:?我們也注意到碳排當量(carbon equivalent emissision)的計算方法並不包含碳排對環境的所有影響。例如,排放氣體可能是有害空氣汙染物(HAPS),而光阻劑與抗反射鍍膜(ARC)皆含有全氟與多氟烷基物質(PFAS) 。這些物質的碳氟鍵結強度提供化學放大阻劑(chemically amplified resist)優異的微影特性,包含發展成熟的光學微影光阻劑與持續發展的EUV光阻劑。然而,由於其潛在的生物累積特性,社會因此亟欲禁用PFAS。除了直接降低碳排,禁用PFAS的研究計畫也應納入考量。