自摩爾定律提出後,晶片製程便不斷快速的向下加壓,企圖在短時間內於單一晶粒(Die)中創造出更多的電晶體數量,同時延伸出整合度更高的晶片設計。在兩年前,市場的主流製程為0.13微米,但先進製程已發展至90、甚至是65奈米,而如今,0.13微米的產品以逐漸退出市場,90及65奈米將成為市場的老大,但肩負效能先鋒的邏輯晶片和記憶體晶片卻已前進至45奈米製程,甚至將在今年年底前,把製程一舉推至32奈米。

製程細微化之後,不單只晶片開發者面臨嚴峻的考驗,代工廠與設備業者也同樣備感壓力。包含曝光、蝕刻、成膜、濺鍍等製程技術,都必須再提高一個檔次,同時要避免過高的失敗率。因此,要有能力量產一個先進製程的產品,將變得愈來愈困難。為了解決新一代先進製程所帶來的種種問題,EDA工具商也嘗試透過新工具的提出和設計工具的強化,來協助客戶渡過製程挑戰,順利導入量產並提高獲利。

因應45奈米以下製程 配置與繞線技術再翻新

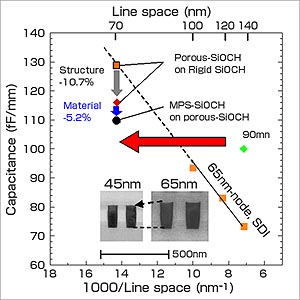

在晶片製程進入奈米之後,有很大的挑戰是來自晶圓材料的問題,尤其是65以下的製程,如何突破物理極限成為當時的主要命題。但隨著High K材料的提出,以及相關生產設備漸趨成熟,半導體業者也順利的過度到65奈米製程。但進入45奈米或32奈米製程時,材料的極限將再次受到考驗,而生產和設計技術的挑戰也面臨新的難關。包括多通道結構(Multi Channel)、變形通道、金屬閘道(Metal Gate)的應用等,這些挑戰都將增加後段實體設計和佈局與繞線(Place and Route, P&R)的困難度。

由於45奈米以下製程的電路設計已非常細微,很容易在製造過程中造成連線變異,讓良率與電路效能大受影響。因此,如何在實體設計中,降低因製程變異的錯誤,並以有效的P&R技術增加設計效能,是目前設計人員最重要的課題。對此,EDA業者也提出新的繞線工具,來因應此一需求。

| 《圖一 進入45奈米製程之後,電路設計已非常細微,很容易在製造過程中造成連線變異,讓良率與電路效能大受影響(資料來源:NEC)》 |

|

為了解決先進製程的繞線問題,新思科技(Sysnopsys)推出了Design Compiler Graphical工具,該產品是業界首款可在設計初期預測電路組塞熱點(circuit congestion hot spot)的合成解決方案。它能將有問題的電路區域影像化,並針對這些區域提供合成最佳解決方案(synthesis optimization)來降低組塞,使得設計者在實體實作(physical implementation)前,幅降低synthesis與P&R的重複執行(iterations),達到縮短設計時程和降低成本的目標。

日前新思科技又為其IC Compiler增加一項能執行多執行緒(multi-threaded)的繞線工具Zroute,以支援在多核心微處理器架構的設計工作,及DFM的需求。

目前,微處理器與一些應用在消費或通訊領域的元件,是採用65甚至45奈米先進製程的主要驅動力。新思科技Implementation Group產品行銷經理Marco Casale-Rossi表示,當製程節點降至45奈米以下時,從IC設計階段開始就面臨極艱鉅的挑戰,而Zroute就是解決先進製程中設計難題的一種解決方案。他指出,在45奈米製程時,晶片中各金屬層之間透過穿孔(Via)連接的連線變得極細,若在每條Net上透過繞線將Via數量降低,則Net的性能將大幅提升,也能改善晶片失敗率並改善效能。

| 《圖二 新思科技產品行銷經理Marco Casale-Rossi表示,當製程節點降至45奈米以下時,從IC設計階段開始就面臨極艱鉅的挑戰。》 |

|

Magma台灣區總經理黃正年博士則表示,晶片設計進入40或者30奈米的挑戰,與進入65奈米的挑戰是大同小異,都會面臨良率與時程的困難。要改善這些困難,必須從整體的流程和架構著手,在前段就要有所考量,才能讓後段設計順利。而Magma主要是針對後段的設計提供解決方案,他指出,Magma是以數位起家,堅持單一引擎、單一模組的P&R技術,在高階的晶片設計上有絕佳的效能,加上支援多電腦的運算,對於大規模的晶片設計有很快的運算速度,尤其是針對先進奈米製程的設計,能達到更短的上市時程、更佳的產品性能。

良率與成本加倍緊縮 DFM工具應用吃重

在晶片製程導入90/65奈米時,由於設計複雜度與物理極限所延伸的問題變得嚴重,使得原先的修正與驗證流程不足以全然適用,必須在IC設計端便要考慮量產的問題,因此DFM的觀念便被提出,而EDA工具商也與晶圓廠進行積極合作,開發出一系列的DFM設計工具,以因應奈米世代的量產問題。如今製程再下探40奈米時,DFM的重要性更形加劇,包含晶圓廠以及晶片設計者,都必須有一套DFM的工具應用,才能有效率的導入量產。

然而,在進行90/65奈米設計時,DFM的應用固然重要,但部份的晶片商並不會全盤的導入DFM工具,主要的原因是採用DFM也需付出一定的成本,在權宜相較之下,大規模的採用DFM並沒有明顯的成本優勢。但製程進入40奈米之後,DFM則成了成敗關鍵。根據統計,一個90奈米的晶片設計成本約2,000萬美元,65奈米的設計成本則為4,500萬美元,而45奈米及32奈米的設計成本便高達7,500萬美元以上,因此,投入一個先進製程的晶片設計專案幾乎是禁不起失敗的考驗,再加上上市時程的考量,如何能夠在最短的時間內達成最高的良率,幾乎是決定產品生死的法則。居於這樣的需求,DFM的工具應用將會更加全面性。

| 《圖三 台灣總經理黃正年也表示,DFM的重要性在進入40奈米以下將會更加明顯。》 |

|

新思科技近日發表的Zroute工具便加入了DFM的應用,讓設計者在進行繞線設計時,便有DFM的支援。Casale-Rossi表示,如果將一個晶片設計在自然原始、沒有人為干預的情況下進行生產的話,那良率是零,不會有任何可用的晶粒。因此,在設計時便考慮量產是非常必要的,尤其是在40奈米以下的製程。Magma台灣總經理黃正年也表示,DFM的重要性在進入40奈米以下將會更加明顯,尤其是在實體層的設計上會有許多的問題,設計者必須在Net List上就開始做考量。至於晶圓廠的部份也必須結合EDA工具,建立一套共用的生產流程。

晶圓廠的方面,為了因應40奈米以下的生產需求,台積電也在日前推出適用32奈米以下晶片設計的可製造性設計統一架構(UDFM),以提高客戶生產良率並降低成本,同時加速上市時程。台積表示,UDFM架構是台積電的開放創新平台(OIP)中的要素之一,由台積電與其EDA工具商以及其他合作夥伴所協同開發,以協助客戶提早晶片上市時程,提升投資效益。

而台積電新版的設計參考流程9.0版中,也大幅提升了DFM的應用。其增加了物理層級及電子層級可製造性設計功能(Physical and Electrical DFM Capability),能夠加速大型晶片設計的DFM分析以及參數效能影響(Parametric Performance Shift)的評估。同時,並針對所有物理層級DFM效應,包括曝光顯影製程檢查(Lithography Process Check,LPC)、化學機械研磨(CMP)與關鍵區域分析(Critical Area Analysis,CAA),提供層階架構DFM分析,能夠大幅減少設計的反覆運算、加速DFM分析,增加設計的精確度。

低功耗設計成主流 CPF/UPF應聲而起

近年來,由於環保意識抬頭以及可攜式裝置的普及,讓消費者市場對於產品的電耗有了更進一步的要求,而因應此趨勢,晶片開發商也不斷的著手低功耗晶片的設計,尤其當製程進入90奈米之後,漏電的問題日益嚴重,CMOS靜態功耗也倍增,同樣的問題在65奈米與45奈米以下將更顯嚴重。由於製程的細微化將導致柵極氧化層厚度越來越薄,柵極漏電指數隨之增加,造成動態功耗也受影響,因此,設計者必須從IC設計端就開始採用低功耗設計技術,並具備系統設計的整體思維。而身為晶片設計上游的EDA工具商,也開始針對客戶的需求提出了數款低功耗設計工具,其中UPF與CPF標準的應用則是目前低功耗設計的兩大熱門。

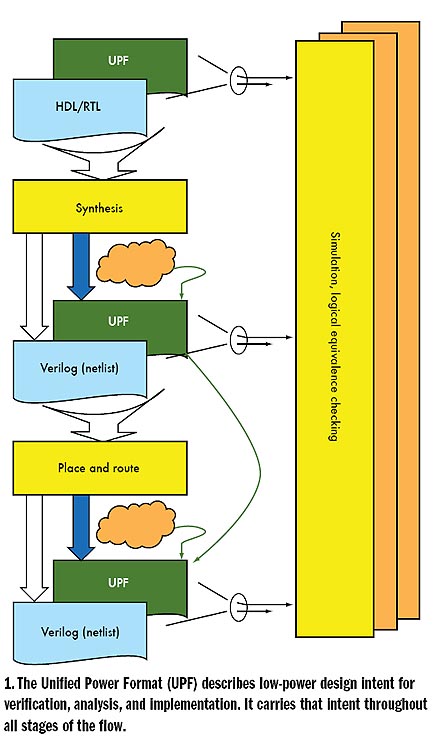

| 《圖四 UPF標準從設計、驗證、實作到分析等各階段全面涉入,從整體系統端的進行低功耗的開發。》 |

|

在低功耗設計中,功率閘控(power gating)技術是目前最熱門的解決方案,EDA 供應商也不斷積極的在研發功率閘控的自動化技術,而統一功率格式(Unified Power Format,UPF)和公用功率格式(Common Power Format,CPF),也都是幫助設計者更有效地實現功率閘控的方法。

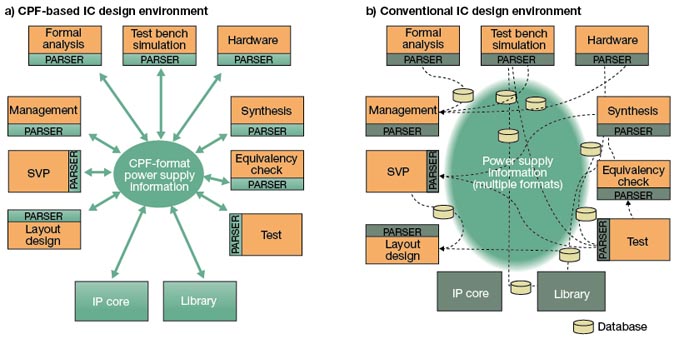

UPF標準是由Accellera所發展低功耗標準,目前由新思科技、捷碼科技及明導國際(Mentor Graphics)所支持,日前三家也共同宣佈推出符合UPF 1.0的低功率EDA解決方案。新的UPF產品不但提高工具的低功率效能,也強化了相互間的操作性。而CPF標準是由益華(Cadence)所主導,是在設計初期詳細定義低功耗技術的標準化格式,透過在整個設計過程中保存低功耗設計意圖,降低費力的人工作業,並在設計初期提供功耗的可預測性。

| 《圖五 CPF標準是由益華所主導,是在設計初期詳細定義低功耗技術的標準化格式,降低費力的人工作業,並在設計初期提供功耗的可預測性。》 - BigPic:678x343 |

|

新思科技新推出的低功耗設計解決方案「Synopsys Eclypse」。是針對系統級(System Level)低功耗需求的晶片設計開發,提供驗證、實作、簽核、智財、設計方法及設計服務等支援,該工具也全面支援統一功率格式標準UPF(Unified Power Format)語言,讓設計支援具備更佳的彈性。而Magma的Talus Power 和 Quartz Rail也是符合UPF的低功率積體電路實施和分析產品。該產品能夠有效降低奈米級晶片的功率損耗,節省率高達25%,而採用Talus實施平台的獨特結構相整合的新功能,可度量性以及自動化等特性,使得設計師們能夠有效縮短開發規模為數百萬門極的低功率奈米設計的時間。

而益華電腦也在去年時推出了第一套的整合式低電耗解決方案。該工具是以Si2標準的CPF為基礎,專用於低功耗晶片的邏輯設計、驗證和實現整體設計解決方案,涵蓋multiple power domains、multi-voltage、multi-Vt、power shut-off與retention。透過在CPF標準中,建立一個設計功耗意圖的單一表示法,促進了IP複用和RTL輕便性。該解決方案已獲得虹晶科技、聯華電子與創意電子的採用,並運用在先進的65奈米投產上。

Magma黃正年表示,低功耗設計是EDA工具的發展重點之一,未來的應用比重會逐漸提高。尤其是進入65奈米之後,不久使用UPF或CPF規格的產品就會陸續面市,並帶進更多的客戶使用相關技術。

混合訊號晶片市場火熱 整合式設計平台問世

隨著裝置輕薄短小和多功整合的發展趨勢,SoC晶片的應用比例也與日俱增。而在SoC設計技術當中,最困難的部份就是將類比功能與數位功能放進一個晶片系統中。因此,在進行類比晶片設計時,就需要一個能模擬此混合晶片的數位類比混合信號電路模擬和佈局設計軟體。加上目前光電、無線通訊及3C消費市場火熱,高性能的混合晶片需求也水漲船高,連帶促使混合信號的EDA工具備受市場關注。

| 《圖六 SoC設計技術當中,最困難的部份就是將類比功能與數位功能放進一個晶片系統中。》 |

|

在手機晶片市場具有九成市佔率的捷碼,其在高階晶片的開發上擁有強大的實力。由於看好混合信號晶片市場的發展,也整合了旗下的類比設計工具,並在年初推出了第一款全晶片級混合信號設計、分析以及校驗平台Titan。不同於其他的EDA工具商僅有獨立且分散的類比設計工具,捷碼的Titan平台將混合信號實施方案與數位實施(digital implementation)、電路模擬(circuit simulation)、晶體管級提取(transistor-level extraction)以及校驗整合在一起,改進了類比晶片開發者的效率和生產方式。

Titan同樣使用捷碼的統一數據模型,並與與捷碼Talus數位IC實施、FineSim Pro電路模擬、QuickCap TLx晶體管級提取以及Quartz DRC和Quartz LVS物理驗証產品一同運作。能讓類比和數位設計團隊一同工作,並對彼此的設計領域有清晰的了解。捷碼執行長Rajeev Madhavan先生表示,過去類比設計最大的問題就是沒有辦法做到「IP reuse」和「Design reuse」,導致設計時程相當冗長,一個完整的類比設計流程時約要耗費9~12個月,不符合市場需求。而Titan平台提供自動化的晶片完工修整功能,能將混合訊號平面電路圖與Talus的佈線功能整合,大幅縮短開發的時間。加上Titan支援多電腦多CPU的運算方式,處理大型的電路設計也具有極佳的效率。以一個含有800百萬個電晶體的設計為例,全晶片的展開只要4分鐘,重新規劃電路只要8秒鐘,較其他對手快10倍~50倍左右。

| 《圖七 捷碼執行長Rajeev Madhavan 先生表示,過去類比設計最大的問題就是沒有辦法做到「IP reuse」和「Design reuse」,導致設計時程相當冗長,不符合市場需求。》 |

|

Madhavan表示,Titan是目前市場上唯一的混合信號開發平台,能利用數位的方法去修改類比的問題,加上具備絕佳的性能,對於先進製程的晶片設計非常有利。而為了推廣Titan平台,目前捷碼也積極的與全球的晶圓廠合作,將鎖定45奈米製程以下的設計方案為主。黃正年也表示,Titan不論在數位或類比的設計上,都堅持以單一模組和單一引擎的形式,在整合與效能上十分有優勢,加上具備優良的人機介面,在開發上也十分容易上手。