TSV製程關鍵名詞解析

穿晶片孔(Through Chip Via; TCV)

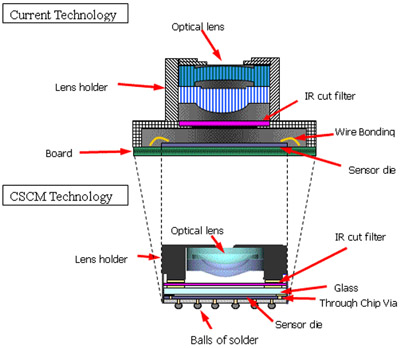

此為Toshiba在其chip scale camera module(CSCM)技術中用到的名詞(圖一)。此技術就是為了設計3D CIS。

《圖一 Toshiba 的chip scale camera module (CSCM)技術》  |

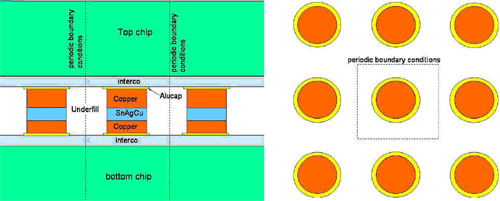

晶片間穿孔 (Interchip via; ICV)

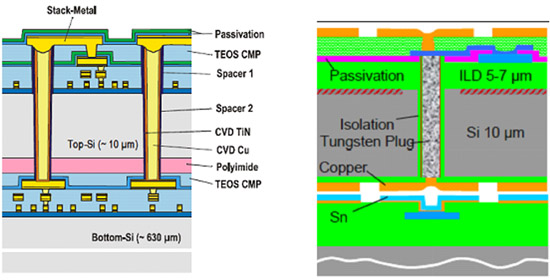

@內文:此為IZM 1998至2009年名詞。通常與ICV-SLID (Inter-Chip Via Solid Liquid Inter-Diffusion)合用(圖二)。ICV 的意思是 Inter-Chip Vias, 也就是從最上層的 TEOS 挖孔到最下層的TEOS,這也是一種 TSV 技術,而 SLID 是透過Cu-Sn間的相互擴散到到黏合效果,用來作電器與機械的相連之用,也就是當電器可以相連的時候,這些接點也是有一定的應力可以粘住兩個晶元。

《圖二 Fraunhofer IZM 的 ICV 技術(左)與SLID 技術(右)》

|

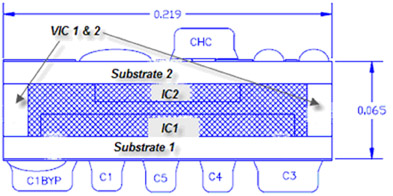

垂直連線 (Vertical Interconnect; VIC)

這個名詞不是在說TSV,是1997 年的時候美國Starkey 實驗室的名詞。當初是為了一個耳內(in-the-ear; ITE)的助聽器所設計的一個三維封裝內的一個垂直導線技術。如圖 3是Starkey 以MCM 技術所設計的ITE 助聽器,雖然是MCM ,但是其封裝是立體的。垂直的導線也不是 TSV。當然依造這個架構,TSV 技術可以使其封裝的體積更小。

《圖三 Starkey 第一個3D 封裝的助聽器(1997)》  |

打線孔 (Bond Vias)

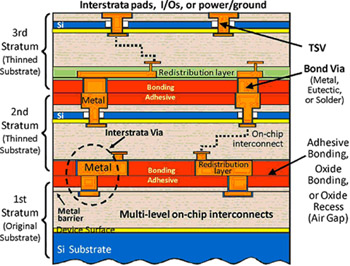

此為 2009 年 ,Rensselaer Polytechnic Institute (RPI) 教授 James Lu 的名詞。首先,RPI 對於Via-Last製程的TSV就分為Plug TSV 與Bridge TSV 兩種(如圖 4)。Plug TSV 看來是一個TSV 與該層的元件有所接觸,而Bridge TSV 僅是做訊號線的穿越,也就是如同 SOC 繞線中常談到的Feed Through。Via-First 的製程中(圖 5),出現了Bond Via這個名詞,這個名詞不是為了替換TSV,反而是用以跟TSV 區隔,因為,RPI 的Via-First 3D 整合技術中,需要在鍵合層做出類似 「挖洞」的動作。傳統「兩層中間的層」(interstrata layer)上不會挖洞,而是先將柱子做好,然後外部的Adhesive 再包住這個柱子,但是RPI 看來是用 TSV 的技術在Adhesive 上面挖洞。因為根據文獻,這個Bond Via 也包含了Isolation Layer, Barrier/Liner Layer, 與Seed Layer,填孔的金屬則用金屬鍵合(metal)、共晶鍵合(Eutectic)或者是利用錫鉛凸塊(solder)的方式填入。這個名詞的確很有意思,因為,這個名詞結合了原有打線(bonding wire) 的bond與挖洞 的 via兩個名詞。理論上,打線就不是Via,既然挖洞了就不會是用bonding wire。所以他們強調,這個 Via 是透過Boding 所創造出來的。

《圖四 RPI 的Plug Via 與Bridge Via 》  |

《圖五 RPI 的TSV 與 Bond Via 關聯圖》  |

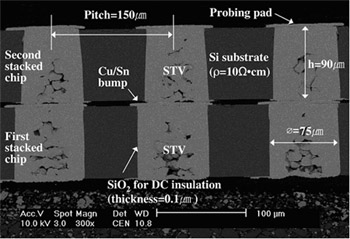

矽穿孔 (Silicon Through via; STV)

此為IBM 在 JSSC 2006、韓國KAIST 在2007 年與 IBM 在 DAC 2008 的名詞。圖 七是KAIST 為了抑制一般數位電路中常看到的SSN (Simultaneous Switching Noise)與減少PDN (Power Distribution Network) 的電阻所發展的3D IC,可以看到STV 就是我們所謂的TSV。這個銅STV 大小為75um、高度為90um、間距則為150um。

《圖六 韓國KAIST 的STV 觀念》  |

矽穿孔/堆疊 (Thru Silicon Via/Stacking; TSV/TSS)

這是Qualcomm 在2008 SEMICON Taiwan 的名詞。名詞都一樣,只是多了一個TSS 說明堆疊的事情。

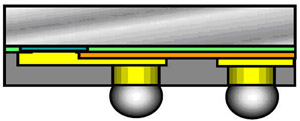

銅柱 (Cu Pillar/Cu Post)

這個名詞並不是在說明TSV,而是ST (2009) 說明上下兩個Chip 透過 Cu-Cu 鍵結後所形成的類似柱狀結構(圖七)。

《圖七 ST 的Cu Pillar 示意圖 (2009) (Source: ST)》

|

銅樁 (Cu Post)

這個名詞也不是TSV 的名詞,ITRS 與INEMI 2009 都曾經用過這個名詞,用以說明WL-CSP 的Bumping 結構。也是 Univ. of Arkansa 的名詞。

《圖八 IRTS/iNEMI 的Cu Post 示意圖 (2009) (Source: iNEMI) 》  |

結論

由上面幾個不同的TSV 名詞可知:

●TSV 是3D Integration 其中的一種可用的連線方式,它並不是唯一。

●不ㄧ定要Through Silicon,也可以Through GaAS,也可以Through interposer 或者是Through interstrata layer

●過程中的Via formation 並沒有「Through」(貫穿),而是只是有一個洞而已,這個洞稱之為盲洞(blind via)。

●挖洞並不ㄧ定要有「挖」的動作,其實早在 1992 年休斯公司為了軍事需求所設計的 3-D VLSI Computer,所用的技術與TSV 很像,但是並不是用挖孔的方式,卻是用「conductive vias through the silicon wafer」的方式,單純稱之為「feedthrough」,這種孔也是穿越過矽晶片,但是,卻不是用「外力挖洞」的方式,而是利用晶圓片上溫度的差異,使 鋁原子具有熱移動能力(thermal migration) 能力,將上層的鋁顆粒(AL drop) 金屬融入到晶圓片後貫穿出晶圓片。

●光是有TSV 也不能連接上下兩層晶圓,必須透過RDL 或者是Bonding 層內的繞線。

●TSV 不一定是在晶圓內部,也有可能是在Interposer 上。

●同一片晶圓上的TSV 的尺寸大小可能不一。