隨著晶片製造商持續推動技術世代演進,要維持前段製程(FEOL)電晶體微縮、中段(MOL)與後段製程(BEOL)接點與導線技術一貫的開發時程,也變得充滿挑戰。愛美科CMOS元件技術研究計畫主持人Naoto Horguchi、奈米導線研究計畫主持人Zsolt Tokei彙整各自的領域專長,將於本文一同呈現先進製程技術的發展藍圖。

本文將依照微縮技術的發展途徑,介紹前段製程中的全新元件架構,以及中段與後段製程中的新穎材料與整合方案,也會討論這些開發技術各自的市場現況、技術挑戰與原理。這些多元的微縮技術提供了晶片市場邁向1nm世代一條可能的通路。

邏輯晶片的要素:FEOL、BEOL、MOL

先進邏輯晶片的製造可細分成三大部分:前段製程(the front-end-of-line;FEOL)、中段製程(the middle-of-line;MOL)與後段製程(the back-end-of-line;BEOL)。

前段製程包含處理晶片中的有源元件,也就是位於晶片底部的電晶體。電晶體當作控制電流的開關,透過三個電極運作;閘極(gate)、源極(source)與汲極(drain)。源極與汲極之間的導通通道電流可以切換開關,轉換工作則由閘極電壓控制。

後段製程,亦即晶片製造的最後階段,指的是處理晶片最上層的互連導線。互連導線是分佈時脈與其他訊號的複雜配線圖,提供電源、接地,並傳送電晶體之間的電訊號。後段製程在不同金屬層中進行佈線,包括局部導線(Mx,其中x指的是金屬層的排序)、中間導線、半全局導線與全局導線。總層數可高達15層,但通常Mx層數介於3~6層。每層金屬層都有(單向的)金屬導線以及介電材料—導線透過規律的軌道(track)進行佈局。金屬層之間以通孔(via)垂直互連,而通孔以金屬填充。

前段與後段製程以中段製程相接。中段製程通常由微型金屬結構組成,作為電晶體源極、汲極與閘極的接點。這些微型結構連至後段製程的局部導線層。儘管元件尺寸持續微縮,用來連接的接腳數大致上仍維持不變,也就是說要將導線連至接腳變得更具挑戰。

隨著元件持續微縮至3nm甚至更小,處理上述各段製程模組的諸多挑戰隨之而來,這也迫使晶片製造商在前段製程中採用全新的元件架構,並在後段與中段製程嘗試新興材料與整合方案。

本文展示了愛美科對微縮製程技術藍圖的看法,並深入探討多種開發選項。以最尖端的主流前段、後段與中段製程技術為開端,筆者接著逐一介紹前端製程的嶄新元件架構,也就是環繞閘極(gate-all-around;GAA)奈米片(nanosheet)、叉型片(forksheet)、互補式場效電晶體(complementary field effect transistor;CFET)元件。

這些架構將直接影響局部導線層,因此後段製程需要新興材料,像是釕(Ru)、鉬(Mo)與其他金屬合金,還需要全新的整合方案,也就是混合金屬佈線(hybrid metallization)、半鑲嵌(semi-damascene)製程,以及「併合通道高度零通孔」(hybrid-height with zero via;H2 with zero via)架構。

在這條令人振奮的開發道路上,本文也將介紹一些透過元件結構來加速微縮進展的技術,例如自對準閘極接點(self-aligned gate contact;SAGC)與埋入式電源軌(buried power rail;BPR),這些加速器有助於優化中段製程的連接性(connectivity),也將藉由降低局部互連導線層中的金屬軌道數,來縮小標準元件尺寸—這被稱作軌道高度微縮化(track height scaling)。

先進主流技術與它們的微縮瓶頸

前段製程:FinFET發展

根據摩爾定律,電晶體的尺寸會每兩年微縮0.7倍。為了保持微縮步調,半導體業從「昔日美好的」平面MOSFET技術中淡出,幾年前開始改用鰭型場效電晶體(FinFET)結構。在FinFET架構中,源極與汲極之間的通道為鰭型,而閘極環繞著該3D通道,從三個面向進行控制。此多通道架構能消弭短通道效應,避免電晶體的效能隨著閘極長度縮短而降低。

2012年,首款商用22nm FinFET問世,此後,該架構進行改良,以強化性能並降低尺寸。舉例來說,鰭型通道高度增加了,為的就是在相同焊裝面積下提高元件的驅動電流。目前業界已生產出「內建」FinFET架構的7nm晶片。就最新技術節點的元件而言,高度為6軌的標準元件每元件的鰭型通道數為兩個以下,接點間距則小至57nm。這裡所說的6軌,指的是在元件高度內容納六條金屬導線。

後段製程:銅雙鑲嵌與鈷雙鑲嵌技術

為了趕上前段製程的微縮進度,後段製程的元件尺寸也持續加速縮小,進而實現更短的導線間距、更小的打線截面面積。現在大多數的重要局部互連導線(M1與M2)都能將導線間距縮短至40nm。而銅雙鑲嵌技術是長期被用來製造互連導線的製程。

雙鑲嵌製程首先將低介電(low-k)材料沉積於元件上。設計這些低介電薄膜的目的在於降低晶片的電容與延遲。接著,通孔(via)與通道(trench)成形。近期,所有的邏輯晶片製造大廠都宣布導入極紫外線(EUV)微影技術,為的就是在製造緊湊的導線間距時維持成本效益。晶片經過圖形化之後,會加上一層金屬阻障層來防止銅原子遷移至低介電材料。而後,將襯墊層(liner)與銅種子層(seed)塗佈於阻障層,再將晶片電鍍上銅,然後進行化學機械研磨(chemical mechanical polishing;CMP),完成雙鑲嵌製程模組。

佈線壅塞以及嚴重的電阻電容(RC)延遲已成為進一步微縮互連導線的重大瓶頸—後者源於產品的RC值增加,因而驅動後段製程推出新興材料與整合方案的需求。近來半導體業已將鈷(Co)視為局部互連導線的替代金屬材料,有些製造商則在中間層利用氣隙(airgap)來代替低介電材料。

中段製程:降低接觸電阻並提升連接性

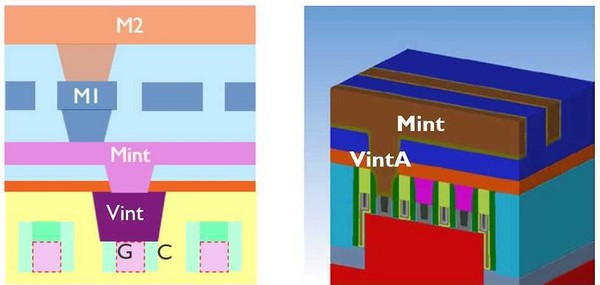

前段與後段製程的關聯就在於中段製程。過去長久以來,中段製程以單層接點佈局,但如今正在增加至數層,例如包含M0與M1之間的Mint金屬層,以及V0與V1之間的Vint通孔層。這些分層將電訊號自電晶體源極、汲極與閘極傳送至局部互連導線,也可以回傳。

| 圖三 : (左圖)中段製程中的晶片堆疊與(右圖)自對準閘極接點。 |

|

就電晶體來說,源極與汲極之間的接觸電阻漸漸變成晶片產業的一大考量。隨著電晶體微縮,製造接點的可用面積也隨之遞減。這也導致源極與汲極之間的接觸電阻急遽增加—該數值與接點面積成比例。這幾年,愛美科為了降低寄生電阻,持續研發源極與汲極之間的接點優化方案,主要是透過增加半導體的摻雜濃度,以及優化金屬(通常是過度金屬矽化物)與半導體之間的介面品質。

要進一步優化中段製程的連接性,結構性的微縮加速器也在推陳出新。自對準閘極接點就是一種,它能讓閘極接點直接置於有源元件上方,這能實現具備更高彈性的閘極連接,並降低整體接點面積。業界也已於目前的晶片設計中採用該技術來進一步提升可佈線性(routability)。

創新製程技術

前段製程:垂直堆疊的奈米片及其延伸版本叉型片

元件微縮推進至5nm以下的同時,FinFET估計也將失去發展動能。當閘極長度縮短,FinFET就不能提供通道足夠的靜電控制能力。除此之外,標準元件的軌道高度演變至5軌以下,因此需將晶片設計轉變至單鰭結構,因而無法提供充分的驅動電流,就算進一步增加鰭片高度也還是不夠。

這時,垂直堆疊的GAA奈米片就登場了。GAA奈米片可以視為是FinFET元件的自然演變。只要想像一下,將FinFET側置,再分成獨立的水平層片,這些層片形成通道。閘極被完全包圍並置於通道之間,如此就能實現相較於FinFET更佳的通道控制。同時將通道在3D空間中的截面分佈進一步優化,這也能盡量提升每個焊裝配置中的有效驅動。

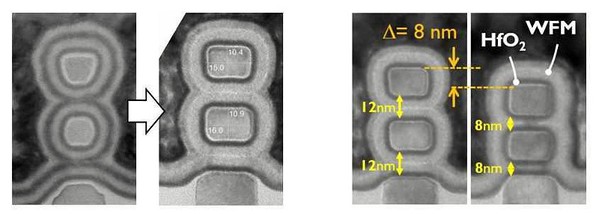

愛美科自2015年起便在研究這個架構,成果顯示製程中幾項最關鍵的步驟確實能因而實現優化。要製造垂直堆疊GAA奈米片電晶體,首先將磊晶沉積於多層矽(Si)或矽鍺(SiGe)上,接著製造淺溝槽隔離(shallow trench isolation)模組並進行填充。下一步就是把SiGe層挑出並移除,形成矽奈米片結構。在這些矽奈米片周邊與層片之間,則運用雙功函數替代金屬閘極(replacement metal gate;RMG)製程,製造出一組閘極堆疊。

除了優化製程,愛美科的研究團隊也持續開發將垂直奈米片間隔降至10nm以下的製程,如此一來,寄生電容就能大幅降低。目前有些晶片製造商也在準備朝向這些架構來生產他們的新一代晶片。

| 圖四 : 垂直堆疊GAA奈米片電晶體的優化:(左圖)奈米片的材形控制;(右圖)奈米片的垂直間隔調降。 |

|

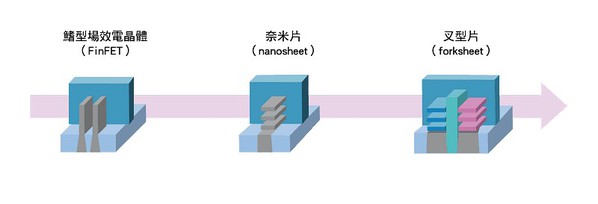

為了將奈米片元件微縮至2nm甚至是更先進的技術節點,愛美科最近提出了一個替代架構,叫做「叉型片」元件。在此架構下,奈米片由叉型的閘極控制,方法是在閘極圖形化前,於PMOS與NMOS之間導入介電牆。此介電牆會形成P型閘極通道與N型閘極通道間的物理性隔離,使得其N-P間距比FinFET或奈米片還要來得更加緊密。

經模擬後,愛美科預估這項奈米片設計能實現晶片微縮在尺寸與性能方面更優秀的表現(軌道高度可從5軌縮減至4.3軌),寄生電容也會更小。應用在SRAM的晶片設計上,預計元件尺寸也可能變小。

| 圖五 : 從FinFET到奈米片到叉型片的製程結構發展。 |

|

(本文由愛美科授權刊登;作者Zsolt Tokei1、Naoto Horiguchi2為愛美科1奈米互連導線研究計畫主持人、2邏輯CMOS微縮研究計畫主持人;編譯/吳雅婷)

**刊頭圖:(source:imec-int.com)