半導體異質整合是將不同製程的晶片整合,以提升系統性能和功能。

在異質整合系統中,訊號完整性和功率完整性是兩個重要的指標。

因此必須確保系統能夠穩定地傳輸訊號,和提供足夠的功率。

半導體異質整合技術現況

半導體的異質整合(Heterogeneous Integration)是指將不同製程、不同材料或不同功能的晶片整合在一起,以提升系統性能和功能。這種技術被視為延續摩爾定律的重要途徑,尤其在半導體製程技術逼近物理極限的情況下。目前,異質整合技術主要包括以下幾種形式:

●小晶片(Chiplet)技術:將多個具備不同功能的小晶片通過先進封裝技術整合於單一基板上。這種技術可以提高晶片製造的良率,降低設計複雜度和成本。

●系統級封裝(SiP):將數個不同製程的晶片透過異質整合技術連接,並整合於同一個封裝殼內。這種技術可以將邏輯晶片、記憶體、影像感測器等不同功能的晶片堆疊在一起。

●三維堆疊(3D Stacking):透過增加堆疊層數,在一個封裝結構中整合更多晶片,實現更高的元件密度。

異質整合技術在許多應用領域中發揮著關鍵作用,特別是在需要高性能和多功能整合的情況下。以下是一些最需要異質整合技術的應用領域:

AI和HPC

人工智慧(AI)和高效運算(HPC)應用需要大量的運算能力和高速數據傳輸。透過異質整合技術可以將不同功能的處理器、記憶體和加速器加以整合,提升系統的性能和效率。

5G通訊

5G技術需要高頻寬和低延遲的數據傳輸。異質整合技術可以將射頻(RF)元件、數據處理單元和天線整合,實現更高效的通訊系統。

物聯網(IoT)

物聯網設備需要低功耗和小型化設計。異質整合技術可以將感測器、處理器和無線通訊模組整合在一起,實現更小、更高效的物聯網設備。

消費電子產品

智能手機、平板電腦和可穿戴設備等消費電子產品需要高性能和多功能整合。異質整合技術可以將處理器、記憶體、影像感測器和顯示驅動器整合在一起,提升產品的性能和功能。

自動駕駛和車用電子

自動駕駛技術需要大量的感測器數據處理和即時決策。異質整合技術可以將雷達、光達(LiDAR)、攝像頭和處理器進行整合,提升自動駕駛系統的性能和可靠性。

| 圖一 : 西門子與聯電合作開發3D IC hybrid-bonding流程(source:西門子EDA) |

|

異質整合被視為延續摩爾定律的重要途徑,尤其在半導體製程技術逼近物理極限的情況下。

異質整合技術雖然帶來了許多創新和機遇,但也面臨一些挑戰。在成本控制方面,異質整合技術涉及多種不同的製程和材料,這使得成本控制變得複雜。特別是在使用先進封裝技術時,如何在保持高性能的同時降低成本是一大挑戰。

對於製程控制精準度,異質整合需要高度精準的製程控制,包括線寬控制和對位準確性。另外,異質整合技術通常會將多個晶片堆疊在一起,這會導致散熱問題。如何有效地管理和散熱,是確保系統穩定性和可靠性的關鍵。

在異質整合系統中,訊號完整性和功率完整性是兩個重要的指標。因此必須確保系統能夠穩定地傳輸訊號,和提供足夠的功率。另外,異質整合技術需要整個半導體供應鏈的協作,包括IC設計、晶圓製造、封裝和測試等環節。有效地協調和整合這些環節,才是實現異質整合的關鍵。

異質整合廠商技術發展

隨著5G、AI、HPC等應用的需求增加,異質整合技術成為半導體產業的重要發展方向。台積電(TSMC)在異質整合技術上投入大量資源,開發了整合型扇出(InFO)、晶圓級封裝(CoWoS)等技術,並應用於蘋果公司的A系列處理器。英特爾(Intel)也積極推動異質整合技術,開發了Foveros 3D封裝技術,並在其處理器產品中應用。三星(Samsung)也在異質整合技術上進行大量投資,開發了X-Cube 3D封裝技術,並應用於其高效能運算晶片。AMD則利用異質整合技術,將多個小晶片整合在一起,提升其處理器的性能和製造良率。

台積電

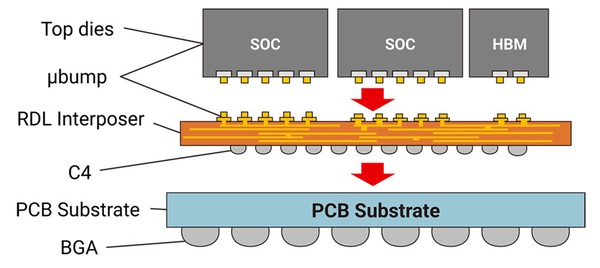

| 圖二 : 台積電的CoWoS封裝技術(source:TSMC) |

|

台積電在異質整合技術上的發展,特別是在整合型扇出(InFO)和晶圓級封裝(CoWoS)技術方面,已經成為半導體製造業中的領導者。這些技術的發展反映出TSMC在提升晶片效能、縮小封裝尺寸以及提高功耗效率方面的創新。

整合型扇出(InFO)技術是TSMC的一項創新封裝技術,目的在提高晶片的性能和功耗效率。InFO通過將晶片與扇出型封裝結合,實現了更高的I/O密度,並且可以更有效地散熱。這項技術的關鍵優勢在於其薄型化設計。InFO技術將晶片直接嵌入到扇出型封裝中,取消了傳統的基板(substrate),使得封裝更薄、更輕,適合於移動設備的應用。由於取消了基板,信號傳輸的延遲得以降低,進而提升了晶片的整體效能。特別是在高頻應用中,這一點顯得尤為重要。InFO技術也有助於降低封裝的電阻和電容,進而減少功耗,這對於現代電子設備的節能設計至關重要。目前TSMC的InFO技術已經成功應用於蘋果的A系列處理器。

晶圓級封裝(CoWoS)技術(Chip-on-Wafer-on-Substrate)則是另一項TSMC的重要異質整合技術。CoWoS將多個晶片(如處理器、記憶體、I/O晶片等)組裝在一個矽中介層上,並且封裝在一個基板上,來實現高度整合。CoWoS技術允許在一個封裝內整合高頻寬記憶體(HBM),這對於需要大量數據處理的應用(如AI、HPC等)非常有利。CoWoS技術也可支持不同製程的晶片,進行異質整合,可以在一個封裝內組合多種不同技術的晶片,實現不同功能的協同運作。而透過縮短晶片間的連接距離,CoWoS技術有效減少了信號傳輸的延遲和功耗,提升了系統的整體效能。

除了InFO和CoWoS,TSMC還在開發其他異質整合技術,如先進封裝技術SoIC(System on Integrated Chips)和Chiplet技術等。SoIC技術允許垂直堆疊晶片,進一步提高了封裝密度和效能,而Chiplet技術則透過模組化設計,實現了不同功能晶片的自由組合與配置。

英特爾

| 圖三 : 英特爾愛爾蘭新廠啟動Intel 4製程技術量產 |

|

異質整合技術涉及將不同製程、不同功能的晶片模組整合在一個封裝中,以提高系統性能和功能的整合度。隨著摩爾定律的放緩,單純依賴縮小晶片特徵尺寸的效益正在減少,因此,異質整合成為業界實現高效能和多功能整合的一個重要策略。

Foveros 3D封裝技術是英特爾開發的先進3D封裝技術,首次在2018年公布。這項技術是英特爾在異質整合領域的重大突破,允許不同製程技術的晶片垂直堆疊在一起。Foveros 3D封裝允許將不同功能的晶片(如運算模組、記憶體模組、I/O模組等)垂直堆疊在一起,這種3D整合方式大幅提升了系統的封裝密度。另一個特點是混合製程整合,Foveros能夠整合不同製程技術的晶片,這意味著可以將最先進的製程與成熟製程結合使用,實現成本效益和性能的平衡。例如,較先進的運算核心可以與較成熟的I/O模組結合使用。透過縮短晶片之間的連接距離,Foveros技術能夠減少功耗和信號傳輸延遲,進一步優化系統性能。

Foveros技術的首個商業化應用是在Intel Lakefield處理器中。這款處理器將多個運算核心、內存模組和I/O模組整合在一個小巧的封裝內,實現了高效能和低功耗的理想平衡,適合於超便攜設備和物聯網裝置。

除了Foveros,英特爾還開發了嵌入式多晶片互連橋接(EMIB)技術。這項技術是在基板上嵌入一個橋接器,實現不同晶片之間的高速互聯。與Foveros不同,EMIB是2.5D的異質整合技術。這兩項技術可以互補使用,以實現更加靈活和高效的晶片封裝解決方案。

三星

隨著半導體製程技術接近物理極限,傳統的製程縮小已經不足以繼續推動晶片性能的提升。因此,異質整合技術成為了包括三星在內的許多半導體公司重點投資的領域。三星積極開發包括2.5D和3D封裝技術在內的多種異質整合技術,三星的晶圓級封裝技術,如Fan-Out晶圓級封裝(FOWLP),能夠在封裝尺寸更小的情況下,實現更高的性能和I/O密度。三星也是HBM技術的領導者,這種技術通常與異質整合技術結合使用,以應對高性能運算和AI應用的需求。

X-Cube是三星推出的先進3D封裝技術,專門應對高效能運算和AI應用的需求。X-Cube技術的核心在於垂直堆疊多個晶片,實現高度整合和優化的封裝解決方案。X-Cube允許將邏輯晶片和SRAM記憶體晶片垂直堆疊,這樣可以顯著提高系統的帶寬,並且減少延遲和功耗。垂直堆疊的晶片透過矽穿孔(TSV)技術進行互連,這大大縮短了晶片間的信號傳輸距離,進一步提高了系統效能。X-Cube技術支持不同製程的晶片在同一封裝中進行整合,可以將最適合的製程技術應用於不同的功能模組,在效能、功耗和成本之間取得平衡。

AMD

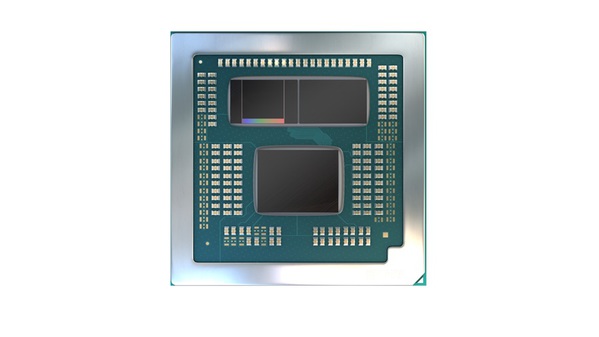

| 圖四 : 搭載AMD 3D V-Cache技術的行動處理器(source:AMD) |

|

AMD的異質整合技術主要展現在其Chiplet設計上。Chiplet是透過模組化的方法,將不同功能的晶片模組整合到一個單一的封裝中,而不是像傳統方法那樣將所有功能整合到一個大型的單晶片中。這種設計具有製程靈活性,Chiplet允許不同的Chiplet使用不同的製程技術。例如,運算模組可以使用最先進的製程技術(如7nm或5nm),而I/O模組則可以使用較成熟的技術(如14nm),這樣可以降低生產成本。Chiplet可以優化不同模組的性能和功耗,並透過高頻寬、低延遲的互連技術(如Infinity Fabric),實現不同Chiplet之間的高效通信。

AMD的Chiplet設計首次在其Ryzen和EPYC處理器中應用,這些處理器證明了這種設計的有效性,特別是在伺服器市場的EPYC處理器上。AMD還開發了3D V-Cache技術,這是一種將大量高速緩存(Cache)堆疊在處理器核心之上的3D封裝技術。這種技術可以顯著提高處理器的效能,特別是在需要大量數據存取的應用中,如遊戲和HPC。

AMD在2022年完成了對Xilinx的收購,這一收購使AMD在異質整合技術方面的能力得到了進一步增強。Xilinx是FPGA的領導業者,這使AMD能夠將FPGA與CPU和GPU進行異質整合,實現更靈活和高效的運算解決方案。

結語

異質整合技術為半導體產業提供了新的成長空間。透過將異質晶片模組在同一封裝內進行高效整合,能夠更好地應對市場對於高性能、低功耗和多功能整合的需求。隨著技術的不斷成熟和應用的擴展,異質整合技術將在未來的半導體市場中扮演越來越重要的角色,推動產業進一步向前發展。