圖像感測器可以說是在數位視訊或靜止相機中,視頻或靜止影像處理流水線的最重要部分。如果沒有感測器,就沒有圖像信號可進行處理。眾所周知感測器是非標準化的。在採用方案方面有以下的不同之處:

a. 轉換可見光或紅外光為電信號的方式。具體而言,在該信號離開這塊晶片之前,對這個信號採用編碼或壓縮的方式。

b. 對感測器內的寄存器進行程式設計,以調整增益、曝光時間、感測器的模式(如線性,HDR)技術,感測器圖像調整等。

c. 實現專門功能的方式,如高(或寬)動態範圍(HDR / WDR; 例如通過在同一封裝中的多個感測器,對於相同的圖像多次曝光等。

d. 這些感測器廠商安排了介面,使這些電子圖像信號離開這個感測器,並進入下游的處理邏輯。

圖像感測器技術

根據用於轉換可見光成電信號的基本技術,圖像感測器分為兩大類。它們是CCD(電荷耦合器件)感測器和CMOS(互補金屬氧化物半導體)感測器。到目前為止,用得最多的圖像感測器是CMOS感測器。本文只關注CMOS感測器介面。

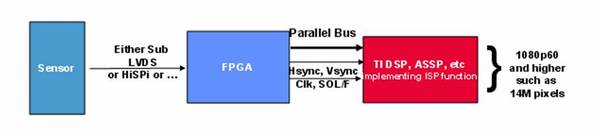

在視頻處理鏈中典型的圖像感測器的應用如圖1所示。

如今有幾個值得注意的圖像感測器製造商,分別是Aptina、OmniVision Technologies、索尼、三星、松下、東芝和Altasens。

如前所述,感測器製造商設計了一系列的介面來處理離開他們的晶片的圖像信號,用於下游邏輯來進行處理。根據需要從晶片中提取資料,相同感測器的製造商使用不同的介面,這是很普遍的。例如,具有百萬像素解析度的現代感測器需要在給定的週期時間傳出比僅具有VGA級解析度的感測器更多的資料。如高動態範圍(HDR)要求還增加了需要從每個圖像幀的圖像感測器讀取的資料量,為了支援平滑的,低延遲高品質的視頻,在給定的週期時間,需要從感測器晶片提取幀數,這也影響了感測器介面的選擇。

圖像感測器介面的演進

到目前為止,連接到並行LVCMOS介面的所有感測器,如圖2所示。感測器解析度和畫面播放速率已經提高到一個水準,以前主要的CMOS平行介面不再能夠處理所要求的頻寬。

由於百萬像素感測器的問世,對更高速度的需求激增,HDR和需要支援更高的畫面播放速率,新的、更高速感測器使用不同的介面,以克服並行LVCMOS的局限性。例如,索尼和松下使用並行的Sub-LVDS介面,OmniVision使用MIPI或串列LVDS。作為另一個例子,Aptina Imaging為了支持更高頻寬的需求,已經推出了稱為HiSPi(高速串列圖元介面)的高速序列介面。該HiSPi介面可以工作在1 - 4串列資料通道,再加上1個時鐘通道。每個信號是Sub-LVDS差分信號,以 0.9V的共模電壓為中心。每個通道可以運行高達700Mbps。

針對HiSPi需要至並行Senor介面橋接

眾多的感測器介面對標準化下游視頻處理邏輯的製造商提出了一個問題,因為難以用一個ASSP來支援許多不同的感測器介面。

大多數ISP(圖像信號處理)器件支援傳統的CMOS並行感測器介面,但通常缺乏對高速序列介面的支持。很多ISP平行介面的運行速度遠遠超過了感測器的平行介面。然而,由於感測器已移動到各種序列介面,這些ISP器件需要邏輯,以轉換到平行介面。因此FPGA的橋接器件需要轉換高速串列資料到並行格式。對於視訊訊號處理ASSP的製造商,它們擁有支援更快的並行CMOS感測器介面的現成產品,FPGA解決了介面至高速串列感測器的問題。 FPGA提供在高速感測器和傳統圖像信號處理ASSP之間的簡單,具有成本效益可程式設計橋接。這個概念如圖3所示。

| 《圖三 高速圖像感測器和ASSP之間的可程式設計橋接》 |

|

基於FPGA的串列Senor橋接參考設計的示例

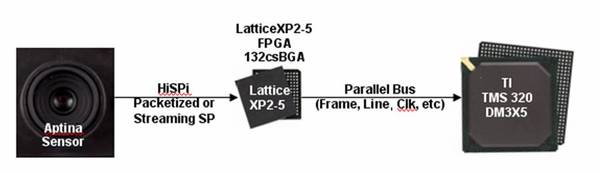

作為一個現實的例子,針對橋接Aptina圖像的HiSPi序列介面至TI DSP平行介面,LatticeXP2 - 5非易失性FPGA提供了有效的具有成本效益的解決方案,如圖4所示。

| 《圖四 Aptina HiSPi至TI DM3X5串列至平行介面橋》 |

|

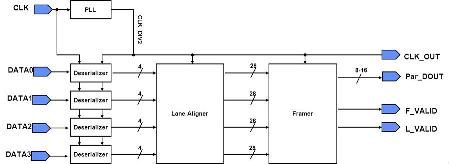

這個參考設計在FPGA輸入端用HiSPi序列介面,與Aptina感測器相接,而在輸出端與TI TMS320DM3X5相接。評估硬體已測試了Aptina的A -1000感測器MT9M034/MTM024和MT9J003該參考設計支持Packetized和Streaming SP HiSPi格式:1-4線運行速度高達每通道700Mbps。它還類比並行感測器輸出,輸出匯流排寬度為8、10、12、14或16位。平行介面可配置為1.8V,2.5V或3.3V LVCMOS的電平。參考設計的框圖如圖5所示。

| 《圖五 Aptina HiSPi至TI DM385介面橋接框圖》 |

|

FPGA在感測器介面橋接上的挑戰

可程式設計邏輯作為圖像感測器和ASSP之間橋接的挑戰有三個方面。首先,對於介面信號,FPGA必須提供電信號支援。第二,FPGA的I / O必須有足夠的匹配邏輯來支援快速串列感測器介面。第三,FPGA必須提供符合成本效益的非常小的體積,以適應對現代攝像機的緊湊的體積方面的要求。

有完備Sub-LVDS文檔支持的非易失LatticeXP2 FPGA解決了針對圖像感測器橋接的電氣需求。集成鎖相環、專用邊緣時鐘佈綫和I / O邏輯解決了高速串列感測器介面。最後,萊迪思的 XP2提供具有成本效益的8 ×8毫米面積。此外,由於其非易失性的性質,LatticeXP2系列器件無需外部PROM,在電路板上進一步節省了成本,對於感測器介面,他們成為有吸引力的可程式設計邏輯平臺。圖像信號處理(ISP)IP的實用性也使更大的LatticeXP2器件提供各種功能,如感測器資料線性化、感測器的寄存器程式設計、de-Bayering、有缺陷的圖元校正,伽瑪校正和簡單的HDR,每個色通道高達24位。

(本文由Lattice提供)