921地震,震出了台灣的悲情,也震出了前所未有的人民力量。921地震影響了台灣新竹科學園區廠房的生產,而使得DRAM價格大幅飆漲,此情形突顯了台灣半導體產業在世界上之影響力。在一般的文章中,比較常提到有關半導體IC製程,不外是設計尺寸大小(Design Rule),如0.25微米、0.20微米、0.18微米等以代表產品的競爭力,或是否先使用銅製程以代表產品速度的品質。就DRAM製程技術而言,所採用的電容技術發展策略亦有極大的影響。以台灣目前主要的DRAM製造廠來分析,大致可將之歸類為兩大技術群:以IBM/Siemens/Toshiba為技術源的立體溝槽式DRAM技術,及Mitsubish等的立體堆積式DRAM技術兩大類。

廠商的立體堆積式DRAM

(表一)提供了國內各主要DRAM廠的電容製程技術及相關推測,或許與實際上有些許差距,僅供諸位讀者參考。由表一略可看出,國內在DRAM技術上的自主性仍偏低,且集中在0.25~0.20微米的設計尺寸階段,近期華邦所推出的0.175微米256M DRAM算是較有突出表現的。同樣是以溝槽式電容製程的茂德及南亞科技,亦應有極大的潛力,於近期內推出0.18或0.175微米的128M或256M DRAM產品。

相同地,以立體堆積方式電容製程的力晶、世界先進則是亦步亦趨,力晶更是率先開出0.18微米的128M DRAM的製程。結合力晶、世界先進、三菱及台積電的策略合作,以此立體堆積式電容製程的DRAM應用,可預期將會有一番不錯的成果。

而廿一世紀的DRAM競爭,在0.18微米64M~128M DRAM的產能上,台灣幾乎可佔全世界20%的產能,面臨可能景氣強力復甦的2000年下半年及2002年間的強力需求,對於台灣半導廠來說將可展現超強的競爭力。而韓、美、日的DRAM大廠,在1999年間除少數如三星、現代、美光外,幾無太多的投資,而面臨競爭力日益衰退的現象。

如何藉此一波段的強勁復甦力及0.18微米的生產能力,以更進一步建立起更為踏實的技術研發及產品開發能力,如0.13微米、0.13微米以下的Lithography技術及元件、銅導線製程及銅包裝(Cu Interconnect and Cu Package)、DRAM電容技術等,應是目前台灣DRAM廠商必須特別留意之處。

台灣茂矽秉於過去在DRAM領域上的專著及經營的靈活性,除了6吋廠在95~97年代以獨創的堆疊式DRAM技術贏得2M DRAM及4M DRAM世界第一的美譽,更採取策略合作方式,跳躍式地由6吋8M DRAM直接進入8吋64M DRAM的領域,並成功地創造了茂德科技全新領域。對於未來DRAM技術的展望,茂矽除了積極將6吋FAB轉型外,對於DRAM技術上的發展,仍不得不面臨與其他多數DRAM廠遇有相同的問題。

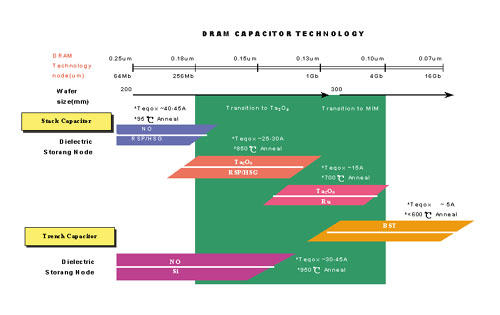

0.13微米的1Gb DRAM之Capacitor技術選墿,與Ferro Electric、Magnetic等新材料/技術可能帶來的衝擊,就如同世界最大半導體設備廠─美商應用材料(Applied Materials)所揭露的DRAM Capacitor技術發展行程如(圖一)(參考Semiconductor International Nov.99 〈page79~82〉),力晶、世界先進等堆疊式DRAM廠,到0.15微米的DRAM產品就非得採行如HSG(半球狀成長晶體;Hemi-Sperical Grain growth)及Ta2O5等技術,以提高產品的良率。而茂德、華邦、南亞等溝槽式DRAM廠,亦將面臨溝槽蝕刻及介電層極限的問題。

| 《圖一 DRAM Capacitor技術發展行程》 |

|

另外,IBM雖已宣稱所謂瓶狀(Bottle Shape)溝槽可因應到0.13微米以下的能力,此一技術使IBM退出DRAM自我生產的陰影下,東芝轉進採用堆疊式DRAM行列,以Semens(Infineon)的一已之力,能否順利解決0.15微米以下溝槽式DRAM的生產問題,應是值得觀察。

0.15微米以上DRAM的技術發展

當現代、三星、美光及Hitach-NEC四強逐形成,Intel捨棄Direct Rambus DRAM而與四強共同訂定新DRAM標準之時,新的DRAM局勢已漸漸成形。顯然地,台灣在2000年至2002年的波峰中,0.18微米到0.20微米應是處於贏多輸少的局面,不論是溝槽式或堆疊式的64M或128M DRAM,在這一波中扮演成功的二線DRAM角色,應能讓台灣各DRAM廠有極佳之營利。但要如何因應四大DRAM廠可能新訂的DDR2新規,且能繼續生存,著實是台灣各DRAM廠的一大隱憂。

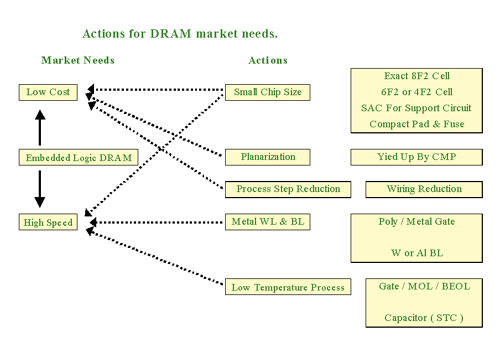

就DRAM設計而言,一個電晶體(Transistor)+一個電容(Capacitor)+導線(Interconnect)即可構成基楚的DRAM結構,如(圖二)所示。而隨著製程技術的演進及DRAM高容量、高速度的市場需求,除了電晶體(Transistor)的不斷縮小(如0.35um→0.25um→0.20um→0.18um→0.15um→0.13um,往往配合所謂的Design Rule演進)、導線的材料變更(如Al→Cu,以提高元件信號傳輸速度);另一項極重要的是電容技術亦隨之改變,以提高單位面積的電容量。

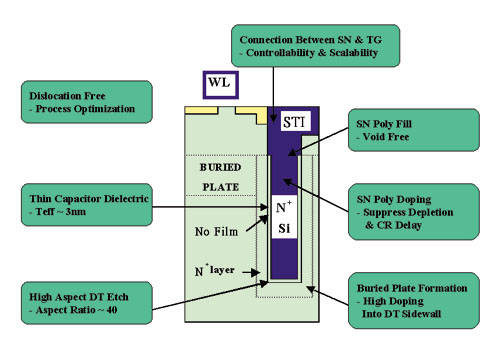

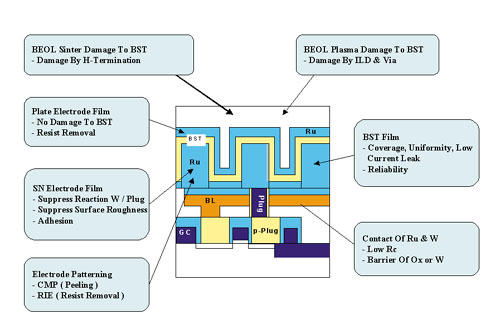

(圖三)顯示,隨著DRAM的演進,在電容技術也跟隨著變化。此變化不外是朝立體方式以增加表面積(圖四)或是提高電容的介電值(圖五),以維持一定的電容量。另一方面,從基楚技術角度,圖一中的設備廠商所提供的設備能力極限,在0.15微米世代不論是溝槽式的BEST(Subtract Plate+Buried Strap)結構,或是Crown,HSG結構應仍可提供足夠的電容,使用於64M DRAM亦或是128M DRAM上。

| 《圖三 Actions for DRAM Market Needs》 |

|

| 《圖四 Concerns of BST cell for giga bit ear--A》 |

|

| 《圖五 Concerns of BST cell for giga bit era--B》 |

|

茂矽電子為求在DRAM技術上的競爭能力,除與西門子(Infenion)策略合作成立茂德8吋廠,從事溝槽式DRAM的製造,更著眼於溝槽式DRAM技術,在0.20微米至0.15微米間配合,即所謂Embedded DRAM的設計與製造,以創造出有別於純DRAM的事業領域。同時,茂矽亦在國科會的經費補助之下於6吋廠完成以HSG之堆疊式64M DRAM的設計與試製。此一技術雖不具經濟生產價值卻也為茂矽墊定往後0.15微米DRAM Capacitor的技術基楚。

後0.15微米之DRAM技術

0.15微米的DRAM技術,將取決於:(1)0.13微米,深達5微米的溝槽蝕刻力;(2)完整的NO介電層能順利推向30A的極限;或是(3)BST等高介電值材料的技術開發。IBM與西門子是目前世界上仍著重於0.13微米溝槽的DARM技術開發公司,雖其發表的瓶狀溝槽結構可解決0.13微米技術的瓶頸,但IBM在適時退出DRAM生產行列,僅保留技術研發部份,而且應用材料對此一溝槽式DRAM技術抱持觀望態度的情形下,似乎不具樂觀。

相較之下,以堆疊式DRAM為主軸的三星、現代、三菱、Hitach-NEC,卻採取了0.5微米至0.25微米FeRAM與0.15微米1GDRAM同步發展的技術開發策略。其主要原因是,FeRAM具非揮發性的特色及其所需的新材料(PZT、SBT)、製程與1GDRAM的BST製程有相當程度的相似。經由1M FeRAM以下Smart Card的應用開發經驗,可符合2000年後Smart Card大量的需要,又可建立DRAM所需的相關材料製程開發,或甚至與MRAM爭奪取代DRAM的機會。

另外,以BST(Ba、Sr)TiO3堆疊式Capacitor的技術,其延伸性可從0.18微米到0.1微米,如能從材料的形成、蝕刻及製程整合的問題逐一解決,則如(表二)的技術推展,將可在世界的DRAM市場上佔有一席之地。