对千兆(Gigabit)SerDes的信道进行布线後验证,是一项具有挑战性但也是必要的任务,因为即使是最详细的预先布局模拟研究和布线指南也不能预测一切。满足详细布线要求的设计,仍然可能会由於不连续和不可预期的谐振而导致失败。

|

| 仿真项目的周期比以前来得更短,迫使仿真工具朝向整合化与自动化的趋势发展。 |

在现代设计中,大量的信道使得布线後验证变得更困难,每个信道都必须单独建模和分析,这需要一个自动化、高效率的过程才能成功。一旦建模,就必须以相同的自动化方式分析每个通道是否符合协议要求。

Mentor PCB系统部门应用工程师闵潇文指出,千兆位元的创新链路呈现了当今设计者面临的最严格信号完整性挑战,现今的系统中,通常都会有大量的SerDes通道,每条通道都必须单独建模与分析,如何进行快速的仿真与分析,这就需要一个自动化、高效率的过程才能成功。

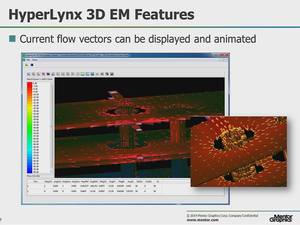

在复杂系统中常见的通道建模问题,包括了庞大的系统中可能会有数百条串行通道需要後仿真验证。另外3D的EM模型需求也持续增加,这是由於速度的上升使得更小的结构需要3D EM,且同时需要简化3D EM建模的难度。而整个建模也需要自动化流程,否则在原理图介面连结各个模型非常容易导致错误的发生。

闵潇文说,虽然虚拟的合规测试不是新鲜概念,但是执行合规仿真需要设计人员对於协议有比较深入的理解,因此合规仿真检查并没有广泛的被硬体设计师采用。而市场也一直都在寻找更加简单高效的方法来进行这方面的仿真,事实上,今日的仿真工作量正在持续增加,但在此同时,仿真项目的周期比以前还来得更短,因此这迫使仿真工具朝向整合化与自动化的趋势来发展。

对工程师而言,企业会要求电路板的设计者可以验证大部分的常见设计问题,并将更好的初始设计传递给SI专家,而SI与PI等专家可以专注在更困难的问题上,并进一步优化系统的整体性能,以把握性能与成本之间的平衡。

为了实现自动化的目标,从根本上来探讨

闵潇文认为,SerDES通道包含三项主要任务,分别是构建建议通道的准确模型、创建通道模型後对其进行验证,以及使用该信息评估权衡并做出设计决策。而实现自动化仿真的关键问题,在於Layout导向的大量仿真、快速创建3D区域、基於协议的自动合规分析,以及通道的叁数化等作业。

一般来说,速度与精度之间的权衡,需要考量整合的2D、2.5D、3D电磁解析器,而仿真通吐量将随着精度的提高而降低,若随着设计的进展来提高精度,将可缩短总体设计的周期。

合规分析的优势,包含了特定标准中定义的所有约束、易於使用与降低仿真门槛、协议与接囗允许的最坏情况下随机抖动,这比起IBIS-AMI模型运行快得多,EDA工具很快就能找到最隹均衡设置,并在Tx/Rx的两端协同优化。但其劣势则在於与IBIS-AMI模型相比,行为模型对实际设备的描述将不够准确。因此,较适用於预先布局分析的通道优化和布线後的错误筛选验证。

在HyperLynx中的SerDES Wizard,可针对通道协议合规性来做出设计决策,不需要发射器与接收器模型,且速度快,可在几秒钟内完成运行,并进行最隹元件的均衡设置。

闵潇文说,高速通道仿真正迈向自动化的趋势发展,增加效率的关键问题包括实现Layout导向的设计验证、快速3D EM自动建模、基於协议的合规分析,以及实现通道模型的叁数化等重点。如此将可缩短仿真时间、提高验证覆盖度,而专家工程师也更能将时间专注於设计上的优化工程。