對千兆(Gigabit)SerDes的信道進行佈線後驗證,是一項具有挑戰性但也是必要的任務,因為即使是最詳細的預先佈局模擬研究和佈線指南也不能預測一切。滿足詳細佈線要求的設計,仍然可能會由於不連續和不可預期的諧振而導致失敗。

|

| 仿真項目的週期比以前來得更短,迫使仿真工具朝向整合化與自動化的趨勢發展。 |

在現代設計中,大量的信道使得佈線後驗證變得更困難,每個信道都必須單獨建模和分析,這需要一個自動化、高效率的過程才能成功。一旦建模,就必須以相同的自動化方式分析每個通道是否符合協議要求。

Mentor PCB系統部門應用工程師閔瀟文指出,千兆位元的創新鏈路呈現了當今設計者面臨的最嚴格信號完整性挑戰,現今的系統中,通常都會有大量的SerDes通道,每條通道都必須單獨建模與分析,如何進行快速的仿真與分析,這就需要一個自動化、高效率的過程才能成功。

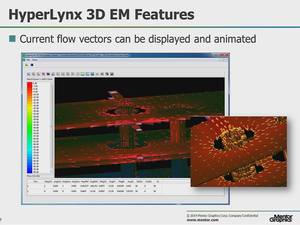

在複雜系統中常見的通道建模問題,包括了龐大的系統中可能會有數百條串行通道需要後仿真驗證。另外3D的EM模型需求也持續增加,這是由於速度的上升使得更小的結構需要3D EM,且同時需要簡化3D EM建模的難度。而整個建模也需要自動化流程,否則在原理圖介面連結各個模型非常容易導致錯誤的發生。

閔瀟文說,雖然虛擬的合規測試不是新鮮概念,但是執行合規仿真需要設計人員對於協議有比較深入的理解,因此合規仿真檢查並沒有廣泛的被硬體設計師採用。而市場也一直都在尋找更加簡單高效的方法來進行這方面的仿真,事實上,今日的仿真工作量正在持續增加,但在此同時,仿真項目的週期比以前還來得更短,因此這迫使仿真工具朝向整合化與自動化的趨勢來發展。

對工程師而言,企業會要求電路板的設計者可以驗證大部分的常見設計問題,並將更好的初始設計傳遞給SI專家,而SI與PI等專家可以專注在更困難的問題上,並進一步優化系統的整體性能,以把握性能與成本之間的平衡。

為了實現自動化的目標,從根本上來探討

閔瀟文認為,SerDES通道包含三項主要任務,分別是構建建議通道的準確模型、創建通道模型後對其進行驗證,以及使用該信息評估權衡並做出設計決策。而實現自動化仿真的關鍵問題,在於Layout導向的大量仿真、快速創建3D區域、基於協議的自動合規分析,以及通道的參數化等作業。

一般來說,速度與精度之間的權衡,需要考量整合的2D、2.5D、3D電磁解析器,而仿真通吐量將隨著精度的提高而降低,若隨著設計的進展來提高精度,將可縮短總體設計的週期。

合規分析的優勢,包含了特定標準中定義的所有約束、易於使用與降低仿真門檻、協議與接口允許的最壞情況下隨機抖動,這比起IBIS-AMI模型運行快得多,EDA工具很快就能找到最佳均衡設置,並在Tx/Rx的兩端協同優化。但其劣勢則在於與IBIS-AMI模型相比,行為模型對實際設備的描述將不夠準確。因此,較適用於預先佈局分析的通道優化和佈線後的錯誤篩選驗證。

在HyperLynx中的SerDES Wizard,可針對通道協議合規性來做出設計決策,不需要發射器與接收器模型,且速度快,可在幾秒鐘內完成運行,並進行最佳元件的均衡設置。

閔瀟文說,高速通道仿真正邁向自動化的趨勢發展,增加效率的關鍵問題包括實現Layout導向的設計驗證、快速3D EM自動建模、基於協議的合規分析,以及實現通道模型的參數化等重點。如此將可縮短仿真時間、提高驗證覆蓋度,而專家工程師也更能將時間專注於設計上的優化工程。