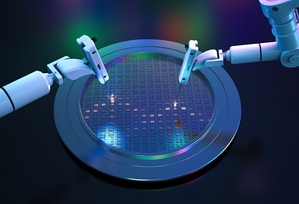

西门子数位化工业软体近日与联华电子(UMC)合作,为联华电子的晶圆对晶圆堆叠(wafer-on-wafer)及晶片对晶圆堆叠(chip-on-wafer)技术提供新的多晶片 3D IC 规划、组装验证,以及寄生叁数萃取(PEX)工作流程。联电并将向全球客户提供此项新流程。藉由在单一封装元件中提供晶片或小晶片(chiplet)彼此堆叠的技术,企业可以在相同或更小的晶片面积上实现多个元件的功能。与在 PCB 板上摆置多个晶片的传统系统配置相比,这种方法不仅更加节省空间,而且能够提供更出色的系统效能及功能以及更低的功耗。

|

| 西门子与联华电子合作开发 3D IC hybrid-bonding 流程 |

联华电子元件技术开发及设计支援??总经理郑子铭表示:「我们的客户现在可以使用强大且经过验证的晶圆制造设计套件与流程,来验证他们的晶片堆叠设计,同时校正晶片对位及连接,并获取寄生叁数,以便在讯号完整性的模拟中使用。联电与西门子 EDA 的共同客户对於高性能运算、射频和 AIoT 等应用的需求正日益提升,随之而来的 3D IC 解决方案需求也相应增长,联电此次与西门子的合作能够协助客户加快整合产品设计的上市时间。」

联电开发出其全新混合键合(hybrid-bonding)3D 电路布局验证(LVS)和寄生叁数获取工作流程,使用西门子 XPEDITION Substrate Integrator 软体进行设计规划与组装,西门子 Calibre 3DSTACK 软体进行晶片间的连接检查,同时还使用 Calibre nmDRC 软体、Calibre nmLVS 软体及 Calibre xACT 软体进行 IC 及晶片间延展实体及电路验证任务。

西门子数位化工业软体电路板系统高级??总裁 AJ Incorvaia 表示:「西门子很高兴能够与联电继续合作,为双方共同客户提供显着的优势。随着客户开发复杂性更高的设计需求,联电与西门子也准备好提供所需的先进设计流程,让客户能将这些复杂设计付诸实现。」