為因應更趨複雜的晶片設計與先進製程需求,電子設計自動化(EDA)方案供應商益華電腦(Cadence Design Systems)宣布,推出全新的數位全流程,結合新推出的iSpatial技術與機器學習(ML)功能,能大幅縮短整體晶片開發的時間,同時更進一步提升晶片本身的PPA(效能、電耗、面積)結果。

|

| 此次發表的新數位流程方案中,iSpatial技術是關鍵的一項技術。 |

Cadence研發副總裁羅宇鋒在今日的媒體線上聯訪中表示,Cadence長期致力於IC設計數位流程的創新與研發,能為晶片開發者帶來產業最佳的PPA成果。透過整合與平行處理多項流程,已為產業界帶來了多項革新的產品。

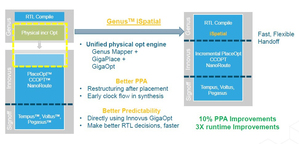

此次發表的新數位流程方案中,iSpatial技術是關鍵的一項技術。羅宇鋒指出,iSpatial技術將Innovus設計實現系統工具的GigaPlace佈局引擎,以及GigaOpt Optimizer整合到Genus合成(Synthesis)解決方案中,提供如繞線層分配、時脈偏移調教、通孔等技術,讓原本分開的兩項流程可以有更多的協同作業,其好處就是讓整個設計流程更加順暢且快速。

此外,藉由通用的使用者介面及資料庫,iSpatial技術也實現了Genus物理合成,到Innovus設計實現的無縫接軌,提供兩端的彼此切換(Handoff)的功能,帶來了更快速的IC開發速度,同時也有更多的設計彈性,以因應目前的晶片設計需求。

羅宇鋒也強調,Cadence的iSpatial技術的優勢,主要就是在執行期間(Runtime)與漸進式佈局(Incremental)的提升。所呈現的結果就是讓執行效能提升了三倍,同時也改善了設計的PPA,並且讓晶片設計的可預測性(Predictability)大幅提升。

Cadence的數位流程方案中的另一個亮點,則是機器學習(ML)技術的採用,它透過對晶片設計模型的訓練與分析,能夠助開發者提升晶片的PPA與可預測性。

羅宇鋒表示,晶片設計的ML應用可分為外部與內部,而此次的方案主要是針對內部的流程,也就是優化晶片設計的成果。客戶能運用此技術優化晶片起始的設計,進一步改良晶片的PPA成果,同時也讓晶片的製造有更高的可預測性。他也強調,採用該ML技術並不需要太多的模型資料量,能夠很快的就取得成果。

而在最後的晶片簽核(signoff)方面,新的數位全流程也整合了設計實現、時序及IR簽核引擎(涵蓋了Tempus時序簽核解決方案、Voltus IC電源完整性解決方案),藉由同步簽核物理、時序及可靠性的設計,強化簽核收斂,降低設計餘量及迭代次數。

羅宇鋒特別指出,電壓衰退(IR drop)的問題,在7奈米以下的設計漸趨嚴重,因此必須要有新的簽核方法。而唯有透過同步簽核的方式,才能夠實現最佳的晶片設計,同時讓設計所需的時間與成本降到最低。

而此新的iSpatial技術與新數位流程,目前已獲得聯發科與三星電子採用,用以開發旗下最先進製程的晶片。