為了協助客戶做好專利迴避、完整提出該層電路圖找異常點(Defect),宜特推出獨家晶片去層技術,將樣品如魔術般放大,直接在晶片封裝(Package)還存在的情況下進行去層工程,不僅可以大幅提升工程上的良率,完整提出電路圖,還可衍生應用在合金PAD、精密IC及其他無法取Die卻需要去層的晶片樣品上。

|

| /news/2020/03/29/0906268410S.jpg |

宜特觀察發現,隨著摩爾定律,製程演進至7奈米、5奈米甚至達3奈米,晶片裏頭的die,幾乎是接近螞蟻眼睛大小,一般人眼無法辨識。因此,希望藉由一般的晶片層次去除(delayer)來完整提取die裏頭每一層的電路,難度是非常高,硬是下去進行一般層次去除(delayer)技術的後果,不只是良率偏低,更可能發生連die都去除到不見遺失的窘境。

宜特說明,以往一般的取die後去層(Delayer)的技術,會因為樣品過小等因素,導致die不見或crack而無法進行製程分析;當無法去層(Delayer)到金屬層(Metal) M1時,記憶體(memory block)僅能以推測得知,電路模組分析圖亦無法完整繪製。

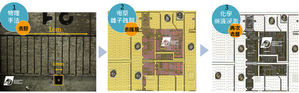

宜特的獨家去層技術,共分為三步驟,第一步驟,利用物理手法去除膠體,首先,在晶片封裝(Package)還存在的情況下,以物理方式去除晶片die正面多餘的膠體。相較以往須先去除package僅在裸die上去層,此法可在較大的面積/體積上施作,可大幅減少後續去層時die遺失的機率,並保持die面的平整度。

第二步驟則是機台去層,藉由離子蝕刻機,將IC護層(Passivation)與隔絕層(Oxide),用適當參數以離子蝕刻方式,將不需要的部份移除,藉由宜特獨家的控制參數方式,使得下層金屬層(Metal)不受傷。

第三步驟,藥液去層,IC護層(Passivation)被去除後,宜特再以藥水蝕刻,蝕刻該層需去除的金屬層(Metal),即可完整提出電路圖。