为因应更趋复杂的晶片设计与先进制程需求,电子设计自动化(EDA)方案供应商益华电脑(Cadence Design Systems)宣布,推出全新的数位全流程,结合新推出的iSpatial技术与机器学习(ML)功能,能大幅缩短整体晶片开发的时间,同时更进一步提升晶片本身的PPA(效能、电耗、面积)结果。

|

| /news/2020/04/23/1703482630S.jpg |

Cadence研发??总裁罗宇锋在今日的媒体线上联访中表示,Cadence长期致力於IC设计数位流程的创新与研发,能为晶片开发者带来产业最隹的PPA成果。透过整合与平行处理多项流程,已为产业界带来了多项革新的产品。

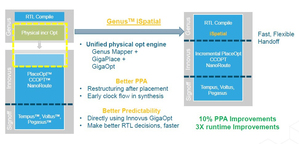

此次发表的新数位流程方案中,iSpatial技术是关键的一项技术。罗宇锋指出,iSpatial技术将Innovus设计实现系统工具的GigaPlace布局引擎,以及GigaOpt Optimizer整合到Genus合成(Synthesis)解决方案中,提供如绕线层分配、时脉偏移调教、通孔等技术,让原本分开的两项流程可以有更多的协同作业,其好处就是让整个设计流程更加顺畅且快速。

此外,藉由通用的使用者介面及资料库,iSpatial技术也实现了Genus物理合成,到Innovus设计实现的无缝接轨,提供两端的彼此切换(Handoff)的功能,带来了更快速的IC开发速度,同时也有更多的设计弹性,以因应目前的晶片设计需求。

罗宇锋也强调,Cadence的iSpatial技术的优势,主要就是在执行期间(Runtime)与渐进式布局(Incremental)的提升。所呈现的结果就是让执行效能提升了三倍,同时也改善了设计的PPA,并且让晶片设计的可预测性(Predictability)大幅提升。

Cadence的数位流程方案中的另一个亮点,则是机器学习(ML)技术的采用,它透过对晶片设计模型的训练与分析,能够助开发者提升晶片的PPA与可预测性。

罗宇锋表示,晶片设计的ML应用可分为外部与内部,而此次的方案主要是针对内部的流程,也就是优化晶片设计的成果。客户能运用此技术优化晶片起始的设计,进一步改良晶片的PPA成果,同时也让晶片的制造有更高的可预测性。他也强调,采用该ML技术并不需要太多的模型资料量,能够很快的就取得成果。

而在最後的晶片签核(signoff)方面,新的数位全流程也整合了设计实现、时序及IR签核引擎(涵盖了Tempus时序签核解决方案、Voltus IC电源完整性解决方案),藉由同步签核物理、时序及可靠性的设计,强化签核收敛,降低设计馀量及迭代次数。

罗宇锋特别指出,电压衰退(IR drop)的问题,在7奈米以下的设计渐趋严重,因此必须要有新的签核方法。而唯有透过同步签核的方式,才能够实现最隹的晶片设计,同时让设计所需的时间与成本降到最低。

而此新的iSpatial技术与新数位流程,目前已获得联发科与三星电子采用,用以开发旗下最先进制程的晶片。