大人物(大數據、人工智慧、物聯網)時代來臨,高效能、低功耗、多功能高階製程晶片扮演重要角色,隨著功能增加,晶片面積也越來越大,想降低晶片成本,先進封裝技術不可或缺。棘手的是,先進封裝技術導入過程中,很可能因為良率不穩定導致成本墊高。另一方面,新功能晶片模組在面積變大之餘也要克服摩爾定律(Moore’s Law)物理極限,在電晶體密度與效能間找到新的平衡。前述兩個問題,小晶片(Chiplet)有解!

| 圖一 : 國研院半導體中心副主任謝嘉民。(攝影:季平) |

|

國家實驗研究院台灣半導體研究中心(簡稱國研院半導體中心)副主任謝嘉民指出,過去的晶片效能提升多仰賴半導體製程改進,隨著元件尺寸越接近摩爾定律物理極限,晶片微縮的難度就越高,要讓晶片設計保持小體積、高效能,除了持續發展先進製程,也要著手改進晶片架構(封裝),讓晶片堆疊從單層轉向多層,小晶片如樂高積木「疊疊樂」的特性吸引各方關愛的眼神。

| 圖二 : 工研院資通所組長許鈞瓏。(Source:工研院) |

|

工研院資訊與通訊研究所(簡稱資通所)組長許鈞瓏進一步指出,傳統系統單晶片是將每一元件放在單一裸晶(IP)上,功能越多,矽晶片尺寸就越大,小晶片的做法則是將大尺寸多核心設計分散成不同的微小裸晶片,如處理器、類比元件、儲存器等,再用樂高積木的概念堆疊,以封裝技術做成一顆晶片。

由於晶片數目不可能一直成長,小晶片將SoC切割成多塊小晶片的概念可以把共通功能裸晶做在一起,比方基礎晶片用低階製程做,上面疊高階製程小晶片,也就是異質整合,如此,廠商可以靈活運用,生產良率得以提升,更可以降低晶片成本。

小晶片的價值:突破摩爾定律+降低成本

「小晶片」並非新概念,而是半導體先進封裝技術之一,最早喊出Chiplet(小晶片)名詞的是Intel和AMD,AMD Ryzen時代使用的Infinity Fabric技術堪稱小晶片濫觴。

小晶片設計源於1970年代誕生的多晶片模組封裝方式,當摩爾定律趨向3奈米、1奈米物理極限,小晶片技術可能為上游IC設計、EDA Tools、製造、先進封測等產業鏈帶來顛覆性的改變。有別於原來設計在同一個SoC中的晶片,小晶片把儲存、計算和訊號處理等功能模塊化成裸晶片(Die),分拆成許多不同的小晶片再加以封裝,達到整合效果。

傳統晶片製造方法是在同一塊wafer上用同一種製程打造一塊晶片,為整合新功能晶片模組(SoC)而增大晶片面積,勢必提高成本、降低良率,「過去封裝能力不好,要把元件做小才能在每單位塞進更多晶片,想要提升每單位計算能力,封裝是必要手段,小晶片封裝3D立體化技術可以往上疊很多層。」謝嘉民說。

| 圖三 : 國研院半導體中心副主任莊英宗。(攝影:季平) |

|

國研院半導體中心副主任莊英宗則指出,為降低功耗、提升速度、增加集成密度,半導體元件持續微縮,但微縮成本太高,也無法解決所有問題,解套方法就是讓高效能晶片使用最先進製程製造,其它則使用符合經濟效益的非最先進製程製造,如I/O晶片、記憶體晶片等,「Chiplet將電路分割成獨立小晶片,各自強化功能、製程技術及尺寸,最後整合在一起,除了克服微縮挑戰,還有助降低成熟晶片開發和驗證成本。」這個技術趨勢也會讓原本使用不同工具鏈與設備的前後段半導體製程變得越來越相似。

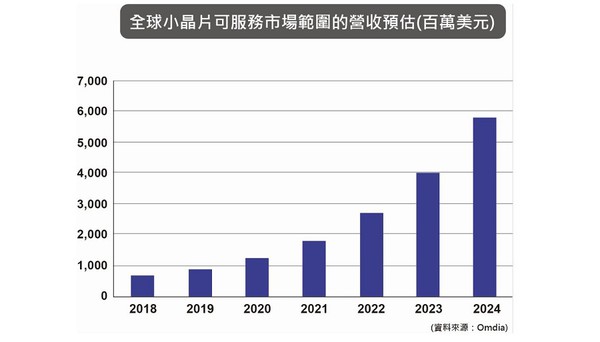

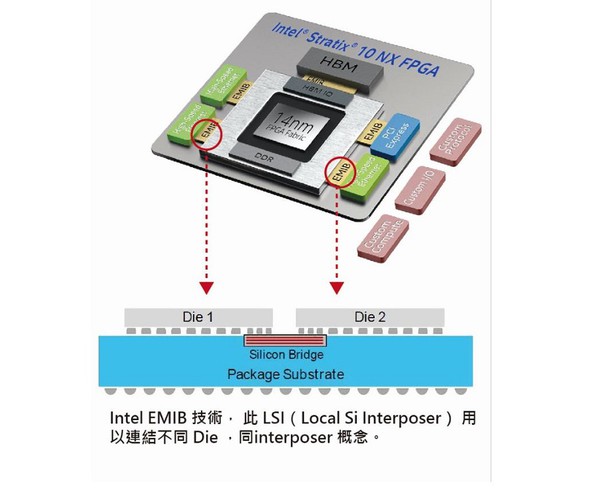

市場研究公司Omdia指出,小晶片在2024年全球市場規模將達58億美元,與2018年的6.45億美元相較,成長約九倍之多,預估2035年市場規模將達570億美元,特別是圖形、AI、低功耗物聯網(IoT)、安全引擎領域扮演重要角色。目前主要運用小晶片整合封裝技術的大廠包含台積電的CoWoS/SoIC(System-on-Integrated-Chips)、Intel的2D封裝技術EMIB(Embedded Multi-die Interconnected Bridge)及Fovores 3D封裝技術、AMD的MCM(Multi-Chip-Module)晶片整合封裝技術等。

| 圖四 : 市場研究公司Omdia指出,小晶片(Chiplet)在2024年全球市場規模將達58億美元。(source:Omdia) |

|

小晶片的應用與發展

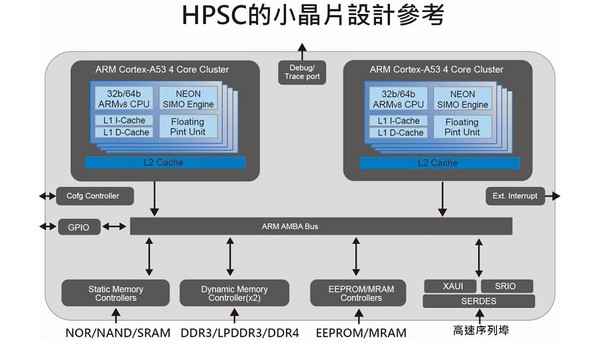

小晶片適合運用在AI雲端、邊緣運算、軍事和航空等「高階少量」領域。航空運用方面,美國太空總署(NASA)與波音公司共同開發特殊規格太空用高效能處理器(High Performance Spaceflight Computing Processor (HPSC Chiplet)即為一例;軍事運用方面,美國DARPA(國防高級研究計劃局)電子復興計劃(ERI)中的CHIPS項目已於2017年8月啟動,目標即為創造使用 Chiplets設計系統的晶片,未來可運用於戰機、導彈的高效能運算。

已有許多半導體業者推出小晶片高效能產品,創造更高的元件密度和容量,比方Intel Stratix 10 GX 10M FPGA採用小晶片設計,以Intel Stratix 10 FPGA 架構及嵌入式多晶片互連橋接(EMIB)技術為基礎,透過EMIB融合高密度Intel Stratix 10 GX FPGA 核心邏輯晶片及I/O單元。

台積電與Arm在2019年共同發表支援高效能運算應用的7奈米小晶片系統就是採用台積電2.5D/3D IC一條龍製程CoWoS封裝解決方案。同樣看好小晶片系統級封裝及異質整合能力,AMD 2019年也與台積電合作7奈米先進製程量產EPYC伺服器處理器,以7奈米FinFET製程及4GHz Arm核心支援打造高效能運算系統單晶片(System-on-Chip, SoC)。

AMD第二代EPYC系列處理器有別於第一代Chiplet方式,將Memory與I/O結合成14奈米CPU,第二代將Memory與I/O獨立成一個晶片,同時將7奈米 CPU切成8個Chiplets加以組合。

台積電在運算應用方面的發展較以往數十年更多元化,包含雲端運算、大數據分析、人工智慧神經網路訓練及推理、高階智慧型手機、自駕車的行動運算等領域。2019年台積電展示自行設計的小晶片This採用7奈米製程技術,CoWos封裝技術,面積僅27.28平方毫米(4.4mmx6.2mm)。台積電近年整合SoIC(系統整合晶片)、InFO(整合型扇出封裝技術)、CoWoS(基板上晶片封裝)等3D IC技術平台TSMC 3DFabric,提供多用途Chiplets解決方案。

除了中國著重化合物半導體,全球指標性半導體大廠包含記憶體大廠Samsung、邏輯運算大廠台積電,以及CPU大廠Intel。國研院半導體中心副主任莊英宗與謝嘉民咸認,三大業者在小晶片發展上各有擅長,呈鼎足之勢,5-10年內沒有打破現狀的可能,不過,台積電可能會花更多心力在小晶片研發與製程,「台積電有太多高低階晶片可以搭配,所以更需要小晶片技術。」謝嘉民說。

莊英宗認為,封裝技術的決勝點在multi chip與cost down,良率要夠才能cost down,幾大廠都在精進中,但台積電「武功練最好」,勝出原因是「很聚焦」,比Intel、Samsung更多元,「台積電取市場極大化作法,3DFabric的後端製程CoWoS和InFO系列的封裝技術都掌握得非常好,所以主流市場仍由台積電掌握。」

| 圖五 : 運用小晶片技術的太空用高效能處理器(HPSC Chiplet)。(Source:國研院半導體中心) |

|

小晶片發展需要克服的挑戰

小晶片雖然具有異質整合優勢,但目前幾家國際大廠提出的小晶片解決方案主要針對超越摩爾定律(More than Moore),投注的資源也最多、產能最大、效益最高,然而,單一系統晶片模組要最大化必須透過密集、高速、高頻寬連結,才能確保最佳效能水準、傳輸速度及功耗效益,因此,未來小晶片仍有諸多挑戰需克服。

【挑戰1】技術問題

小晶片組裝或封裝仍缺乏統一標準,各大廠都有自家方案,雖然名稱不同,離不開TSV和高密度技術。謝嘉民說,不論是晶片堆疊還是大面積拼接,都有製程上的挑戰,「小晶片要拋薄,要用不同材料,立體化高密度下,封裝技術的挑戰超乎想像,比方散熱、應力、訊號傳遞互不干擾等問題都要一一克服。」

【挑戰2】品質問題

SoC是一片晶片中製造不同功能區,小晶片則是由獨立晶片功能透過封裝堆疊完成終極功能。與SoC不同,小晶片只要其中一個晶片出問題,整個系統都會受影響,付出的代價很高,因此,小晶片必須被獨立測試、獨立運作以確保品質無虞。

【挑戰3】散熱問題

幾個甚至數十個晶片封裝在同一個空間中,互連線極短,散熱處理更為棘手。

【挑戰4】晶片互聯標準

小晶片目前還沒有共通的互聯標準,而是開發商與客戶自訂標準。小晶片需要彼此互聯的通訊互聯標準才不至於互連後Dead Lock(閉迴路)。單一小晶片的通信系統也許可以很好地工作,但是當小晶片全部連接在一起形成晶片網絡時,就可能出現死鎖與流量堵塞等問題。

【挑戰5】供應鏈整合

電子設計自動化EDA(Electronics Design Automation)工具在半導體製造中越來越重要。在小晶片模式下,EDA工具商、晶片商、封測商都要與時俱進做出改變,比方小晶片模式出現問題可能需要EDA工具從架構探索甚至物理設計方面提供全面支援,不同晶片商、封裝商的進度也需要同步。

【挑戰6】SdC Tool

工研院資通所組長許鈞瓏指出小晶片倉庫(IP Mall)、架構探索與效能分析(Sowhere Defined Chiplet)工具的重要性,前者可以依產品需求挑選不同製程、功能的小晶片,後者可以檢測前者的效能與良率狀況,「這個Tool可以有效評估小晶片兜在一起時的整體表現,如晶片面積、功耗、散熱、訊號、成本等效益。」

| 圖六 : IntelEMIB技術,此LSI(local Si interposer)用以連結不同Die,同interposer概念。(source:國研院半導體中心) |

|

小晶片與SoC共存互利 各領風騷

小晶片具有異質整合能力,也被視為突破摩爾定律(Moore’s Law)物理極限、提高晶片運算力、降低成本的良策,它會是摩爾定律的「最後一棒」,甚至取SoC而代之嗎?工研院資通所組長許鈞瓏認為,小晶片會不會是摩爾定律的最後一棒很難說,但繼續夯個十年應該沒問題,「設計、封裝等面向都有持續改善的空間,未來還會在這個方向上繼續精進發展。」

他進一步說明,小晶片是把晶片的某些特定功能做成很小的die,台積電的CoWoS、Intel的EMID都是封裝技術的突破,目的是為了異質整合,不用像SoC在同一製程下封裝。不過,小晶片在應用端上主要是高速運算部分,適合少量多樣產品,如追求快速、低成本的AI、服務型機器人、自駕車等,「越智能越需要小晶片,比方服務型機器人具有影像及聲音辨識功能,如果想更新其中一部分功能,只要更換小晶片上的一顆Die即可。」SoC系統晶片則適合生命週期較長、量大、短期不須置換或更新的產品,如手機晶片,「就算蘋果推出新產品,具有照相、運算、視訊等功能的SoC板基本不會變,這類產品用不到小晶片。」

與AI有關的晶片如CNN卷積神經網路(Convolutional Neural Networks)及RNN遞歸神經網路(Recurrent Neural Networks)晶片做在一塊SoC裡成本相當高,「AI是不斷學習、智能導向,用SoC做死就沒有功能了,但小晶片可以找到相對應的功能,成本較低,置換也比較容易。」未來如有其他智能需求,如語言需求,可以搭NLP(Natural Language Processing)晶片,不同智能需求堆疊不同的小晶片,量身打造客製化、機動性高的產品。由於日常生活不太需要與航空、軍事或AI運算有關的高端產品,因此,小晶片不會完全取代SoC,兩者各有擅長,視產品需求、成本等考量選擇適合的技術。

國研院半導體中心副主任謝嘉民強調,小晶片不是新概念,但新的應用方式可以增強驅動能力,「讓小晶片發揮更好的效能,必須克服研發與製程問題,整合好就能用得更好。」

國研院半導體中心副主任莊英宗從異質整合角度看小晶片未來發展,他認為多晶片IP發展已相當精緻多元,許多大廠搶食這塊大餅,卻忽略IoT等新創事業的發展性,「IoT未來趨勢很多,profit很大,因為不容易做,所以實現的很少。」日、韓等國已著墨小晶片多樣性少量製造如車用感測器等產品,「未來小晶片的決戰場可能在IoT,建議政府、產學界加速推動。」