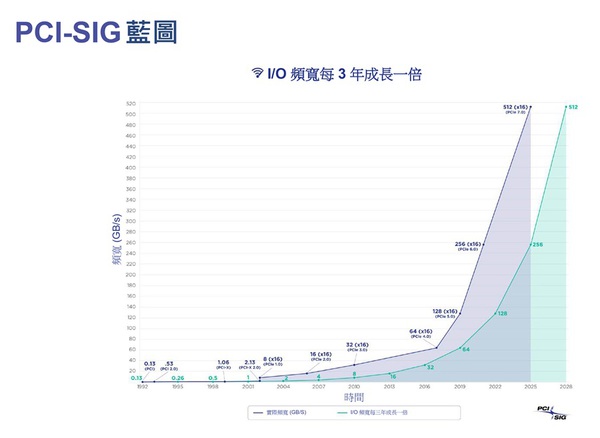

隨著PCIe技術的不斷進步,其測試驗證的複雜性也日益增長。為了滿足日益增長的速度需求,每一代PCIe的演進都實現了傳輸速率的翻倍。如今,全球各地的資料中心已經開始採用最新版本的PCIe 5.0和6.0電纜來連接大量高速資料存放裝置。與此同時,電纜製造商也在積極生產,以向客戶交付首批PCIe 5.0和6.0電纜。

更高速的傳輸纜線

PCIe測試驗證不僅需要先進的測試設備和技術,還需要嚴格遵守PCI-SIG規範,以確保測試結果的準確性和可靠性。

為了確保這些高速電纜符合PCIe標準並保證整個系統的正常運行,研發驗證、合規性和製造過程都需要進行徹底的測試。每個PCIe鏈路具有不同數量的通道對,包括1、2、4、8或16對,每對通道由一組差分發送(TX)和一組差分接收(RX)通道組成。以PCIe 6.0電纜為例,採用x8配置的電纜可以實現高達64 GB/s的傳輸速率。

然而,手動驗證高速互連的合規性不僅工作量大,而且容易出錯。對於電纜的所有Thru連接以及電纜內部的近端和遠端串擾路徑,需要進行大量的四埠測量。傳統的四埠向量網路分析儀在每次測量時都需要重新連接,並且需要正確終端化未測量的差分對,這無疑增加了測試的複雜性和難度。

在PCIe 5.0/6.0系統行為測試中,某些遮罩限制值的偏差可能並不關鍵。通過或失敗判定主要取決於整合回波損耗(iRL)和串擾雜訊分量(ccICN)等度量。這些度量在PCI-SIG規範中定義,需要從S參數結果計算得出,並需要進行大量的後處理工作。此外,校準測試夾具特性也帶來了額外的挑戰。

鑒於PCIe系統的重要性,PCI-SIG正在制定用於內部(主機殼內部)和外部(主機殼到主機殼)應用的標準化電纜規範。這些規範包括在32 GT/s和64 GT/s速率下配對的電纜元件和配對線纜連接器的相應電氣要求,以確保整個系統的穩定性和性能。

因此,對於PCIe測試驗證而言,不僅需要先進的測試設備和技術,還需要嚴格遵守PCI-SIG規範,以確保測試結果的準確性和可靠性。隨著PCIe技術的不斷發展,測試驗證的難度和複雜性也將繼續增加,但這也將推動測試技術的不斷創新和進步。

測試設備考量

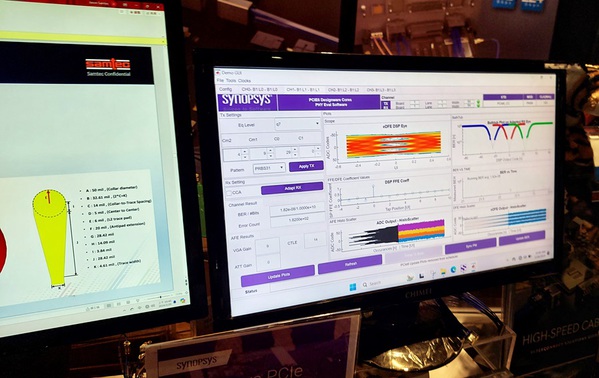

| 圖一 : 示波器和網路分析儀,是PCIe測試驗證中不可或缺的設備。 |

|

隨著PCIe技術的不斷發展,資料速率的提升使得高速串列資料連結的設計愈發複雜。特別是通道拓撲的多樣化以及主動元件需要調整的參數數量激增,對設計和測試增加了更高的挑戰。

高速信號測試設備,如高性能示波器和網路分析儀,是PCIe測試驗證中不可或缺的設備。這些設備能夠支援更高的資料傳輸速率,如PCIe 6.0的64GT/s,並具備足夠的採樣頻寬和精度,以捕捉和分析高速信號中的細微變化。

專門的PCIe測試解決方案也是必不可少的。這些解決方案通常包括一系列的軟體和硬體工具,用於模擬、研發和驗證PCIe設計的各個方面。此外,誤碼率測試儀和即時示波器等設備也是PCIe測試中的重要組成部分。BERT能夠類比各種信號條件,以驗證被測設備在不同環境下的性能表現,而即時示波器則用於對PCIe信號進行即時採樣和分析。

針對PCIe測試驗證的最新標準,還需要關注設備供應商發佈的最新產品和解決方案。隨著PCIe技術的不斷發展,新的測試設備和解決方案會不斷湧現,以滿足更高的測試需求。需要注意的是,為了確保測試的準確性和可靠性,選擇設備時除了考慮其性能參數外,還應考慮其是否符合PCI-SIG等權威機構制定的標準和規範。同時,與設備供應商的技術支援團隊保持溝通,以確保獲得最新的技術支持和解決方案。

PCIe 6.0正在開發中,以滿足新興應用的高速數據傳輸需求。隨著數據速率翻倍和其他增強的性能規格,PCIe 6.0將增加高速互連設計的複雜性。工程師需要選擇合適的信號完整性測試解決方案,來驗證他們的產品是否符合 PCIe 6.0 標準。為了確保PCIe測試驗證的準確性,需要一系列先進的測試設備來支援。這些設備包括:

●誤碼率測試儀(BERT)和脈衝模式發生器(PPG):用於進行高精度的特定信號測量。BERT和PPG在PCIe測試中發揮著關鍵作用,能夠類比和生成各種信號條件,以驗證被測設備在不同環境下的性能表現。

●BERT誤碼檢測器(ED):用於分析Serdes輸出的誤碼率(BER)。ED能夠準確檢測信號中的錯誤,並提供誤碼率資料,?明工程師評估PCIe設備的性能。

●即時示波器:需要採樣頻寬大於50 GHz,用於對PCIe信號進行即時採樣和分析,檢測信號的波形、時鐘抖動等參數。即時示波器能夠提供詳細的信號資訊,?明工程師診斷和解決潛在問題。

此外,針對PCIe 5.0和6.0等更高級別的測試,還需要支援更高速率和更複雜測試方案的設備。例如,鏈路均衡訓練測試需要BERT模擬一個參考Serdes,並與被測設備(DUT)在PCIe協定的PHY邏輯子區塊進行交互。這要求測試設備具有更高等級的模擬和交互能力。除了上述核心設備外,還可能需要其他輔助設備,如測試夾具、校準設備等,以確保測試的準確性和可靠性。

目前測試大廠是德科技(Keysight)就推出了端到端的PCIe 5.0/6.0測試解決方案,涵蓋了從模擬到實體層和協議層的測試需求。是德科技的PCIe測試解決方案包括模擬、研發和驗證工具,能夠支援從PCIe 3.0到PCIe 6.0等各個版本的測試需求。太克科技(Tektronix)則提供了高性能的示波器,用於即時捕獲和分析高速PCIe信號。安立知(Anritsu)的PCIe解決方案能夠支援PCIe設備的性能評估和一致性測試,確保設備符合相關標準和規範。羅德史瓦茲(R&S)則與PCI-SIG密切合作,針對PCIe架構的一致性測試提供了廣泛的解決方案。這些解決方案不僅可用於一致性測試,還可用於高效驗證和系統級設計,包括存在其他介面和無線信號的複雜場景。

加快合規測試速度

| 圖二 : 每一代PCIe的演進都實現了傳輸速率的翻倍。圖為PCI-SIG的發展藍圖。 |

|

為了準確快速地進行符合PCI-SIG規範的最新一代PCIe 5.0和6.0電纜和連接器的合規性測試,R&S開發新的向量網路分析儀自動化套件選項。例如,對於完全自動化驗證PCIe x8電纜,軟體可以控制一個由ZNB向量網路分析儀和可擴展的OSP開關矩陣配置組成的測試裝置,創建一個具有64個測試埠的多埠VNA解決方案。該解決方案將PCIe x8電纜的測試時間縮短到僅幾分鐘,包括所有Thru連接、所有串擾組合以及相應的度量計算,以進行通過與失敗評估。相比之下,手動測試需要數小時,並且測試工程師可能存在連接錯誤的重大風險。

新的向量網路分析儀自動化套件選項,可應對PCIe 5.0和6.0電纜和連接器的合規性驗證挑戰。R&S ZNrun-K440專為根據PCI-SIG規範自動進行PCIe 5.0和6.0內部和外部電纜和連接器的合規性測試而設計,為用戶節省了大量時間。測試裝置配備四個測試埠,並結合多個開放式開關和控制平台,根據要驗證的設備通道數目而定,提供多個四埠測量,而無需重新連接到DUT並重複其它通道的終端電阻插拔。例如,PCIe x8電纜具有16個通道,需要64個測試埠,由三個OSP320平台提供,而PCIe x4電纜只需要兩個OSP320平台提供32個測試埠。

R&S ZNrun-K440解決方案自動化符合PCIe規範的所有測量。還包括對定義的PCIe度量進行後處理。測試配置器可對個別通道進行選擇和取消選擇測試,提供更大的靈活性,以滿足研發和驗證測試中客戶的需求和偏好。自動化測量結束時生成帶有通過或失敗判定的測試報告。該自動化功能採用新的校準程式,顯著減少了校準步驟和校準連接的數量。它還包括了符合PCIe測試規範所需的測試夾具去嵌套方法。

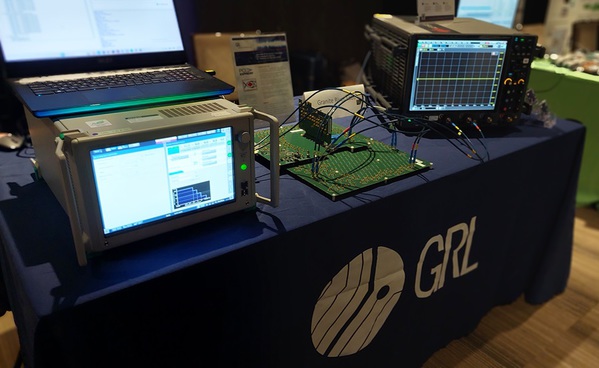

| 圖三 : 選擇適合的測試設備是確保驗證成功的關鍵。圖為GRL,PCI-SIG的官方測試認證機構。 |

|

PCIe 6.0基本規格測試系統

安立知也以其訊號品質分析儀 MP1900A 系列,搭配太克科技的即時示波器,以及通過矽驗證的 Synopsys PCI Express 6.0 IP,成為一套PCIe 6.0基本規格測試系統。PCIe 6.0利用前向糾錯技術,確保SNR訊號之完整性,其結果是評估待測物複雜度更高。更高效率的測試方案,是使用即時示波器執行自動基本規範校準和訊號品質評估,並結合安立知支援糾錯分析的MP1900A以即時測量FEC誤碼率。

MP1900A訊號品質分析儀是一款高性能的誤碼率測試儀(BERT),可用於測量諸如PCIe 6.0、PCIe 3.0至5.0和USB3.2/4.0等高速運算介面,以及包括400GbE與800GbE等超寬頻通訊介面。MP1900A兼具測試重現性和簡單的操作等優點,是一款經PCI-SIG認證的儀器,可用於高達PCIe 5.0的一致性測試。

優化信號完整性

在PCIe設計與模擬方面,是德科技提供模擬工具,可以優化PCIe設計的信號和電源完整性。同時,這些工具還能夠分析高速IC封裝和PCB互連等元件的電磁效應,確保設計的穩定性和可靠性。快速有效地評估PCIe 6.0鏈路的端對端性能,可以為使用者提供有力的設計驗證支援。

在PCIe發射器測試方面,PCIe 6.0從NRZ轉變為PAM4,眼圖高度從PCIe 5.0的15mV縮小到只有6mV,帶來了更大挑戰。是德提供了最佳化雜訊性能的示波器,能夠準確測量低至6mV的眼圖高度。此外,Keysight FlexPLL支援速度最快的發射器鎖相環(PLL)頻寬測量,將測量時間從幾小時縮短到數秒,提高了測試效率。

結語

PCIe測試驗證需要一系列專業的測試設備支援,這些設備不僅具有高精度的測量和分析能力,還需要支援高速率和複雜測試方案。選擇適合的測試設備是確保PCIe測試驗證成功的關鍵之一。

支援PCIe測試驗證標準的設備涵蓋了高速信號測試設備、專門的PCIe測試解決方案以及BERT和即時示波器等關鍵設備。在選擇設備時,應綜合考慮其性能參數、符合標準情況以及技術支援等因素。許多廠商都提供了針對不同PCIe版本和測試需求的解決方案,包括硬體測試設備、模擬軟體、驗證工具等。隨著PCIe技術的不斷發展和新版本的推出,測試廠商也會不斷更新和升級他們的測試解決方案,來滿足市場需求。