由於Si/SiGe/Si所具有的異質性介面特性,以及與主流Si-技術製程的相容性,將開啟新一代微電子技術潮流,其元件應用主要可分為兩大類:一.Heterojunction Field Effect Transistor(HFET);二.Heterojunction Bipolar Transistor(HBT)。其中HBT首先驗證於1988,之後就有快速進展,截止頻率從開始的30GHz推到目前130GHz,直逼GaAs特性。今天SiGe HBT已漸屬發展成熟技術,正導入量產階段。

隨著無線通訊蓬勃發展,其相關RF ICs需求日益殷切,找尋低成本、高效益、高集積度的製程技術來配合IC設計更是急迫。具有優異高頻特性,以及易與CMOS整合成BiCMOS的SiGe技術,無疑將是最佳選擇,而且預估可涵蓋到更高頻的MMICs,以及高速類比/數位混合式ICs上,目前全世界各大半導體廠商無不開始積極研發或列入下一世代重點技術;亦有相當多研究機構進一步將各式高頻/高速主動元件和被動元件與SiGe HBT整合,應用在Millimeter Wave Sensor、Communication上,以及利用SiGe/Si異質性結構製作Optoelectronics元件,應用在OEICs產品上;可說是一種甚具實用性與前瞻性的技術。

本文首先扼要闡述SiGe HBT元件物理與特性,據此與其它技術的元件如CMOS、Bipolar、GaAs(MESFET、HBT)作一廣汎的比較,以瞭解各種技術應用在高頻/高速ICs的利基所在。接著討論SiGe HBT的關鍵製程技術,包括各式SiGe薄膜成長技術、不同元件結構、和SiGe BiCMOS整合技術。

之後兩個章節則分別討論SiGe HBT/BiCMOS的量產問題及其產品應用,前者主要是依據IBM近年來多次所發表的資料來說明;後者則以SiGe HBT元件的高頻特性,來推測其產品應用範圍及市場,並以各家公司在網路上所張貼的產品網站為佐證。最後對國內產、官、學對SiGe技術研發作一扼要描述,期望為國內半導體業再開創另一新的局面。

SiGe HBT元件特性與技術比較

基本上,SiGe HBT利用射極(Poly-Si)與基極(SiGe)的能帶間隙差異(7.4 mV/% Ge Content),來提高射極的注入,因此可降低射極攙雜濃度和提高基極攙雜濃度。在可避免射-基極間的隧穿(Tunneling)效應下,來提高射-集極間的穿透崩潰電壓(Punchthrough)。且可同時降低基極寬度和電阻,達到優異高頻特性,如高截止頻率、低雜訊。

以上基極SiGe層的Ge含量為箱形分佈(Box Profile),例如Ge含量增加所引起介面能帶間隙差異,將等效提高基極之QB值(寬度x濃度),如此可增加元件設計的彈性;或祇增加基極濃度以大幅降低基極電阻;或增加基極濃度且縮短基極寬度,在降低基極電阻的同時可提高元件截止頻率。

另一種作法則是SiGe層的Ge含量屬漸昇式分佈(Graded Profile),其在射-基極介面Ge含量從零漸昇到基-集極介面的適量值(如15%),因隨著Ge含量的漸變在基極區內的能帶亦隨著漸變,如此將在此區內造成內建電場,加速注入載子移動速率,達到降低注入載子的延遲時間。元件設計上可由Ge含量分佈的調變來改變內建電場大小,再適當提高基極濃度,以同時達到低基極電阻和高截止頻率的目標。

其對於介面Band Diagram和元件特性的影響可用(圖一)表示。在射-基極介面因Ge含量造成有一能帶間隙位能差,△Eo,有利於射極載子注入及提高電流增益;在基極區內由於Ge攙雜量漸增,能帶間隙漸窄,將內建一電場加速注入少數載子的傳導,而減低傳導延遲時間及提高截止頻率;另外由於射極注入效率提高,可相對提高基極濃度,可減少集極電壓對基極寬度的調變,即減少集極電流對集極電壓的變化而提高其VA電壓(Early Voltage),加上由前一項電流增益提高,兩者乘積,GainxVA,將大幅提昇極有利於類比電路的設計。

Bipolar/CMOS/GaAs技術比較

選擇適用於無線通訊產品的IC製程技術,一直有很大爭論,尤其在所謂的RF CMOS加入戰局之後;過去幾年以來RF ICs零組件有各種方式被提出,包括Bipolar(Si/SiGe HBT、BiCMOS)、CMOS、GaAs MESFET和HBT。雖然最終的考量應是經濟因素,能以最低成本和最快時間將產品推出市場的將是最大贏家;但各種製程技術的高頻特性,無疑是開發階段中作為評估的重要依據。

基本上GaAs(MESFET、HBT)其高頻特性是優於Si BJT(CMOS),但在Si BJT(CMOS)不斷降低尺寸、提昇效能情勢下,GaAs已無法像CMOS在數位IC技術中一樣一直佔有主流地位,如果Si BJT(CMOS)高頻特性能進一步滿足電路規格要求,在成本和整合性的考量之下,無疑將漸漸取代GaAs。如果將電流損耗、被動元件整合性、製造複雜度考慮進來,理想RF ICs製程技術應該同時能達到低雜訊、高線性、低電流損耗、高度整合性、低製造成本的要求。

將各種製程技術不同特性比較整理如(表一),可發現SiGe HBT/BiCMOS可提供極佳選擇;其中RF CMOS最近雖一直有很多進展,分別從元件佈局設計、多晶矽閘極電阻降低,顯示在0.15um以下CMOS元件其高頻特性甚至可超越Bipolar元件;以Toshiba的0.15um RF CMOS為例,可達到fT=42 GHz、NFmin=1.4dB(at 2GHz)。但MOSFET有一先天限制,其Noise Figure反比於Transconductance(gm),在低汲極電流時gm甚小,造成其NFmin遠大於最低值;相對於Bipolar元件要達到相同的Noise Figure,CMOS需要更高電流或更大面積來達成,對講究低耗電的可攜型無線電終端產品來說並不利,仍需時間加以克服。

SiGe HBT/BiCMOS整合製程技術

SiGe HBT製作

SiGe HBT製程技術除需要另外成長SiGe薄膜當作基極外,並需與傳統Si-Bipolar完全相容,因此在SiGe HBT研發過程中SiGe薄膜的成長無疑將是成功與否的關鍵。(圖二)簡要顯示SiGe HBT不同的SiGe薄膜磊晶成長和元件結構,以及相關製程流程和代表廠商。

SiGe薄膜磊晶成長技術包括有Blanket、Differential、Selective三種成長方式,和MBE(Molecular Beam Epitaxy)、RTCVD(Rapid Thermal Chemical Vapor Deposition)屬廣義的稱呼,另外包含有LRP(Limited Reaction Processing)、AP(Atmospheric Pressure)、LP(Low Pressure)成長型式、UHV/CVD(Ultra High Vacuum Chemical Vapor Deposition)三種成長製程設備,其中MBE屬研究性質較不適合用來製造生產,另外兩種技術則廣為半導體業界所採用。

元件結構則分別有Mesa-Type、Single-Poly Quasi-Self-Aligned,Double-Poly Self-Aligned三種型式,其中Mesa-Type不易整合成ICs;以不同機台的適用性來考量,目前以MBE Mesa-Type(Blanket)、UHV/CVDSP(Differential)、RTCVDDP(Selective)為較佳組合,MBE因較不適合量產將不作進一步討論。

在未進一步討論HBT製作之前,有必要先對SiGe Strained Layer特性作一番探討;Ge原子晶格常數略大於Si原子,在Si基材上所成長的SiGe薄膜屬形變層(Strained Layer),其品質與成長環境、溫度、Ge攙雜量有密切關係,易有缺陷產生而影響元件特性;因此SiGe薄膜的成長條件、和後續製程整合的配合都需詳加考慮。

◆RTCVDDP(Selective)

基本上延續傳統Si-Bipolar的雙層複晶自我對準結構,主要差別在於HBT其基極改由SiGe薄膜磊晶形成,主要發展廠商有Philips、Siemens、NEC、Hitachi。矽化鍺薄膜磊晶屬RTCVD成長方式,具有寄生電阻、電容低,和與現有Bipolar製程相容的優點。但此矽化鍺薄膜是在預設的射極窗以選擇性磊晶長成的,其過程不易掌控,除易在其它非晶系區域Nucleated,和有嚴重Micro-Loading效應外,亦易由側邊的基極複晶層形成一不同於由射極窗往上成長的晶面,成為射-基極間主要漏電來源,皆為此種結構進一步要解決的課題。

◆UHV/CVDSP(Differential)

此方法為IBM所專利的作法,其SiGe層同時在晶系與非晶系區成長,祇是在晶系區長成單晶的內在基極層,而在非晶系區則長成複晶的外在基極層層,將作為後續基極拉線接觸之。SiGe層長好之後,後續製程除需要一高品質低溫氧化層成長外,類似於傳統單層複晶的Si-Bipolar。此種作法雖然射-基極區非自我對準,但在製程能力愈精細情況下其結果將與前述雙層複晶自我對準相同,且製程易與CMOS結合形成BiCMOS,將為下一節SiGe BiCMOS討論重點。

SiGe BiCMOS製程整合

SiGe BiCMOS的製程也是與Bipolar一樣的分為Single-Poly與Double-Poly兩種製程,其中Single-Poly BiCMOS的製程是以IBM公司所提出的製程最具代表性。此製程是最具關鍵之處是利用在沉積SiGe基極時一同製作複晶閘極層,亦即在SiGe Base層沉積之前會先成長閘氧化層,然後接著進行SiGe層成長。

此沉積過程不僅是在晶系區成長單晶的內在基極層,也可以於場氧化層之上沉積外在基極層,並於閘氧化層之上製作出複晶閘極層,然後再製作射極複晶結構。至此Bipolar的部份製作完成,接著進行複晶閘層的蝕刻、LDD離子植入、Spacer的製作、源極和汲極的離子植入、熱退火製程,以及後段的金屬化製程後,即完成Single-Poly SiGe BiCMOS的製作。

SiGe HBT/BiCMOS產性與可靠性

新技術的開發最後要能達到應用的階段,需要通過可量產特性的驗證,包括製程再製性、良率,及可靠性的試驗。IBM在1997年以超過17 Wafer Runs,總共200片SiGe用UHV/CVD成長的的200mm晶片,來檢證HBT元件關鍵製程參數-基極片電阻(Rpb,Pinch Base Sheet Resistance,(Ω/sq)的均勻性,顯示每片Site-to-Site偏離該片平均值的偏差量小於8%,而Wafer-to-Wafer偏離全平均值的偏差量(3-Sigma)則小於39%,再製性結果優於一般傳統Bipolar元件和III-V技術。

主要原因應來自於SiGe HBT的磊晶型基極濃度峰值位於射基極介面之下,有別於傳統植入型基極其濃度峰值會在射極攙雜離子推入時被消耗掉,造成雙載子電晶體特性的均勻性不佳,尤其是頻率要求更高時製程將會更難掌控。

其次,電晶體良率可由串聯4000個HBT(AE=0.5(2.5um2)元件的Test Chains來估算,其Failure Mode屬射-集極之Piping造成集極電流漏電。而在整個200 mm晶片上則有9個Fail Dies,依此推算其良率為87%,進一步推算Single Transistor的良率可達到99.994%,如此高的良率已達到可作LSI整合的程度。

德國IHP(Institut fur Halbleiterphysik)亦在1998年利用RTCVD成長SiGe Base來驗證SiGe HBT的可量產性,結果顯示在射極面積為104 um2(相當於8000個射極面積為0.5(2.5um2的元件)良率為90%,其樣本空間為100mm的晶片600片,對應於IBM兩者有相當類似的結果。另外亦將具有1.8 M Transistors CMOS ASIC 晶片以SiGe BiCMOS製程製作,其產品特性完全不受影響,表示其製程整合良好,不影響CMOS特性,可具量產能力。

此外,SiGe HBT元件經過反向電壓試煉(Stress),所造成劣化(Degradation)程度優於一般矽雙載子電晶體,可部份歸因於射基極介面之Ge元素有降低其介面間電場之作用,而有效改善元件可靠度。IBM亦同樣證實元件在125℃環境溫度下經過1mA/um2電流密度試煉下,其Mean-Time-to-Failure(MTTF)可超過1E7 hrs。

SiGe HBT/BiCMOS應用及市場

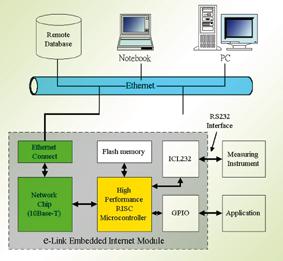

根據1998BCTM研討會上,Daimler-Benz的Konig推測在2~30GHz操作頻率範圍內SiGe將可逐漸取代GaAs成為主要通訊IC製程技術;SiGe Microsystems公司如(圖三)更明確指出SiGe技術應用頻段範圍,主要可分為三大應用範圍:

| 《圖三 SiGe HBT/BiCMOS在各個頻段應用機會》 |

|

◆ Wireless Communications

◆ Navigation/aerospace

◆ Automotive Applications

另外還包括High-Speed A/D & D/A。不過由圖三亦顯示出三種技術(Si CMOS/Bipolar、SiGe HBT/BiCMOS、GaAs FET/HBT)彼此之間的消長,在5.0GHz頻段範圍以下,成本僅比Si技術高出10 %的SiGe技術,在Performance考量之下應會被優先採用;而在較高頻段(20GHz)以上,雖Performance遜於GaAs,但因其成本遠低於GaAs技術,且具有高整合度,無疑地SiGe技術仍有其廣大發展空間。

IBM從1994年以來不斷有以SiGe HBT技術來設計的驗證電路發表,舉其要者整理如下(表二)。

從1998年10月,IBM首先推出第一顆商品化產品,到最近已有多家廠商陸續發表SiGe相關產品,如Atmel的PA(GSM)、DSP的RF chip(PDC)、Maxim的LNA/Mixer(GSM);尤其IBM更是與Alcatel、AMCC、Harris、Hughes Electronics、National Semiconductor、Nortel、Tektronix策略聯盟,採取IBM’s SiGe HBT/BiCMOS技術技術來開發眾多高速IC,分別應用在Wireless、Network、和Test-Instrument上。其相關產品特性規格型號整理成如(表三)所示。

| 《表三 發表SiGe HBT/BiCMOS產品型號/規格》 |

|

現階段SiGe產品雖然種類不多、量亦少,但一般推測其未來將有很大發展空間,據Strategies Unlimited公司預估未來潛在市場,單SiGe RFICs可從去年US$15M快速成長到2005年的US$1.9B,約佔RF ICs市場總值10%以上,極具市場潛力。

WW SiGe HBT/BiCMOS發展現況

至今全世界至少有30家廠商投入SiGe ICs製程與電路的研發,舉其要者除了北美的IBM、AMCC、AMP、M/A-Com、Analog Devices、Harris、Hughes Electronics、Lucent、Maxim、Motorala、National Semiconductor、Nortel、SiGe Microsystem,還包括歐洲的Daimler-Benz AG(Temic)、Philips、Siemens、GEC Plessey、SGS-Thomoson和日本的Hitachi、NEC、NTT。

其中AMCC、AMP、M/A-Com、Analog Devices、Harris屬設計公司與IBM策略聯盟,利用IBM的製程技術共同開發高頻/高速相關積體電路;而上面歐洲五家主要半導體廠則組成TIBIA協會(Technology Initiative in BiCMOS for Application),成立Esprit Project 8001計畫來推動SiGe HBT技術開發,並已有優越成果,在1995年IEDM研討會中發表多篇論文,於”Advanced Bipolar Device”章節中佔了幾乎一半的文章。

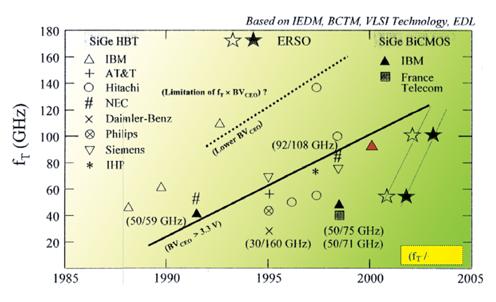

將這幾年來各家所發表的SiGe HBT/BiCMOS技術整理成(圖四),以其元件的截止頻率(fT)作一參考指標,可發現HBT從一開始的30 GHz快速推展到目前130GHz,如果另外考慮BVceo需要達到目前一般操作電壓3.2伏特的限制,則fT快接近100GHz可達90GHz左右,其可應用範圍大幅提高,如上一節所述。在技術研發上最近有幾個訊息值得注意:

| 《圖四 各家廠商SiGe HBT/BiCMOS技術發展趨勢》 |

|

◆一.Motorala與IHP合作研發SiGeC技術:

去年5月通訊大廠Motorala與德國研究機構IHP(Institut fur Halbleiter Physik)合作開發SiGeC技術,將利用Motorala’s CMOS廠建立IHP’s SiGeC HBT技術和SiGeC BiCMOS技術,以開發下一代無線通訊產品;所代表的意義有二,一為通訊大廠體認到SiGe技術應用於高階但成本遠低於GaAs產品的時代已來臨,一為攙有C原子以提高SiGe薄膜穩定性及降低p型基極B原子擴散的SiGeC技術,已通過驗證將達量產階段。

◆二.高速SONET產品相繼推出:

分別有IBM、Lucent、AMCC、Siemens推出,其中AMCC與IBM結盟利用IBM’s SiGe BiCMOS技術來設計,Siemens則開發其第七代高頻雙載子電晶體製程(SiGe:B7HF),來設計其高階Gate-Array-Based Clock/Data Recovery Circuit;其代表的意義是SiGe技術不祇應用於RF ICs上,高速傳輸的介面ICs亦是一可大大發揮的應用領域,其速度可推到40Gbps以上。

以上討論偏向廠商的發展,其實歐、美、日凡與微電子研究有關的主要大學/研究機構,幾乎都有在從事SiGe這方面的研究,涵蓋範圍極廣,舉凡薄模成長(SiGe/SiGeC;MBE/RTCVD/UHV CVD)、元件開發(SiGe HBT/MODFET/MOSFET;Optoelectronics)、電路應用(RF ICs/OEICs/High Speed IC)。

SiGe/Si異質性介面結構除了在HBT應用上有快速進展外,另外在HFET、Optoelectonics亦不斷有人研究,預期將開創新的應用領域。以下分別依其元件結構/特性、製程技術、研究機構作簡要說明:

◆HFET(Heterojunction Field Effect Transistor):

分有MODFET和QW MOSFET兩種結構,其間主要差別在於後者需要有類似Si-MOSFET的Gate Oxide,兩者皆利用Si/SiGe/Si/SiGe等多層異質介面結構,以形成量子井(Quantum Well)提高載子傳導速率,理論上在常溫下可增加2~3倍,極適合在低壓、高速系統應用;基本上QW MOSFET與CMOS製程比較匹配,祇另需要一高品質低溫成長的氧化層,但目前實驗結果特性尚不理想,MODFET元件倒有較好結果;在此領域已獲具體成果的機構有IBM、Daimler-Benz、DRL/UCLA、Cavendish Lab.。

◆Optoelectonics Device:

同樣也是利用Si/SiGe/Si/SiGe等多層異質介面結構,已開發出各式SiGe-Based光電元件,如Optical Wavequide、Electrooptic Modulator、Photodetector for 1.3~1.6 um、Optical Switches;主要研究機構包括Rome Lab.(AFRL)、DRL/UCLA、Cavendish Lab.

最後,以整合成Si-Based OEICs為理想,其中包含不少SiGe關鍵元件,英國劍橋大學的Cavendish Lab.描繪出未來籃圖如下(圖五)。

結語

SiGe技術經過這十幾年的研究發展,最近幾年來已漸漸開花結果,除了研發廠商家數逐漸增加外,也陸續有不少商品化產品推出,並且應用範圍日益擴大,不祇應用的頻率愈高、速度愈快,亦利用異質介面特性開發出光電元件,並朝OEICs領域邁進。

綜觀國內半導業界長久以來,在考慮市場需求下幾乎集中於數位CMOS製程技術及相關ICs設計上,相對於高頻/高速/類比的就著力少了許多,造成無線通訊蓬勃發展的今日在這方面的製程與設計卻兩者皆缺失的窘境,而且此情況在未來整合度要求越來越高的3C時代,將日益嚴重,亦即對高頻/高速/類比的製程與設計需求將日益殷切。

由於國際上SiGe技術目前正屬急速發展階段,國內之切入刻不容緩,以求得掌握關鍵技術並加以創新。過去工研院電子所三、四年來累積不少Si-Bipolar的研發經驗,並於今年度首先建立SiGe薄膜磊晶量產機台,開始SiGe技術的研究與開發,包括有SiGe HBT、SiGe Photodetector、SiGe HFET;另外幾個國內半導體大廠亦陸續宣佈投入SiGe HBT技術開發,再加上國內學術界包括交大、台大多年來有關SiGe技術的基礎研究,未來產、官、學三方面的密切結合,將可再為國內蓬勃發展的半導體業再開創另一新局。