一些晶片大廠近期宣布在其邏輯晶片的開發藍圖中導入晶背供電網路(BSPDN)。比利時微電子研究中心(imec)於本文攜手矽智財公司Arm,介紹一種展示特定晶背供電網路設計的設計技術協同優化(DTCO)方案,其中採用了奈米矽穿孔及埋入式電源軌來進行晶背佈線。他們展示如何在高效能運算應用充分發揮該晶背供電網路的潛力,並介紹在標準單元進行晶背連接的其它設計選擇,探察晶背直接供電方案所能發揮的最大微縮潛能。

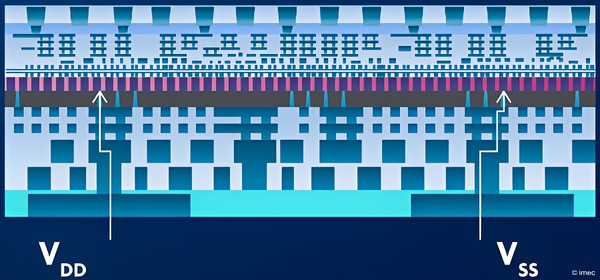

長久以來,訊號處理與供電網路都在矽晶圓正面進行,晶背供電技術打破了這種傳統,把整個配電網路都移到晶圓背面。矽穿孔直接讓電力從晶背傳輸到晶圓正面,電子就不用經過那些在晶片正面且結構日益複雜的後段製程堆疊。

晶背供電技術:改變新一代邏輯晶片規則

晶背供電網路(BSPDN)的目標是減緩邏輯晶片正面在後段製程所面臨的壅塞問題,而且還能透過設計技術協同優化(DTCO),在標準單元實現更有效率的導線設計,進而協助縮小邏輯標準單元的尺寸。晶片系統也可望因此受惠,系統級(system level)逐漸受到功率密度增加和供應電壓猛降(IR壓降遽增)的影響。

由於晶背供電技術的導線能採用更大尺寸與更小電阻的設計,晶背供電網路據信能大幅降低晶片的IR壓降。這將方便設計人員把穩壓器與電晶體之間的功率損失控制在10%以下。利用晶圓接合技術,還有望實現像是邏輯與記憶體堆疊等3D系統單晶片的設計。

| 圖一 : 晶背供電網路的示意圖:它能把供電與訊號網路分離。 |

|

2019年,imec率先提出晶背供電技術的概念,並與矽智財公司Arm合作,量化其系統級優勢。同時,作為一套考量佈線環境的導線設計方案,晶背供電網路也納入了imec展望2奈米以下的技術節點藍圖。近期,一些晶片大廠宣布將在其新一代邏輯晶片的商業量產製程中導入晶背配電技術。

晶背供電網路的特定應用:奈米矽穿孔連通至埋入式電源軌

晶背供電網路帶給晶片製造一些全新的製程步驟及整合挑戰,包含像是基板極薄化、微米或奈米矽穿孔製程、晶圓背面與正面對準,以及晶背製程帶給前端製程主動元件的影響。這些整合流程和各自帶來的挑戰都在一篇E. Beyne等人受邀於2023年IEEE國際超大型積體電路技術研討會(VLSI Symposium)發表的論文中進行探討。

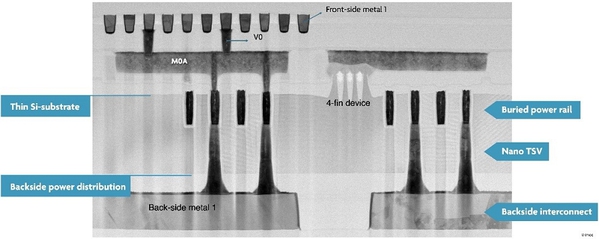

利用上述製程步驟,imec在2022年IEEE國際超大型積體電路技術研討會(VLSI Symposium)上以實驗展示了一種特定的晶背供電網路(BSPDN)設計,也就是搭配埋入式電源軌(BPR)的晶背供電技術。埋入式電源軌是一種深嵌在晶片前段製程的垂直導線,與標準單元平行。

利用這些電源軌,imec能把微縮化的FinFET元件連接到晶圓的正面與背面。電源經由深度為320奈米的奈米矽穿孔從晶背傳輸至間距僅200奈米的埋入式電源軌,還能毫不佔用標準單元的空間。晶背製程也並未損害到FinFET元件的前端性能。

| 圖二 : 此穿透式電子顯微鏡(TEM)圖顯示了微型FinFET測試元件與晶圓正面及背面相連(發表於2022年IEEE國際超大型積體電路技術研討會)。 |

|

區塊級評估:高密度或高性能應用?

上述研究聚焦的是晶背供電網路及標準單元級(standard cell level)的電晶體連接性,imec和Arm也已著手進行下一步:把研究範圍擴展到區塊級(block level),其代表著積體電路的更大單位,也是晶背供電網路能完全發揮其優勢的所在。針對晶背供電網路整合埋入式電源軌的設計,他們研究了其能否在區塊級提供比設於晶圓正面的供電網路(PDN)還要高的電源完整性。

藉由設計技術協同優化(DTCO)來進行區塊級評估能算出晶片上的IR壓降,亦即量化供電效能的主要指標。該數值還能顯示該供電網路對積體電路的影響程度,包含量化其在功耗、性能及尺寸(PPA)方面的影響。這項研究還能針對特定運作狀態,指出優化該供電網路的調整方法。

在高密度的邏輯運作狀態下,晶背供電網路設計已然勝過設於晶圓正面的供電網路設計。高密度邏輯元件的優化設計會盡可能做到最省電並縮小尺寸。這點在採用奈米片架構的元件上能透過奈米片寬度最小化來實現。但在高性能邏輯元件上,目前還未取得晶背供電網路所能帶來的性能升級數據。高性能邏輯元件鎖定的是快速開關和高驅動電流,通常採用較寬的奈米片元件和較大的臨界電壓。這類的邏輯元件對功率密度的要求也比高密度邏輯元件還更嚴格,因此,晶背供電網路所能帶來的效益預計更具影響力。

整合晶背供電網路和埋入式電源軌 實現高性能邏輯晶片的區塊級升級

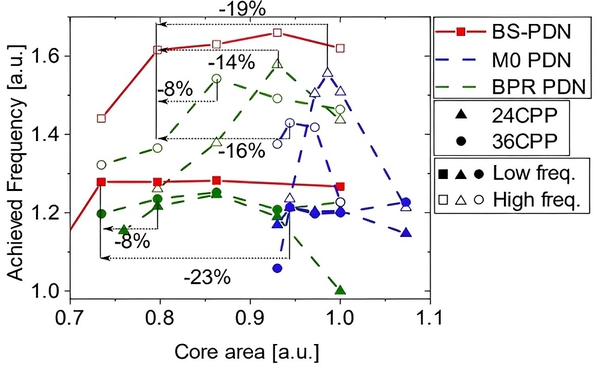

在一篇於2023年IEEE國際超大型積體電路技術研討會(VLSI Symposium)發表的論文中,imec和Arm利用一款Arm推出的64位元高性能處理器來評估(晶背)供電網路所帶來的影響。該評估鎖定了三種不同的供電網路設計:傳統的晶圓正面供電(M0 PDN)、晶圓正面供電搭配埋入式電源軌(BPR PDN),以及晶背供電網路搭配連接到埋入式電源軌的奈米矽穿孔(BSPDN)。

為了確保能實現高性能運算區塊的現實應用,還開發了高性能版本的imec 14埃米(A14)奈米片製程設計套件(PDK)。我們也套用了一款內部研發的分析模型,並結合了實體設計框架,以評估區塊級的功耗、性能及尺寸並驗證IR壓降。

與晶圓正面供電網路相比,該晶背供電網路能在不影響能耗的情況下使其頻率提高6%和尺寸縮小16%。與晶圓正面供電網路搭配埋入式電源軌的設計相比,則是頻率提升2%、尺寸縮小8%和能耗降低2%。

| 圖三 : 比較晶背供電網路及兩種晶圓正面供電網路(設於M0金屬層的供電網路、搭配埋入式電源軌的供電網路)在寬閘極間距(36CPP)及窄閘極間距(24CPP)、低頻及高頻運作狀態下的核心電路面積。在性能開始下降前,晶背供電網路的核心電路面積能夠縮小(發表於2023年IEEE國際超大型積體電路技術研討會)。 |

|

研究人員為評估IR壓降設立了功率損失的最大容許值,即35mV,相當於10%的額定供應電壓(VDD + VSS)。在應用晶背供電網路時,該IR壓降值在奈米矽穿孔的間距為4~6μm時實現,這也代表電源「接通」時的間距。不過在另外兩種晶圓正面的供電網路上,只有極窄間距(或CPP)才能把IR壓降控制在這個目標範圍內,導致處理器的性能下降。

針對晶背供電網路,imec團隊也研究了進一步改良其電源完整性的方法,例如透過改變奈米矽穿孔的材料。以釕(Ru)取代鎢(W)來製造奈米矽穿孔能降低其電阻,進而改善IR壓降,將其減少23%。

簡言之,在高效能運算應用上,晶背供電網路能充分發揮其潛力,提升區塊級功耗、性能和尺寸並降低IR壓降。

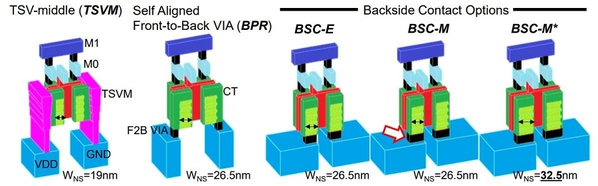

| 圖四 : 各種連接方案的模擬結構圖:中段製程矽穿孔封裝(TSVM)及三種晶背直接供電方案(發表於2023年IEEE國際超大型積體電路技術研討會)。藍色為電源及參考電壓(VDD + VSS);淺藍色為中段製程的M0金屬層;深藍色為後段製程的M1金屬層;黑色為通孔;紅色為閘極;淺綠色為(主動式)奈米片及介電隔離層;深綠色為接觸金屬(CT)。 |

|

擴充標準單元級的晶背供電方案

目前為止,我們探討的晶背供電網路只有一種,那就是利用與埋入式電源軌相接的奈米矽穿孔把電源從晶圓背面連接到晶圓正面。一條小通孔從埋入式電源軌連接到中段製程(M0A)導線的底部,以連接標準單元級的電晶體。

除了這種埋入式電源軌設計,研究人員也在探索其它能在標準單元實現晶背供電的導線設計方案。imec在2023年IEEE國際超大型積體電路技術研討會(VLSI Symposium)上討論另外兩種奈米片電晶體的連接方案。選在中段製程進行矽穿孔封裝(TSV-middle;TSVM)時,一條長型通孔能在無需埋入式電源軌的情況下,把晶背的M1金屬層連接到M0A金屬層的那面。

第二種更先進的做法是由一條通孔直接把奈米片源極和汲極的磊晶底部連接到晶背的M1金屬層。這種晶背直接供電(direct backside connectivity;BSC)的連接方案有三種不同類型,主要差別在於接點的面積大小。磊晶型晶背直接供電(epi BSC;BSC-E)的通孔直接連接到源極和汲極磊晶的底部,而接觸金屬型晶背直接供電(BSC-M)的通孔則與接觸金屬(metal contact)相連。第三種是加寬版接觸金屬型晶背直接供電(BSC-M*),為BSC-M的延伸版本,除了縮小閘極的蝕刻範圍,還要增加奈米片(作為主動元件)的寬度(WNS)。

不同的連接方案具備不同的特性,例如奈米片寬度,分別對電性及標準單元的微縮潛能產生不同的影響。一般來說,從採用中段製程矽穿孔封裝到埋入式電源軌,再到晶背直接供電,元件會越來越緊湊,整合難度也會更高。但我們也預期隨著邏輯元件的微縮化,雖然整合複雜度會增加,但在功耗、性能及尺寸方面將能獲得更多優勢。

實現晶背直接供電

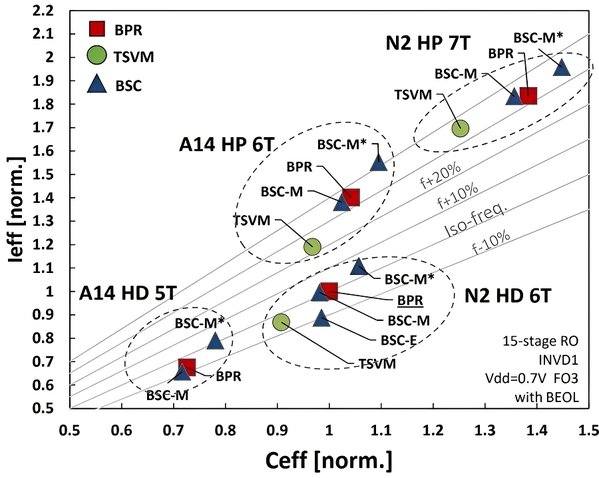

在2023年IEEE國際超大型積體電路技術研討會(VLSI Symposium)上,imec鎖定採用2奈米及1.4奈米(即14埃米)奈米片技術的高密度(2奈米6軌和1.4奈米5軌)和高性能(2奈米7軌和1.4奈米6軌)邏輯晶片設計,針對不同的晶背供電方案提供了各自在功耗、性能、尺寸和微縮潛能方面的數據[4]。先前用來評估性能的主要指標是環型振盪器的模擬頻率,以有效驅動電流和有效電容的比值(Ieff/Ceff)來表示。

在2奈米的高性能邏輯晶片上,採用最多軌設計的7軌標準單元,不論採用哪種連接方案,工作頻率都幾乎相同。但當微縮到1.4奈米時,中段製程矽穿孔封裝方案仍能採用於6軌設計,不過與埋入式電源軌方案相比,速度減慢了8.5%。整體來說,加寬版接觸金屬型晶背直接供電方案顯然勝過其它的連接方案,例如速度比埋入式電源軌還快了5%。

至於2奈米的高密度邏輯晶片,其軌道高度比高性能邏輯晶片還要小(6軌),所以採用不同連接方案的運作頻率差異會更大。當微縮到1.4奈米5軌設計時,中段製程矽穿孔封裝不再適用,只能考慮埋入式電源軌和晶背直接供電這兩種方案。在這種情況下,埋入式電源軌和加寬版接觸金屬型晶背直接供電方案之間的奈米片寬度差異所帶來的影響更大,而後者顯然是贏家,速度比埋入式電源軌快上8.9%。

| 圖五 : 在高性能邏輯晶片(2奈米7軌、1.4奈米6軌)和高密度邏輯晶片(2奈米6軌、1.4奈米5軌)上採用不同的連接方案,模擬其環型振盪器頻率的結果。 |

|

總而言之,雖然中段製程矽穿孔封裝方案更佔空間,但對於較大的標準單元設計(例如2奈米7軌的邏輯晶片)來說還是不錯的選擇。然而,就尺寸和能耗的微縮潛能來說,埋入式電源軌和晶背直接供電方案更具潛力。在較少軌道的標準單元設計上,加寬版接觸金屬型晶背直接供電方案因為具備更大的奈米片寬度和接點面積,所以明顯勝過其它方案。但是這套方案除了具備性能優勢,還要考量整合方面的技術挑戰也會更大。

imec團隊目前在努力進行不同晶背連接方案的技術展示,也與Arm合作評估區塊級的功耗、性能及尺寸。

未來展望

矽晶圓的背面經久未用,而供電會是其首開的應用實例。與此同時,imec攜手其業界夥伴共同探索其它能移到晶背運作的元件功能。例如,全域導線和時脈訊號分配。供電網路是一種特別針對電阻最小化進行優化的導線,但時脈分配或其它類型的訊號具備不同的特性,所以晶背的其它應用將會探討不同的面向。imec正在研究功能性晶背(functional backside),或稱為晶背2.0(backside 2.0),可能要面臨哪些挑戰,又能帶來哪些契機。(本文作者Julien Ryckaert為imec邏輯晶片技術研發副經理;編譯/吳雅婷)