有些家電全年無休 24 小時運作,對於效率的要求極高,因此使用 MOSFET 的效果會比 IGBT 更理想。但是,運用超接面原理的現代化 MOSFET 技術,卻難以控制各種馬達驅動器應用。本文說明閘極驅動器電路有效設計的基本考量,以及結合運用 EiceDRIVER IC 及 CoolMOS CFD2 所帶來的效益。

BLDC 驅動器的整流電池分析

圖 1 所示的半橋式電池,可供研究所有 FET 的切換行為。S1 及 S2在降壓組態切換,S4則永久開啟提供回路電流路徑。S1為主動式開關。電感器電流在S1開啟時上升。S2為整流器開關,其本體二極體在S1關閉時輸送電感器電流,且電感器電流下降。這種運作模式在 1/3 的馬達週期之中產生,然後相同的運作流程會移往下一個半橋。MOSFET 的切換模式運作會造成高 dv/dt 及 di/dt。

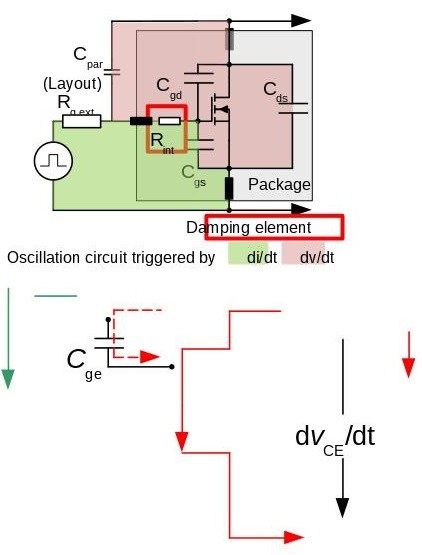

| 圖2 : MOSFET、封裝、配置及驅動器的寄生元件 |

|

高 dv/dt 的主要風險在於擊穿。S1開啟並在S2產生 dv/dt,與其閘極耦合且出現電壓突波。如果耦合突波夠高,足以達到 FET 的閘極閾值電壓,則橋接的兩個 FET 都會短暫開啟,導致分流電阻器或電解電容器等元件故障。

另一項風險在於,開啟時可能引發閘極振盪。高 di/dt 會在 FET 封裝及配置的源極電感造成壓降。這種電壓會形成負回饋至驅動電壓,造成 FET 閘極諧振(如圖3所示)。

此外,高 dv/dt 關閉時,可能透過汲極閘極電容耦合至閘極,而造成振盪。以上疑慮與 FET 參數、封裝及配置寄生有關,如圖2所示。這些問題必須透過閘極驅動器設計加以解決。

dv/dt 來源及應用效應

dv/dt 在逆向電容Crss的充電期間產生(如圖 2 所示的電荷 Qgd)。因此,Crss值及充電電流位準是影響dv/dt的兩項因素。閘極電阻Rg值較高,表示是以較低電流為Crss 充電 (會延長米勒平坦區時間,並降低 dv/dt)。

MOSFET本體二極體逆復原期間的電流變化率dIrec/dt會在寄生源極電感產生電壓,也就是送往驅動電壓的正回饋。這樣會加快Crss 的充電速度,並提高 dv/dt。具備階躍復原行為的二極體,會產生較高的dv/dt。此外,上述躍階性質會在S2增加電壓過衝現象,而這是由迴路電感所造成。

在關閉期間,超接面 FET(例如 CoolMOS CFD2)的非線性電容 Coss 和高電壓 Vds 下的低 Coss 值會提高 dv/dt。如此可降低切換損耗並加快電壓轉移,不過考量到 dv/dt 較高的情形,也需要謹慎的配置和適當的閘極驅動器設計技巧。

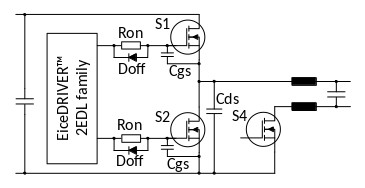

CoolMOS CFD2 的閘極電路設計提案

圖 4 為 CoolMOS IPD65R420CFD 使用提案示意圖。主要是在各個橋接開關節點新增電容器 Cds=0.47nF,藉以限制並線性化 dv/dt。這是預防擊穿及諧振問題最可靠的方法。在馬達驅動器應用中,切換頻率多半偏低,因此新增的電容器 Cds 只會對切換損耗造成些微影響。選擇其他驅動參數的考量如下:

- Ron=1000 ? 減緩開啟速度、延長平坦區,減少 dv/dt。

- Roff=0 ? 關閉時降低對 GND 的阻抗,減少電壓耦合突波。

- Cgs=0.47nF 降低 Crss/Ciss 比率、減少汲極閘極或米勒耦合增益。

- Cds=0.47nF 在開啟時控制/線性化 dv/dt,優點在於可移除閘極振盪與減少 EMI。

| 圖4 : CoolMOS CFD2(採用 EiceDRIVER 2EDL 系列)的閘極電路示意圖 |

|

電路由 2EDL05N06PF EiceDRIVER IC 運作。此系統採用英飛凌SOI 技術,提供卓越的耐用度,可有效承受負瞬時電壓 [3]。整合靴帶式二極體的優異屬性,可滿足高功率密度和成本效益比的需求。

配置建議

圖 5 顯示了雜散電感最小化的配置,其高側源極端子與低側汲極端子之間的距離較短。相對於頂層的高側電晶體,底層的低側電晶體偏移至左側,導致兩個電晶體熱解耦。此外,低側電晶體甚至更靠近相應的閘極電阻。

這項偏移也讓低側電晶體的汲極端子直接移到源極端子下方,使適當數量的通路就近連接至高側源極端子,進而將迴路電感最小化。將低側電晶體適當置於頂層,可避免雙側組裝,不過必然會增加整體區域。

一般來說,若要在閘極驅動迴路降低雜訊和諧振,建議使用以下配置準則:

- 讓閘極驅動器盡可能靠近閘極。

- 將閘極到汲極的外部電容減到最小。

- 適當地選擇閘極電阻 Rg.以減緩 dv/dt。

- 隔離電源接地與閘極驅動器接地。

- Rg 盡可能靠近閘極腳位。

- 在閘極驅動器與閘極之間使用較厚走線。

閘極端子鄰近閘極電阻的配置方式,加上較低的雜散電感,可提升 CoolMOS 電晶體的效能,實現出色的切換行為。圖 6 顯示驅動電路設計提案的開啟波形。圖中可見沒有振盪的乾淨閘極訊號,而汲極-源極電壓也在米勒平坦區期間緩慢降低至 0V。

![圖6 : 開啟波形:直流連結電壓 VDC = 320 V 及負載電流 IL = 2.5 A. VDS(紅色,50 V/div)、IL(綠色,1 A/div)、VGS(藍色,10 V/div)、PWM(黃色,5 V/div)、時間尺度 1 μs/div]](/art/2018/10/251000196300/p6S.JPG)

| 圖6 : 開啟波形:直流連結電壓 VDC = 320 V 及負載電流 IL = 2.5 A. VDS(紅色,50 V/div)、IL(綠色,1 A/div)、VGS(藍色,10 V/div)、PWM(黃色,5 V/div)、時間尺度 1 μs/div] |

|

假設配置及驅動電路不變,可預期其他兩種切換橋接出現相同行為。

結論

CoolMOS CFD2 可有效提升馬達驅動應用的效率。採用EiceDRIVER 2EDL系列的閘極驅動器電路提案,可確保切換不會產生振盪。由此可見,CoolMOS CFD2在驅動器系統中能夠有效、可靠的運作。此外,2EDL系列採用英飛凌SOI技術,可為馬達驅動器應用提供 dv/dt 方面的高耐用度以及絕佳的 CoolMOS CFD2控制能力。

(本文作者Wolfgang Frank任職於英飛凌科技)

參考文獻

[1] R. Mente, F. Di Domenico, M.A. Kutschak, A. Steiner: CoolMOS? CFD2 first 650 V rated super junction mosfet with fast body diode suitable for resonant topologies, Application Note, Infineon Technologies, February 2011.

[2] W. Choi, D. Son, M. Hallenberger S. Young: Driving and Layout Requirements for Fast Switching MOSFETs, Fairchild Semiconductor Power Seminar 2010-2011, Fairchild, 2011.

[3] J. Song, W. Frank: Robustness of level shifter gate driver ICs concerning negative gate voltages; Proceedings of PCIM 2015, Nuremberg, Germany, 2015.