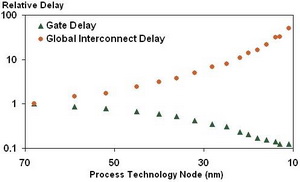

為了使積體電路元件的性能跟上摩斯定律(Moore’s Law),積體電路設計人員在驅策技術節點縮小化時必需減緩RC遲滯效應。為達到元件縮小所帶來的應有的積效進而增加45奈米以下導線間的空間縮小所帶來的挑戰。在過去幾年裡,研究人員研究了替代材料和更複雜的整體整合方法以解決RC遲滯問題。雖然在研究環境中看到了成效,但大多數這些材料和整合技術最終還是面臨轉移到量產時之程序控制和生產成本的挑戰。

|

| 剖面測試架構中顯示了諾發系統的介電薄膜和其特有薄膜介面 |

諾發系統最近已開發出一套突破性技術來導入介電薄膜沉積和其薄膜介面控制製程,它提供需無複雜的重大變化來降低百分之五的有效介電常數(keffective)價值超過各種途徑。圖中的剖面測試架構中顯示了諾發系統的介電薄膜和其特有薄膜介面。

這些在薄膜沉積的創新方法就是利用諾發的PECVD系統,VECTOR的多站連續沉積架構來實現。開發小組對影響薄膜沉積堆疊及其薄膜介面控制參數實施最佳化的調整,使諾發系統的客戶在面對未來新技術節點需求條件下還能夠繼續延用。

諾發PECVD事業群的技術總長Mandyam Sriram 說明,RC遲滯效應所重視的是有效的介電常數值(keffective),而不是每一薄膜層的絕對K值。現今業界中最快和最先進的積體電路元件就是使用諾發的介電薄膜還製造。進而證明我們可為我們的客戶提供簡單化的製程整合流程及同時擁有低成本及量產就緒的解決方案。