Altera推出了Quartus II版本6.1软件,帮助设计人员实现优异的性能和效能。该版本对PowerPlay功率消耗优化工具进行了改进,与Altera Stratix III FPGA的可编程功率消耗技术相结合,总功率消耗比Stratix II FPGA降低了50%。与竞争65nm组件相比,Quartus II版本6.1软件在Stratix III FPGA上性能平均快出一个速率等级,编译时间平均缩短55%(请参考相关的Stratix III FPGA发布www.altera.com/stratix3release)。

|

| Quartus II版本6.1软件在65nm FPGA上实现了优异的性能和效能 |

Altera FPGA产品资深产品营销总监David Greenfield表示:「在65nm上,优化功率消耗、性能和效能十分关键,它们在使设计软件实现令人满意设计上的作用越来越重要。Quartus II版本6.1软件和Stratix III FPGA在设计和开发上进行了细致地协调,因此,客户完全可以充满信心地开始下一代系统设计。」

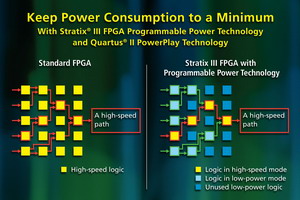

这一版本的PowerPlay功率消耗优化工具与Stratix III芯片的可编程功率消耗技术紧密结合,这种独特的创新帮助设计人员获得非常好的性能,从根本上降低了功率消耗──都是自动同时完成。对于Stratix III FPGA设计,PowerPlay工具在编译时自动分析客户的设计,确定性能最关键的路径,然后,将相应的模块设置为高性能模式,而其他逻辑则设置为低功率消耗模式。

由于Altera的核心布局布线技术取得了实质性进步,与竞争65nm FPGA及其设计软件相比,Quartus II版本6.1软件和Stratix III FPGA组合在设计性能和编译速度上具有明显的效能优势。使用Altera性能基准检验方法(请参考白皮书www.altera.com/literature/wp/wpfpgapbm.pdf),Quartus II版本6.1软件和Stratix III FPGA性能平均快出一个速率等级;使用最大努力对比方法时,最多快出三个速率等级;使用时序约束对比方法时,编译时间平均缩短55%,最大达到80%。而且,在所有这些基准检验中,Quartus II软件所需要的计算机内存要少50%。

TimeQuest时序分析器首次在Quartus II版本6.0软件中导入,是由FPGA供货商提供的第一款也是唯一一款时序分析器,为Synopsys设计约束(SDC)时序格式提供全面直接性的支持,该格式是高级和高密度设计成熟的业界标准。设计人员使用TimeQuest工具可以建立、管理和分析SDC时序约束,迅速达到时序逼进。这一ASIC功能时序分析器在版本6.1中进行了改进,为Stratix III FPGA提供更精确的模型,实现更高的性能。新的SDC编辑器缩短了编译时间,简化了约束建立,数据表发生器和SDC格式扩展支持进一步简化了电路板级设计。

Quartus II版本6.1软件对Altera新的Stratix III组件以及其他CPLD、FPGA和结构化ASIC系列提供软件支持。其性能和效能改进的其他特色包括:

• 多处理器支持:支持多处理器计算机在编译时进行平行处理,从而缩短了编译时间。Quartus II软件首次实现了由FPGA供货商提供的多处理器支持,发挥了新的多重核心处理器的优势。

• 分离窗口支持:Quartus II软件GUI用户可以在桌面上独立移动各个工具窗口,方便了设计分析和管理。

• 芯片规划器:新的整合平面规划器和芯片编辑器进行详细地设计平面分析和工程更改顺序(ECO)编辑。

• 高级I/O时序:支持设计人员在Quartus II软件中输入电路板布线参数,实现更精确的I/O分析,更迅速地达到时序逼进。

• 接脚规划改进:从接脚规划器结果中自动建立顶层设计档,实现更彻底的I/O分析,加速实现电路板设计。

• Windows 64位版本:Quartus II软件64位版本运行在Microsoft Windows XP Professional x64上,设计人员可以充分利用计算机的4Gbytes内存优势。

• 扩展Linux支持:除了Red Hat Enterprise Linux外,Quartus II软件还支持SUSE Linux Enterprise 9。