即使三星電子最近被採用Exynos系列處理器之行動裝置產品疑似存在著安全漏洞問題搞的烏煙瘴氣,但在邁向14奈米製程技術之路一樣沒有任何懈怠。繼格羅方德半導體以及英特爾後,三星也向外界宣布採用14奈米製程技術之行動晶片測試成功,該行動晶片不管是針對動態功耗以及漏電率方面皆有明顯改善。

|

| 三星宣布採用14奈米製程技術之行動晶片測試成功 |

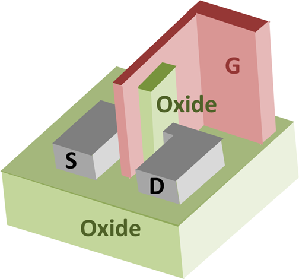

三星提到目前14奈米FinFET比起32/28奈米的高介電常數金屬閘極(HKGD)製程,已經大幅改善先前SoC晶片之漏電率以及動態功耗的問題。也代表三星極有可能會在往後推出的行動處理器中採用ARM big.LITTLE處理技術和14奈米製程技術,相信可以預見效能更強大的行動處理器將會縮短問世時間。而三星也協同其他夥伴(Synopsy、ARM、Cadence、Mentor)進行多種晶片測試之Tape Out。

14nm Cortex-A7處理器的順利Tape Out也代表三星在14奈米製程技術的重大突破。三星同時發佈製程技術之產品開發套件,讓其他客戶能夠針對14奈米FinFET測試晶片進行模型設計以及其他產品設計之用。除此之外三星更與ARM共同簽訂有關14奈米製程技術與IP庫的合作協議,並成功研發了14奈米技術的測試處理器晶片。更與其他的合作夥伴一起完成了ARM Cortex-A7處理器、ARM big.LITTLE設置以及SRAM晶片的研發測試工作。

還記得三星於今年年中才斥資19億美元來建立一條新的邏輯晶片生產線,新生產線將採用300mm晶圓、20/14奈米製程技術,加大邏輯晶片的產量,以滿足智慧型手機和平板電腦行動處理器日漸增長的大量需求。以及表示會在近期之內將會開發出內建big.Little省電配置的Exynos處理器,雖然還必須等到2014年才能達到可用的水準,但相信未來行動處理器的效能很快就能跟上PC處理器的腳步。