台積電終於在今年第一季的法人說明會裡,透露了其3奈米將採取的技術架構,而出乎大家意料的,他們將繼續採取目前的「FinFET」電晶體技術。而這代表了台積電的製程微縮能力遠超乎市場想像,3奈米仍不是其極限所在。

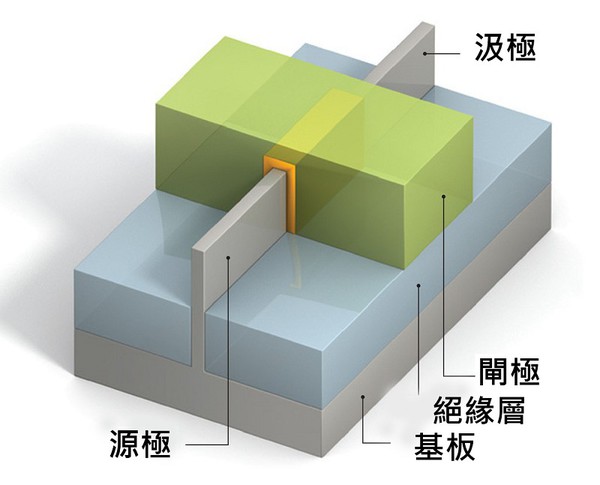

當製程下探,電路無可避免的會遭遇到控制的困難,產生如漏電、電壓不穩定等的短通道效應(Short-channel Effects)。而為了有效抑制短通道效應,盡可能的增加電路的面積,提高電子流動的穩定性,就是半導體製造業者重要的考量,而鰭式電晶體(FinFET)架構就因此而生。

FinFET運用立體的結構,增加了電路閘極的接觸面積,進而讓電路更加穩定,同時也達成了半導體製程持續微縮的目標。但這個立體結構的微縮也非無極限,一但走到了更低的製程之後,必定要轉採其他的技術,否則摩爾定律就會就此打住。

也因此,三星電子(Samsung)在2019年就宣布,將在3奈米製程世代,改採閘極全環(Gate-All-Around,GAA)的技術,作為他們FinFET之後的接班製程;無獨有偶,目前的半導體龍頭英特爾(Intel),也在不久前宣布,將投入GAA技術的開發,並預計在2023年推出採用GAA製程技術的5奈米晶片。

| 圖一 : 台積電總經理魏哲家表示,3奈米將延續FinFET技術。(CTIMES資料照) |

|

由於世界前兩大的半導體廠都相繼宣布投入GAA的懷抱,因此更讓人篤定,也許3奈米將會是GAA的時代了,因為至3奈米製程,FinFET電晶體就可能面臨瓶頸,必須被迫進入下個世代。

續用FinFET架構 帶來雙贏局面

但唯獨台積電,仍將在3奈米世代延續FinFET電晶體的技術。

而就如同所有的業者,台積電的選擇考量也是商業決策下的結果。而他們能做下這個決定,多少也意味著他們確認了3奈米並非FinFET技術的瓶頸,甚至還非常有自信能夠在相同的FinFET技術下,在3奈米製程裡取得水準以上的良率。這也代表著台積電的微縮技術遠超過其他的晶片製造商。

所以台積電將會在相同的製程技術與製造流程下,進入3奈米世代,也因此他們不用變動太多的生產工具,也能有較具優勢的成本結構。而對客戶來說,也將不用有太多的設計變更,也有助於客戶降低生產的成本。若最終的產品性能還能與競爭對手平起平坐,那台積電可能又將在3奈米產品世代再勝一籌。

尤其是對客戶來說,在先進製程的開發裡變更設計,無論是改變設計工具或者是驗證和測試的流程,都會是龐大的成本,時間和金錢都是。因此若能維持當前的設計體系,對台積電和客戶來說,都會是個雙贏局面。

晶片效能決定市場價值 FinFET還能走多遠?

剩下的問題,就是誰的效能表現比較好,而這個答案只有在2022年3奈米晶片量產之後才會知道。由於最先進製程的產品,都是運用在最高階的產品上,這些產品的價格高,因此成本相對較不明顯,一旦效能優勢無法凸顯,就會失去消費者的支持,進而失去訂單。

過往的三星電子就數次面臨此一局面。儘管他們的價格較低,但是產品的效能始終無法超越台積電,因此一流的大廠都轉往台積電投單,讓他們在高階晶圓代工的市場上頻頻失利。

因此進入3奈米世代後,若三星的GAA製程在效能上可以勝過台積的FinFET,即使價格較高,都可能反轉當前的先進晶片代工的市場局面。

| 圖二 : FinFET技術的片狀結構成功延續了摩爾定律,但還能走多遠?。 |

|

另外一個問題,就是FinFET技術還能延續多久?如果3奈米不是瓶頸,那會是哪裡?

所幸,目前的可能的答案也只剩下兩個,如果不是2奈米,就是1奈米。但無論是哪一個,都要很多年以後才會知道。但我們可從過去台積電的發言來看,他們對於微縮技術相當有信心,認為做到1奈米也不是問題,0.1奈米都可以挑戰看看。

再對照他們在3奈米世代所採取的策略,我們更可以大膽預測,也許要走到1奈米世代,才能摸清楚台積電的能耐,但那已經是一個完全無法想像的超級先進晶片製造技術。

新架構接連問世 布局2奈米製程

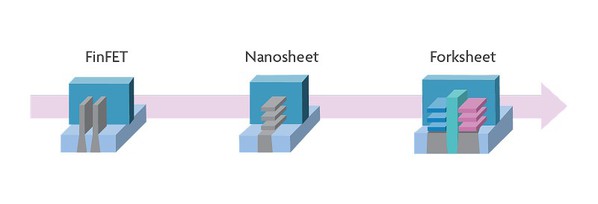

然而,FinFET製程終究會步入它的物理極限,接班技術的布局也應該要開始策動,而目前看起來,採用加大閘極電路面積的GAA技術會是最可能選項,其中Nanosheet FET又會是最適合的製程,目前三星也是採用此一結構,作為其3奈米世代的核心技術。

當然Nanosheet FET也不是唯一的選項,目前仍有許多的研究機構針對3奈米之後的晶片製程技術進行研究。例如愛美科(imec)日前也宣佈了一個名為「Forksheet FET」的技術,用以在2奈米的晶片製造。

依據愛美科的資料,在「Forksheet FET」結構中,nFET和pFET被整合在同一個結構中,其中有一個介電牆把nFET和pFET分開。它也跟目前的GAA製程完全不同,也將使用不同的裝置來生產nFETs和pFETs。這個技術的優勢就在於它有更緊密的n到p的間距,並減少面積縮放。與Nanosheet FET相比,在相同的製程下,Forksheet FET的電路更加緊湊(42nm vs 45nm)。

| 圖三 : 與Nanosheet FET相比,在相同的製程下,Forksheet FET的電路更加緊湊。(Source:imec) |

|

除此之外,愛美科也在研發一種稱為CFET(Complementary FETs)的技術,它是另外一種GAA的架構,為針對2奈米以下製程所開發。該技術由兩個分開的Nanowire FET所組成(n型和p型),是一種把p型奈米線疊在n型奈米線上的結構。

透過這種疊加的形式,CFET等於是實現了一種「折疊(folding)」的概念,藉此消除了n到p分開的瓶頸,同時也減少了運作單元活動區域(cell active area)面積達到2倍之多。

目前這些仍在研發中的技術都有更自的挑戰待突破,包含散熱的控制和製造成本等,但可以確定的就是,對於2奈米之後的晶片製造,現在已有數項技術正在進行中,同時也不會是遙不可及。

結語

從現在分歧的製程技術採用決策來看,顯然半導體製造商在3奈米之後的晶片製造,已經面臨了需要轉進新架構的挑戰,而且目前仍未有主宰的技術出現。

當此之時,除了製造商需要各顯本事之外,如何從技術與成本中取得最大的利基,將是競爭的關鍵所在。特別是先進半導體製造的成本十分高昂,若不能在生產技術與製造成本中取得較佳的平衡,未來的發展也將會非常艱辛,再加上半導體的製造供應鏈牽連體大,不僅是製造設備,也包含設計工具和檢驗測試的部分,若不能有一致性的解決方案,想要一枝獨秀也將是非常困難。