百倍變焦、億萬畫素,還可拍攝8K的影片,而且幾乎克服了夜間低光源的拍攝困難。CMOS影像感測器究竟如何把智慧手機變成單眼相機?

智慧手機的相機功能可以有多強?三星電子(Samsung)近期發表的最新旗艦型5G手機,樹立了一個新典範。該款新手機的拍攝畫素來到了1億800萬的等級,可拍攝8K的影片,而且最大的變焦數來到了史無前例的100倍,更驚人的是,幾乎克服了夜間低光源的拍攝困難,實現了隨時、隨地、隨身的高品質攝影的可能。

達成這個目標背後的功臣,就是先進的CMOS影像感測器技術,而三星所使用的,是一個名為「ISOCELL」的影像感測器系統。該產品是三星自行研發的CMOS影像感測技術,目前最新的一代為「ISOCELL Bright HM1」。

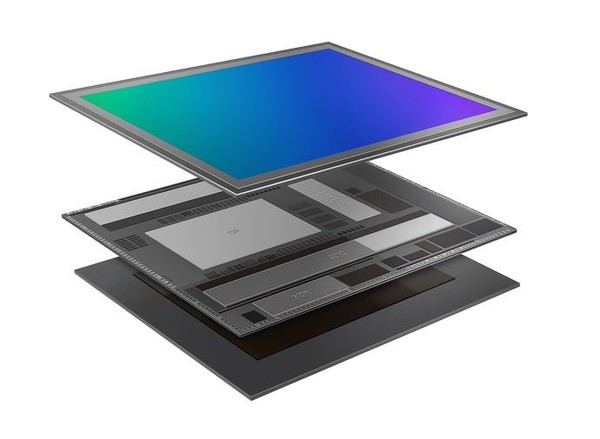

在2018年初,三星宣布了新一代的ISOCELL(Fast 2L3版本)技術更新,而這次的更新是一個重大的升級,因為三星正式將3層堆疊架構運用在CMOS影像感測器上。

異質整合 CMOS進入感測+邏輯+DRAM時代

在此之前,一般的CMOS感測器是採兩層的結構,也就是把產生光感訊號的畫素陣列(pixel array)感測器,以及進行電子與數位訊號轉換的邏輯運算器進行堆疊,藉此加快運算的速度,並減少DRAM的使用。

| 圖一 : 三星把DRAM整合至影像感測器之中,完成了一種三層的架構。(source:三星) |

|

這種雙層的結構對於實際的影像拍攝來了諸多的好處,最明顯的就是實現了超高的畫素(image readouts)讀取性能,並讓電子快門的即時取景,與順暢的超級慢動作成為可能。

站在這個基礎上,三星進一步把DRAM整合至感測器的結構之中。他們把2GB的LPDDR4 DRAM置於邏輯層之下,完成了一種三層的架構,並帶來了超高速的的影像拍攝性能。

由於整合了2GB的DRAM,感測器可以在把數據傳送到處理器之前,暫時儲存大量的影像資訊,所產生的結果就是超高速的電子影像快門,以及清晰無比的錄影功能,對於拍攝者而言,就是更強大的照相能力,以及超高解析的影片拍攝。最明顯的改進,就是消除了過去CMOS感測器的照片變形與所謂的果凍現象(Rolling shutter)。

另一方面,高速快門與瞬時儲存多重畫幀(multiple frames)的性能,就能支援3D降噪(Noise Reduction)以及更高階的高動態範圍成像(HDR)。而這對經常需要在室內拍攝的手機來說,是非常重要的提升。

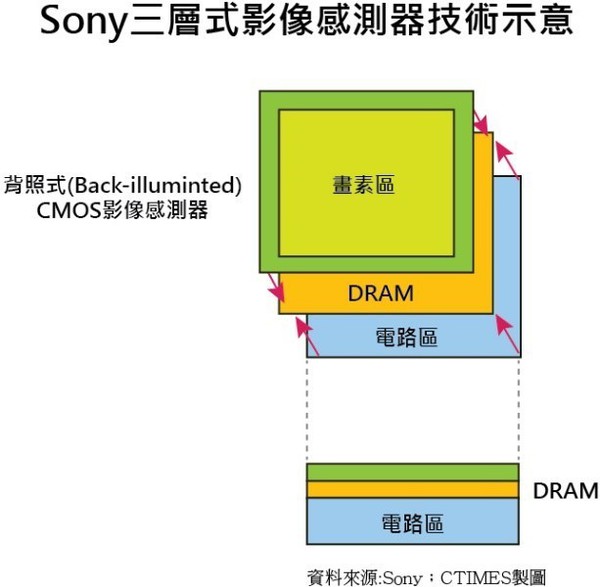

事實上,三星並不是第一個使用三層式堆疊技術的業者,早在2017年,Sony就發表了三層式的堆疊CMOS影像感測器技術。但是不同於三星,Sony的DRAM層是為在中間,畫素感測在前,邏輯電路則是在後。此設計同樣達成了高畫素與更快的影像幀數,讓智慧手機的拍攝有了全新的思考。

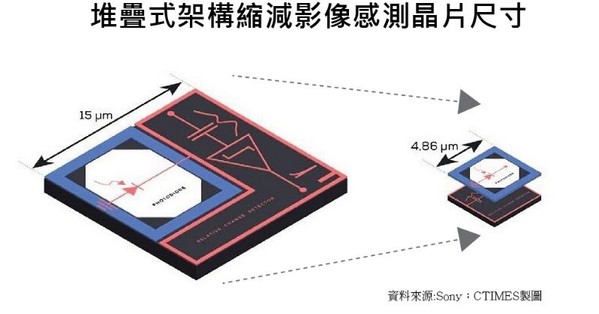

近期,Sony則是進一步把堆疊式CMOS影像感測器技術拓展至工業領域上。他們與Prophesee合作開發的新一代事件導向(Event-based)CMOS視覺感測器,就是把光學畫素陣列感測器堆疊在邏輯處理器之上,並以銅墊(copper pads)連接的方式取代過去採TSV的作法。透過這個堆疊的架構,Sony實現了業界最小的畫素尺寸(1 4.86μm),和最高的HDR的性能(1 124dB)。

| 圖二 : Sony的DRAM層是為在中間,畫素感測在前,邏輯電路則是在後。 |

|

一直以來,Prophesee的事件導向影像感測技術,就是以高光學資料讀取量與快速的畫素反應著稱,再與Sony高敏感與低雜訊的CMOS影像感測器結合,兩者合一,則是產生了兼具速度與質量的影像感測產品。而採用堆疊的結構,則又更進一步縮減了晶片的面積,這對於物聯時代寸土寸金的產品體積來說,十分有經濟效益,尤其是機器視覺與安全監控等應用。

| 圖三 : 採用堆疊的結構,則又更進一步縮減了晶片的面積。 |

|

先進軟體演算贊力 畫素與解析力倍增

而儘管堆疊的架構能為影像資料的運算與晶片體積帶來突破,但影像本身的質量則是完全取決於感測技術對光感的畫素反應,要有更細緻與更大量的畫素,就要在畫素層的技術著手,讓光感反應更敏感,同時畫素資料更細緻。

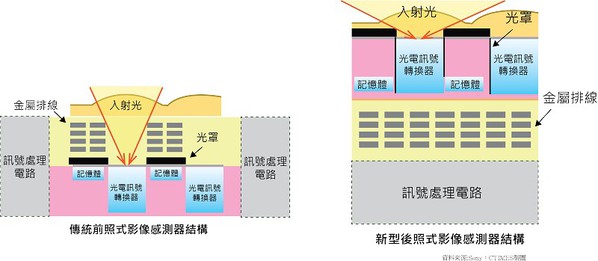

以Sony為例,就是採用背照式(Back-illuminated)的影像感測結構,再搭配自主研發的專屬畫素結構(proprietary pixel structure)技術,達成了優越的敏感度,同時也改善了過去畫素微小化的缺陷。

| 圖四 : 背照式(Back-illuminated)的影像感測結構。 |

|

透過這個技術,Sony把畫素微縮至2.74 μm,並維持了元件的敏感度以及色彩飽和度,也由於採用後照式的形式,感測器得以針對更廣的區域進行偵測與量測,這意味著能夠產生更多更精細的訊號,所以整體的解析度也較前照式架構增加了1.7倍。

至於三星則是運用獨家的畫素模擬技術「Teracell」,來突破實體感測畫素無法增加的困境,他們透過特殊的演算法,讓畫素以四個為一組的形式安排在影像感測器的彩色濾光片。

當處於低光源的拍攝時,演算法就會把四個畫素模擬成一個,讓畫素變大;反之,在明亮的環境時,則使用稱之為「再馬賽克(re-mosaic)」演算法,把原本的畫素再分割成四格,藉此產生更高解析度的照片。這個技術不僅改善了明暗成像的性能,同時也增加了HDR在高對比環境中的拍照能力,等於全面提升了手機的拍攝能力。

而三星最新一代的ISOCELL Bright HM1,則是更進一步採用了新的「Nonacell」技術,它其實是Teracell的升級版。不同於前代使用四畫素(2 x 2)一組的結構,新的Nonacell則是使用9畫素(3 x 3)一組的結構,把拍攝畫素一舉推升到了1億800萬的等級,同時新的感測器的畫素尺寸則是縮小至0.8μm,意味著能夠對光感測訊號有更細緻的敏感度,在明暗兩端的拍攝也更加突出。

結語

就系統設計的觀點,CMOS影像感測器本身的體積只能有減無增,並不允許其占用過多的裝置空間。而在這個前提下,想要達成更佳的拍攝品質,就只能從製程與設計結構來改善。

但若從應用的角度切入,則拍照與攝影其實是軟硬體協同產出的結果,所以想要突破目前的成像限制,更多的光學工程設計與軟體優化的技術也是不可或缺的,例如AI與人工智慧的導入等,都是可用之策。

所以對於系統開發商來說,尋求先進的影像感測器方案固然是一個明顯的對策,但思考進一步結合第三方的光學設計與優質的軟體協助,從整體性的影像拍攝體驗進行改良,才會是最佳對策,而這也是前述這兩家業者能夠持續領先的原因所在。