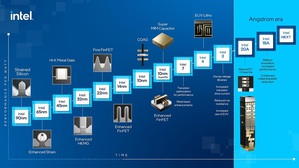

英特爾近期於美國檀香山舉行的年度VLSI國際研討會,公布Intel 4製程的技術細節。相較於Intel 7,Intel 4於相同功耗提升20%以上的效能,高效能元件庫(library cell)的密度則是2倍,同時達成兩項關鍵目標:它滿足開發中產品的需求,包括PC客戶端的Meteor Lake,並推進先進技術和製程模組。

|

| 英特爾公布Intel 4製程的技術細節。 |

對於英特爾的4年之路,Intel 4是如何達成這些效能數據? Intel 4於鰭片間距、接點間距以及低層金屬間距等關鍵尺寸(Critical Dimension),持續朝向微縮的方向前行,並同時導入設計技術偕同最佳化,縮小單一元件的尺寸。透過FinFET材料與結構上的改良提升效能,Intel 4單一N型半導體或是P型半導體,其鰭片數量從Intel 7高效能元件庫的4片降低至3片。綜合上述技術,使得Intel 4能夠大幅增加邏輯元件密度,並縮減路徑延遲和降低功耗。

Intel 7已導入自對準四重成像技術(Self-Aligned Quad Patterning、SAQP)和主動元件閘極上接點(Contact Over Active Gate、COAG)技術來提升邏輯密度。前者透過單次微影和兩次沉積、蝕刻步驟,將晶圓上的微影圖案縮小4倍,且沒有多次微影層疊對準的問題;後者則是將閘極接點直接設在閘極上方,而非傳統設在閘極的一側,進而提升元件密度。Intel 4更進一步加入網格布線方案(gridded layout scheme),簡單化並規律化電路布線,提升效能同時並改善生產良率。

隨著製程微縮,電晶體上方的金屬導線、接點也隨之縮小;導線的電阻和線路直徑呈現反比,該如何維持導線效能抑是需要克服的壁壘。Intel 4採用新的金屬配方稱之為強化銅(Enhanced Cu),使用銅做為導線、接點的主體,取代Intel 7所使用的鈷,外層再使用鈷、鉭包覆;此配方兼具銅的低電阻特性,並降低自由電子移動時撞擊原子使其移位,進而讓電路失效的電遷移(electromigration)現象,為Intel 3和未來的製程打下基礎。

將光罩圖案成像至晶圓上的最重要改變,可能是在於廣泛的使用EUV來簡化製程。英特爾不僅在現有良好解決方案中的最關鍵層使用EUV,而且在Intel 4的較高互連層中使用EUV,以大幅度減少光罩數量和製程步驟。其降低製程的複雜性,亦同步替未來製程節點建立技術領先地位及設備產能,英特爾將在這些製程更廣泛地使用EUV,更將導入全球第一款量產型高數值孔徑(High-NA)EUV系統。