半導體產業的變化,使得Cadence的解決方案不僅完整,

更具備了前後連貫的特色,為的就是希望從問題的源頭開始,

設法將每個環個環結所面臨的問題,作一次性的解決。

過去大家對於EDA(電子設計自動化)的印象,大多停留在扮演晶片設計軟體工具供應商的角色,隨著全球半導體產業的不斷變化,EDA產業也有了全新的樣貌。其中Cadence(益華電腦)應該可以說是變化相當大的業者。

眾所皆知,Cadence在既有的EDA與矽智財(IP)已經耕耘相當長的一段時間,在PCB(印刷電路板)設計領域,Cadence同樣也有相當優異的成績。由於PCB已經進入了終端系統設計整合的階段,對Cadence而言,該公司已經從「協助IC設計」的定位,轉變成「協助系統設計」,所以強化PCB設計軟體的能力也成了Cadence十分重視的課題。

設計垂直流程的一次到位

由於從晶片到PCB設計,Cadence擁有完整的產品組合,在策略上,就是希望能從晶片設計一路貫穿到PCB設計,這中間包含晶片IO電路方塊(IO Cell)、封裝承載晶片接腳(die pad)、封裝與PCB板間接腳(BGA)等,在考慮走線平順前提下,自動完成最佳化處理。透過封裝層級的自動佈線功能 (APR) 及PCB層級的互動式自動佈線功能 (Allegro Auto-Interactive Routing) 進行早期評估,就是希望能在晶片設計之初,就要考慮到封裝與PCB設計的問題,以直接減輕PCB設計的負擔,這種概念被Cadence稱為「IC-Package-PCB Co-design」。

Cadence技術服務部資深應用工程經理林謂昌就表示,這個概念最早就是由Cadence所提出,許多晶片大廠也早已採用這樣的概念平台進行晶片設計,上游的晶片或是設計服務業者可利用此協同設計概念來強化晶片與封裝設計對各式PCB設計的相容性;中下游的ODM與OEM業者則透過Allegro互動式自動布線工具來提升設計效能與品質。

| 圖一 : 每個終端系統都會有晶片到系統設計的階段,Cadence以完整連貫的解決方案來滿足市場需求。 |

|

PCB設計 由Allegro擔綱主角

若單以PCB設計來說,其相關系列的產品線,Cadence則是以「Allegro PCB Designer」作為代表。

林謂昌談到,你可以把PCB想像成一座航空母艦,不同的晶片都放在同一個載板上,有主被動元件,高度有高有低,整個系統設計過程會牽涉到高速數位訊號布線問題(像DDR4、PCIE Gen3與USB3.1等,電源供應系統設計,因電生熱問題,機構與電路板相容問題及最終EMI(電磁干擾)設計。

一個好的設計平台,若能將物理層級(布線、機構)與電性層級(電源、熱、EMI)整合考量,達到首次設計成功,那將會大大降低成本並提升產品品質。Allegro PCB設計及Allegro-Sigrity電性協同分析平台即能達成此目的。

物理層級設計是一切產品的基礎,布線品質與快速完成時間往往是產品設計的重點要求,而Allegro TimingVision正是為此誕生。

TimingVision克服高速數位訊號設計問題

Allegro TimingVision平台試圖解決高速訊號的設計與電路佈局所面臨的挑戰。林謂昌進一步談到,晶片之間的溝通,是透過時脈來調度資料傳輸與控制訊號,但問題在於,即便晶片之間訊號走線的距離相等,資料/控制訊號和參考時脈(或strobe) 的抵達時間卻不見得會相同,更甚者兩者的誤差之大,將十分容易造成訊號在電路接收端無法滿足判斷訊號邏輯所需最小的建置與維持時間(Setup/Hold time) 的情況。在PCB面積有限與線寬間距等諸多條件限制下達成時序收斂是一大挑戰。林謂昌透露,一般大家所了解的「差動訊號」像是USB、PCI Express、SATA、乙太網路及DDR3/4等技術,這類的電路是整個系統佈局最為困難的部份。因此Cadence以Allegro TimingVision核心技術為基礎,發展出AiDT (auto-interactive delay tune) 、AiPT (auto-interactive phase tune) 、AiBT (auto-interactive breakout technology) 等技術,能讓傳統的布線設計效率提升超過65%以上,像ODM廠和碩聯合(Pegatron)即利用此技術提升設計效能。

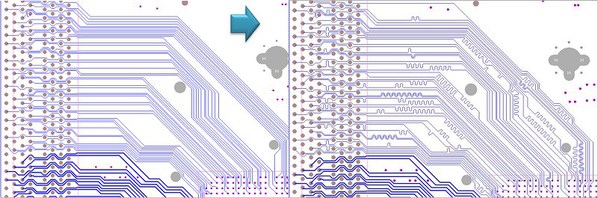

AiDT主要針對平行匯流排像DDR3/DDR4走線,選定參考時脈或strobe訊號長度為依據,在走線長度與間距規範下 (Constraint Management) 自動調整資料/位址/控制訊號與其參考時脈或strobe之間的長度關係以符合規範。

| 圖二 : 利用AiDT較傳統手動怖線調整長度效能至少快50%以上 |

|

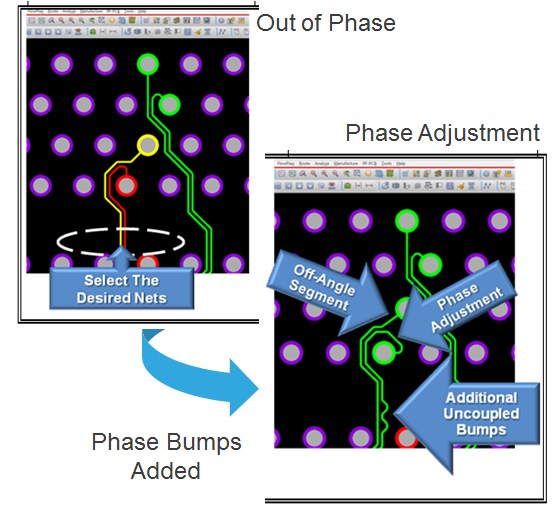

至於AiPT則是針對差動訊號對 (differential-pair) 兩訊號間的靜態或動態相位調整補償以減少共模訊號的產生。

| 圖三 : 透過使用者選擇欲調整的差動對進行自動相位補償調整 |

|

AiBT是針對走線在IC出腳位處,考量走線規範下在訊號連接的IC兩端進行最佳化處理讓走線順暢不絞線。

在約束走線規範設定(如訊號阻抗要求,走線間距要求等)完成後再加上TimingVision技術即能將設計在第一版就符合要求的目標。最後再將零件與機殼機構圖透過Step Model格式輸入到Allegro Designer平台以檢視機殼與PCB零件機構有否衝突之處,以達到所謂ECAD與MCAD設計整合考量。

透過MCAD 3D Step Model在Allegro平台內檢視,零件與機構干涉問題皆能提早發現。

電源與訊號完整性設計也要前後銜接

物理層級設計完成後,必須對PCB設計做最後簽核(Sign-Off)工作,訊號與電源完整性及因電生熱問題都必須在此簽核階段分析是否符合晶片正常工作所要求規格。而電源完整性是一切的基礎。

傳統的電源分析是側重在嚴謹的分析晶片端電子漂移 (EM) 及靜態與動態IR 壓降上。但是,由於所有送往晶片的電力都是從電壓源開始,在抵達晶片前至少會先流經PCB及晶片封裝,所以許多假設是建立在忽略這兩者之上。在更小的幾何尺寸及更低的電力需求下,因忽略PCB與晶片封裝的影響而引起的失準,可能會造成第一次便告成功與重啟晶片設計的巨大差異。

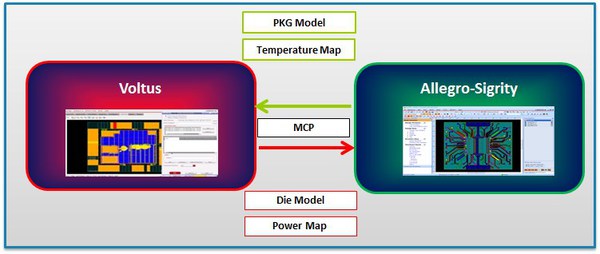

依循「IC-Package-PCB Co-design」的核心思想,Cadence在電源設計方面也是如此,Cadence現在將晶片、晶片封裝及印刷電路板的電源整合解決方案合而為一,實現了提高精確度的共同分析解決方案,並且讓設計團隊可以預先判定晶片、封裝體及印刷電路板的電源完整性。 Voltus? IC 電源分析解決方案可以與 Allegro-Sigrity電性協同分析平台連結,滿足了整個系統電源與熱共同分析解決方案。

| 圖七 : 晶片端的電源模型、功耗分布圖與封裝及PCB端電源模型和溫度分布圖透過MCP協定來交換資料以達到協同分析的能力 |

|

另外,訊號完整性驗證是無法獨立於電源考量,而是一個具有考慮電源效應下的訊號完整性。一般在系統SSO/SSN分析即是IO電源負載最重的情況下是否還能有良好的電源供應以確保訊號的品質。Allegro-Sigrity平台能將晶片、封裝到PCB所有模型整合,並將系統電源從VRM,一路從PCB到晶片端,包含了板級電容與晶片電容效應完整考慮。

結論

整體來看,為了克服PCB設計的挑戰,Cadence從晶片設計開始,就採取了行動,這也的確與Cadence朝向系統設計前進的作法一致。重點在於,Cadence充分考量了PCB乃至於整體系統設計所面臨的問題與關聯性,所以各自在不同的設計環結提供了對應的解決方案,但解決方案之間又能彼此連貫,對於晶片設計甚至是系統整合等工程師們,不僅提供了完善的設計工具,也解決了設計流程之間的溝通問題。