SoC技術的發展雖然有效降低了電子產品的成本,但卻也增加了SoC晶片的設計、製造和測試難度。面對越來越複雜的SoC晶片,測試工程師除了必須達到全面完備測試的要求之外,又得不斷嘗試降低測試成本的方法,因此降低測試成本也目前產業最為關注的焦點之一。

採用低成本的ATE方案,可以明顯降低晶片測試成本,但是SoC晶片中整合度高、越來越複雜,對ATE的測試通道數、測試向量深度、測試頻率、同測、併發測試能力等,都出現了更高的要求,低成本的ATE方案很難同時滿足這些要求。僅靠一昧地降低測試設備成本,並不是一個很好的解決方案,需要尋求新的降低SoC測試成本的方法。

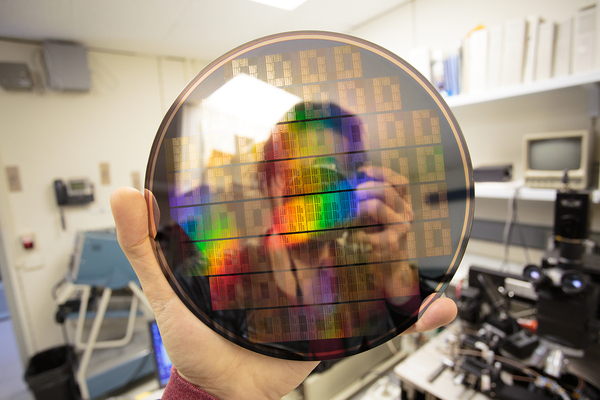

| 圖1 : 晶片的測試時間是影響晶片測試成本的重要因素之一。 |

|

SoC測試挑戰

晶片的測試時間,是由晶片測試程式的執行時間,加上與其配套的設備執行時間所組成。晶片的測試時間是影響晶片測試成本的重要因素之一,對於產業化測試,除了盡可能減少設備執行時間外,還要同時考量被測晶片的特點和測試系統的運作方式,並對晶片的測試程式進行優化,加快程式的運行速度,以達到節省晶片測試時間、降低測試成本的目的。

由於在同一個晶片中整合了不同的功能模組,使得SoC晶片的測試過程也變得極為複雜。要實現全面性的完整測試,需要的測試項目更為繁複。因此,晶片測試時間,也將由晶片測試程式的複雜程度決定,前期測試方案的設計變得很重要,晶片測試程式調試完畢後,投放生產測試之前,透過測試程序的最佳化,可以節省晶片的測試時間。

由於在同一個晶片中整合了不同的功能模組,

使得SoC晶片的測試過程也變得極為複雜。

要實現全面性的完整測試,需要的測試項目更為繁複。

對同一晶片的測試,測試機台一般都是按造流程逐項進行,這樣的流程便是測試流程。一般來說,測試流程會綜合考慮各種因素,來對流程中的測試項目進行較為合理的測試排序。在測試流程中,通常會將連線測試排在首項,連線性測試是用於確保測試設備的介面與晶片的連接是正常的。而直流參數測試則通常會安排在前段測試流程中,因為漏電流和功耗等直流參數,也是晶片製程良善與否的重要指標。

多模SoC晶片的測試,通常會採用分別測試的方式,先測試數位電路,再測試類比電路。這是因為數位電路的測試原理相對簡單,所需的測試資源要求較低,測試時間也相對較短。至於類比電路的測試過程,由於需要採用比較複雜的測試方法和測試設備,相對測試時間也較長。在測試過程中,可以透過收集處理失效資料的方式,將失效機率較大的測試項目排在前面,來減少接下來過程中,失效晶片的測試時間,如此也可有效降低測試成本。

智慧化測試方案

特別是針對物聯網的崛起,在物聯網時代,要選擇測試設備的平台時,成本與上市時間都是關鍵要素。功能固定的大型測試機台,可以滿足某些公司的標準,例如必須測試記憶體和微控制器的廠商。不過隨著廠商必須持續創新,改良自家的裝置功能,他們也會需要更具智慧效能的ATE平台,並依據創新需求來進行有效擴充。

美國聯邦航空總署近期決定,可讓乘客使用行動電子裝置,只要設定為航空模式即可。這關鍵就在於軟體層面,而非硬體。以前,使用者必須購買新的裝置,才能享有全新的功能。但現在的智慧手機、電視、電腦、甚至汽車等,都能夠運用可重設的韌體技術,在上市之前,進一步擴充或加強硬體裝置的功能。

隨著市場變化,且裝置複雜度越來越高,工程師也被迫接受這些變化,準備好面對無法預期的一切。這些智慧裝置可透過軟體升級,來加強情境智慧效能,測試設備也應該能夠辦得到。例如透過軟體來定義測試設備,相關廠商即可投資能滿足目前測試需求、也可因應未來變化的平台,同時盡可能減少資本投資。模組化硬體當然扮演十分吃重的角色,不過軟體平台才是平台式、智慧型ATE方案的關鍵。

結語

由於物聯網相關方案不斷在更新,測試工程師都必須確保這些佈置於物聯網的新裝置可提供安全、穩定、具成本效益的運作效能。也有越來越多的企業,把更具智慧效能的平台式方案應用於測試設備,以便克服這些難題。隨著成本與上市時間持續縮減,創新公司需要更好的SoC測試方案,來滿足每一個不同環節的測試需求。

愛德萬:擴充性架構 解決物聯網測試四大挑戰

愛德萬(ADVANTEST)的V93000測試機台,目前已經受到許多物聯網產業相關的客戶,應用於作為物聯網各種元件的測試平台。最主要的原因,就在於V93000 PS1600機台提供了Universal Pin的功能,因此在單一的板卡上,可以提供數位、類比、power、或基礎RF的測試能力。換句話說,一張卡片就可以滿足各種不同的測試需求。

愛德萬台灣總經理吳慶桓指出,V93000測試機台的優點,可以從四個方向來觀察。第一,由於物聯網的元件整合度提高,因此測試設備的能力就必須要多元。然而。傳統的解決方案不但緩不濟急,投資成本也過於高昂。而Universal Pin的架構,正好可以用來滿足這些物聯網廠商對於多元測試的需求。因為以功能性來看,物聯網的設備並不需要像是行動裝置,使用到過於高階的測試機台,物聯網的元件功能性並沒有如此複雜,但卻必須確定機組的基本功能都能夠正常運作。而這些功能,Universal Pin的架構都可以做得到。

第二,物聯網解決方案的低功耗特性是不可或缺的。物聯網的所有元件,都必須要能夠確定擁有低功耗的能力才行。也因此,在機台方面,也必須要能夠提供十分精確的量測條件,來確定這個設備能夠正常地運作。

而在PS1600的板卡上,針對電壓的部分,目前可以量測到最小的1mV,而在電流的部分,最小可以量測到10 nA,這對於目前物聯網的測試來說,已經是非常不錯的規格。

第三,物聯網產品本身的價格一定要夠低。然而這也使得相關廠商的測試成本隨之被壓低。在測試成本壓低的情況下,要同時去注意高整合度,以及維持一定的品質,很多的測試設備並沒辦法同時對這些條件進行妥協。也因此,唯一能做到的,就是提高單位時間的產出。

V93000機台的好處,就是其可擴充性。也就是可以隨著產品的特性,來組合所需要的模組,或者擴增性能,例如從比較小的測試機台,換成比較大的測試頭。這樣一來,就可以放更多的模組,也就可以達到更多的同測數。

只是,當同測數提高了,錯誤產生的機率也會相對提高。當同測數拉高的時候,也必須保證要能維持一樣的同測效率。目前愛德萬與客戶的合作之中,大致上都能維持在97-98%這樣的高效率。而這也是V93000這個機台之所以為什麼能在如此多客戶與這麼多市場競爭的情況下,依然能夠受到青睞的主要原因。

第四,不可避免的,物聯網許多狀況都是不可預知的。因此如何選擇一個正確的機台,能夠有比較長遠的使用,以及保有其擴充性,這是未來在物聯網的測試機台選擇上,一個很大的重點。

| 圖3 : 愛德萬測試V93000平台(source:advantest.com) |

|

吳慶桓說,V93000從剛上市起,就一直沿用相同的擴充性架構,讓客戶能夠依據他的需求,來選用機台的模組。也可以針對不同設備的大小,來選擇不同的測試頭。所以這是整個面對未來不確定性與變動性很大的情況之下,V93000仍保有很好的快速上市、以及大量生產等優勢。V93000在物聯網測試上,也正是目前最主力的機種,未來愛德萬也將會持續推動這個機台,讓客戶有更多的能量,來因應市場的變化。