高速類比數位轉換器(ADC)的發展已經達到每秒千兆次採樣(GSPS)的水準,並且可用頻寬也相對地增加。這些性能的提升也帶來了許多挑戰,其中一項,就是對電源的要求更加複雜。例如,AD9625是一款2.6 GSPS的ADC,它需要7個獨立的電源軌,同時,並分為3種電壓:1.3 V、2.5 V和3.3 V。

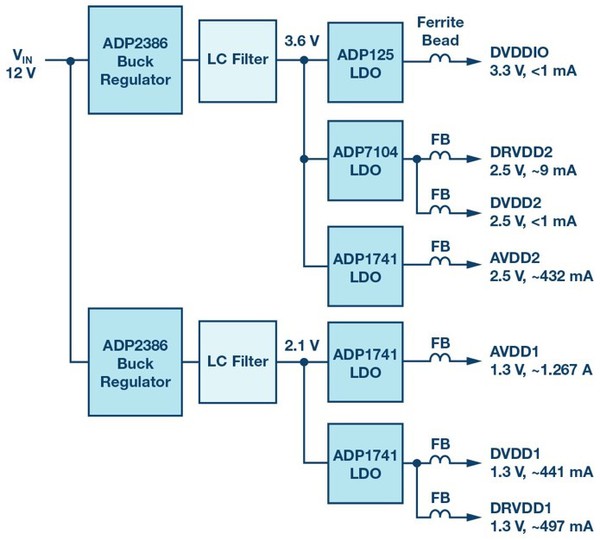

完整的ADC電源系統必須具有高效率,適合放入空間擁擠的PCB,並且產生的輸出雜訊可與負載敏感度相匹配。平衡這些要求(通常彼此衝突)是系統設計人員面臨的最主要的參數優化問題。通常,解決這個問題的辦法是將切換開關穩壓器(雜訊大但效率高)與低壓差(LDO)後級穩壓器相結合,如此效率雖然相對較低,但是能夠減少電源雜訊。圖1則是一個典型系統的方框圖。

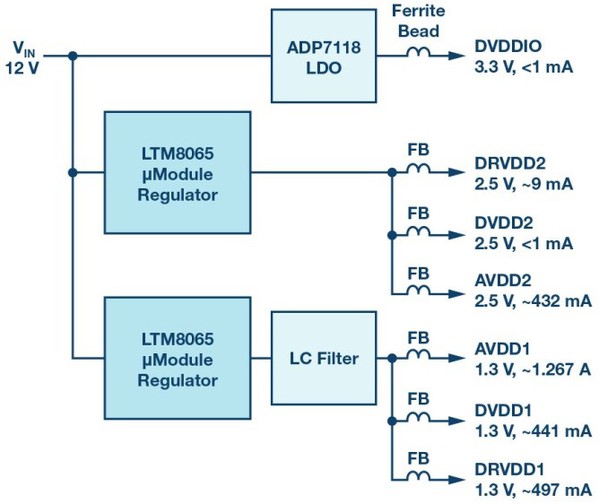

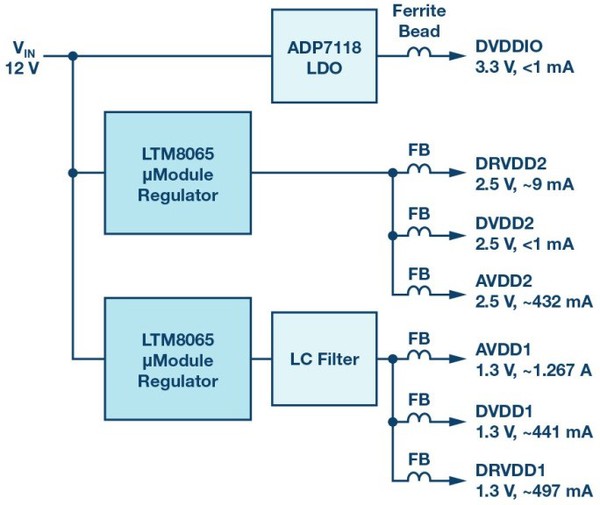

遺憾的是,效率與雜訊性能的優化通常會增加系統的複雜性。圖2是採用μModule Silent Switcher穩壓器的替代性電源系統,此一解決方案可為ADC提供低雜訊供電,而且比傳統解決方案效率更高。

考慮雜訊因素

系統設計人員必須對負載敏感度進行量化考慮,並需要將其與電源雜訊相匹配。透過在電源路徑中使用LDO穩壓器,可將電源雜訊降至最低;它既可以作為獨立穩壓器(如圖2所示),也可作為切換開關穩壓器的後級穩壓器(如圖1所示)。LDO穩壓器能夠抑制輸入電源雜訊,該性能可用電源抑制比(PSRR)來衡量。

使用LDO穩壓器改善雜訊性能的代價是效率較低。LDO穩壓器在高降壓比下效率會降低,因為它們必須在導通元件上消耗額外的功率,因此使用LDO穩壓器時,期望能最大程度地減小降壓比以獲得最高效率。這就是為什麼它們經常被用作後級穩壓器,接在固有雜訊雖大但是效率較高的開關穩壓器後面,這樣就可在LDO穩壓器輸入端之前先對主電源軌進行降壓。然而,當它們被用作後級穩壓器時,便需要額外的餘裕以最大化LDO穩壓器的PSRR性能,而這進一步降低了電源的整體效率,尤其是在較重負載時。

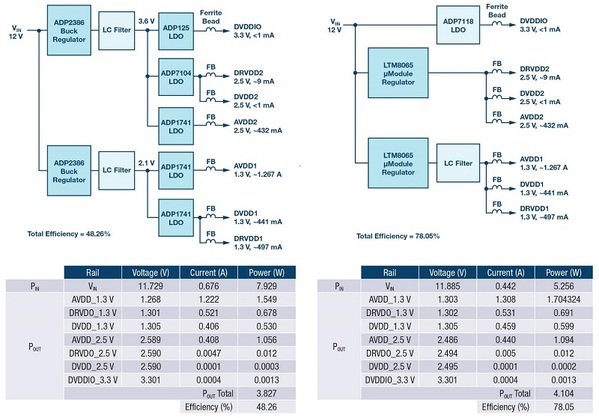

| 圖1 : 採用切換開關穩壓器和LDO穩壓器的GSPS ADC基準電源設計(傳統設計)。 |

|

| 圖2 : 傳統切換開關穩壓器和LDO電源系統(如圖1所示)的替代方案。該設計採用兩個LTM8065 μModule Silent Switcher穩壓器直接為AD9625供電。這種設計雜訊低、更緊湊、更高效(未經濾波的LTM8065設計)。 |

|

考慮簡化設計和尺寸因素

傳統切換開關穩壓器加LDO的系統通常採用分立式元件來實現,但其導致PCB尺寸大且設計複雜,這違背了小尺寸和簡化設計的目標。相較之下,可採用μModule穩壓器來實現這些目標,因為在其封裝內已整合了關鍵的穩壓器元件,尤其是尺寸相對較大的電感,因而使解決方案的PCB非常精小。

此外,μModule穩壓器通常能夠處理足夠大的負載,使設計人員能夠在單個μModule輸出上組合多個相同電壓的電源軌。大電流能力使得在現有基於μModule穩壓器設計中添加電源軌成為可能,簡化設計修改,從而縮短產品上市時間。

此處顯示的基於μModule穩壓器的解決方案非常高效且精小,很適合於12位元2.6 GSPS的高性能ADC AD9625,其由Power by Linear Silent Switcher μModule穩壓器LTM8065 供電。Silent Switcher技術幾乎消除了不可預測且難以濾波的高頻雜訊,而且可採用與ADC敏感度敏感度完全匹配的電源。

為了將μModule穩壓器解決方案與傳統電源配置進行測試比較,採用2.5 A降壓型μModule穩壓器LTM8065為AD9625的1.3 V和2.5 V電源軌供電。對LTC電源模組兩個電源軌上的ADC電源雜訊敏感度和輸出頻譜都進行了檢測。

傳統的AD9625 ADC基準電源系統設計

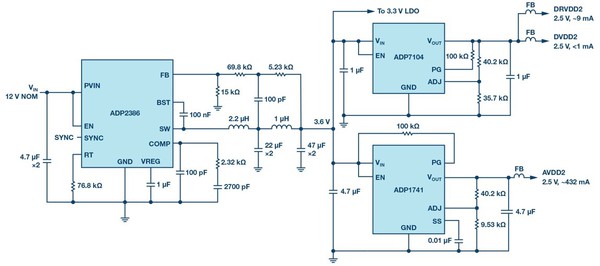

圖3是傳統推薦用於AD9625 2.6 GSPS ADC電源配置的部分原理圖。圖3中僅顯示了2.5 V電源軌,它可代表每個電源軌的典型電流要求。在完整的電源中,7個不同的電源域主要分為3路電壓:1.3 V、2.5 V和3.3 V。圖1中的框圖是完整電源的概要。

在此系統中,切換開關穩壓器是兩個帶LC濾波器的20 V/6 A降壓型轉換器ADP2386,它們作為3.6 V和2.1 V中間電壓的前級穩壓器。圖3所示為3.6 V輸出穩壓器。這些中間電壓在ADC的每個調節輸入軌上由LDO穩壓器進一步降壓。LDO穩壓器為ADC提供調節電壓,可有效減少切換開關穩壓器的輸出紋波。

| 圖3 : 原理圖顯示為AD9625供電的3個2.5 V電源軌,採用傳統的切換開關穩壓器和LDO系統。另外4個電源軌沒有在此處顯示,但在圖1的框圖中有顯示。 |

|

傳統的基準系統成功生成了穩定調節的低雜訊輸出,但其代價是複雜性增加。在電路板上放入眾多元件會很困難,並且LDO的效率在最大負載時會受到影響,還可能會產生熱問題。有沒有更好的辦法?有。

LTM8065 μModule穩壓器直接為AD9625 ADC的1.3 V和2.5 V電壓軌供電

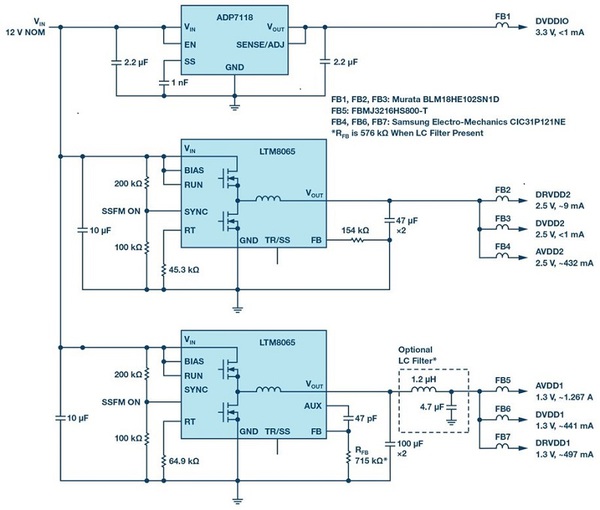

圖4是基於圖2框圖的替代性電源解決方案的完整原理圖。該系統由兩個LTM8065 μModule穩壓器和一個ADP7118 LDO穩壓器組成。LTM8065是一款40 V輸入、2.5 A Silent Switcher μModule穩壓器,採用耐熱增強的精小過壓成型球柵陣列封裝(BGA)封裝。該模組中包含一個切換開關控制器、一個電感和其他支援元件。LTM8065支援0.97 V至18 V的輸出電壓範圍和200 kHz至3 MHz的切換開關頻率範圍,輸出電壓由單個外部電阻設定。僅需添加輸入和輸出濾波電容便可構成完整的穩壓器。

| 圖4 : 傳統ADC電源系統的替代方案。這款完整的七電源軌解決方案可為AD9625 2.6 GSPS ADC供電。請注意,完整的原理圖與圖2框圖沒有太大區別。 |

|

在這個解決方案中,LTM8065直接為1.3 V電源軌和2.5 V電源供電。3.3 V電源軌直接由ADP7118低雜訊LDO從12 V電源調節供電。3.3 V軌電流小於1 mA,因此LDO穩壓器上的功耗可忽略不計。

中標:關於負載對電源雜訊的敏感度因素

ADC的電源敏感度是電源系統設計的首要考慮因素。透過測量ADC本身的PSRR或從資料手冊中檢索PSRR,可以確定電源雜訊敏感度。有兩種類型的PSRR:靜態PSRR和動態(交流)PSRR。靜態PSRR指電源電壓變化與由此產生的ADC失調誤差變化之比值。這並不是主要的關注點,因為DC-DC轉換器應該會為負載提供穩定調節的電壓。而另一方面,動態(交流)PSRR是電源設計人員關注的指標,因為它表示ADC在一定頻率範圍內對電源針腳上的雜訊進行衰減的能力。

ADC的交流PSRR可透過在電源針腳上注入正弦波訊號的同時,直接在被測電源針腳上測量注入的正弦波訊號幅度(探測靠近電源引腳的去耦電容)而獲得。數位化雜散出現在相應頻率的ADC的FFT雜訊基準上。在ADC FFT頻譜上測量的注入訊號幅度與相應數位化雜散幅度之比是電源抑制比。圖5是一個典型的交流PSRR測量配置的方框圖。

使用AD9625 2.6 GSPS ADC,在1.3 V類比電源軌上主動耦合1 MHz、100 mV峰峰值正弦波。在ADC的FFT雜訊基準上出現相應的1 MHz數位化雜散,其幅度取決於1 MHz處的PSRR。在這種情況下,在FFT中,1 MHz數位化雜散出現在轉換器雜訊基準之上,為-61.8 dBFS,對應的峰峰值電壓為892μV p-p ,參考類比輸入滿量程範圍1.1 V。

Calculating the ac PSRR at 1 MHz using equation 1 yields an ac PSRR of 41 dB.

使用公式1計算1 MHz的交流PSRR,得到交流PSRR為41 dB。

其中:

數位化雜散是ADC FFT中觀察到的雜散,與電源針腳上的注入漣波相對應。本例中,雜散為892μV p–p.。

注入漣波是在輸入電源針腳處耦合,並測量的正弦波。這裡的漣波幅度為100 mV p-p。

附帶LC濾波器的LTM8065 μModule穩壓器為AD9625 ADC供電,提供1.3 V電源軌

圖6顯示,與2.5 V AVDD軌相比,1.3 V AVDD軌更容易受到電源雜訊的影響——特別是在LTM8065的切換開關頻率範圍(200 kHz至3 MHz)內。圖7是也是一個LTM8065解決方案,但它增加了一個低通LC(電感-電容)濾波器,用於1.3 V電源軌組合。

| 圖7 : 在1.3 V電源軌添加LC濾波器,以進一步降低雜訊。 |

|

低通LC濾波器的元件推薦取決於需要的濾波量。對於1.3 V電壓軌而言,至少需要20 dB濾波才能將切換開關電壓降低到資料轉換器的雜訊基準。截止頻率約為67 kHz時使用1.2μH和4.7μF的LC組合(比LTM8065的1.3 V電源軌的切換開關頻率低大約1個10倍頻程)。建議使用直流電阻(DCR)小的電感,以防止電感上出現過大的壓降和功耗。

至於電容,可以使用多層陶瓷電容(MLCC)。MLCC具有低等效串聯電阻(ESR),可在電容自諧振時提供良好的衰減性能。電容的最小阻抗由其ESR決定。MLCC還具有低等效串聯電感(ESL),可在高頻下提供出色的去耦性能。

鐵氧體磁珠用於過濾ADC電源軌上的切換開關穩壓器產生的高頻雜訊。這些磁珠還為每個組合軌提供高頻雜訊隔離。流過磁珠的推薦電流應為鐵氧體磁珠直流電流額定值的30%左右,以防止磁芯飽和,從而降低磁珠的有效阻抗和EMI濾波性能。具有低直流電阻的鐵氧體磁珠可最大限度地降低磁珠上的壓降和功耗,尤其是在高電流電壓軌(如AVDD 1.3 V)上。

評估結果

此處顯示的三種電源配置透過具有262k個資料點的快速傅立葉轉換(FFT)獲取的結果,對AD9625的訊號雜訊比(SNR)和無雜散動態範圍(SFDR)進行比較。第一個配置是傳統的基準電源(如圖1所示)。第二個配置是不帶濾波的LTM8065(如圖2所示)。第三個配置是帶有LC濾波器的LTM8065提供1.3 V電壓軌(如圖7所示)。兩個基於LTM8065的解決方案均支援擴頻調製。

表1顯示了AD9625在由三種電源配置供電時的動態性能。使用了兩種不同的ADC類比輸入載波頻率(729 MHz和1349 MHz)。當由兩個基於LTM8065的電源供電時,ADC的SNR和SFDR結果與基準電源的結果相當。資料顯示,LTM8065無需使用額外的LDO穩壓器即可直接為AD9625供電,大幅簡化了整體解決方案。

表1.AD9625 2.6 GHz動態性能

|

輸入頻率(MHz)

|

SNRFS (DB)

|

SFDR (DBC)

|

|

基準電源

|

LTM8065未經濾波

|

LTM8065

帶LC濾波器

|

基準電源

|

LTM8065未經濾波

|

LTM8065

帶LC濾波器

|

|

729

|

57.01

|

57.03

|

57.01

|

79.87

|

79.72

|

80.11

|

|

1349

|

56.53

|

56.49

|

56.54

|

78.41

|

80.06

|

80.77

|

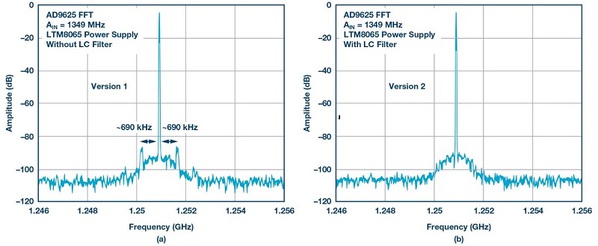

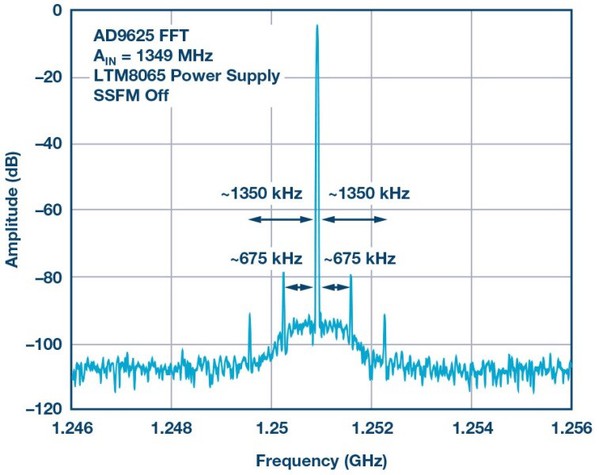

仔細檢查1349 MHz附近的頻段,發現有邊帶雜散,它與LTM8065(用於1.3 V電壓軌)690 kHz切換開關頻率(擴頻功能)相關,但調製幅度遠小於典型的SFDR規格(如圖8a所示)。然而,最好能消除這些邊頻雜散(如圖8b所示),因此建議在LTM8065解決方案中添加LC濾波器。

| 圖8 : 使用兩個不同的電源系統:基於μModule穩壓器的電源系統,一個不帶LC濾波器(a)而另一個附帶LC濾波器(b),透過比較AD9625的FFT結果,可以發現LC濾波器對1349 MHz載波頻率附近的調變雜散的影響。 |

|

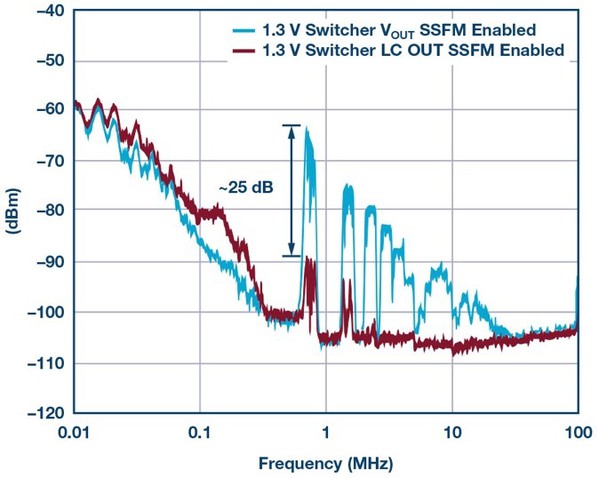

在LC濾波器部分之前和之後探測到的頻譜輸出如圖9所示,它表明雜訊濾波性能的改進高達25 dB。

| 圖9 : LTM8065在1.3 V電壓軌上的頻譜成分(啟用SSFM)。 |

|

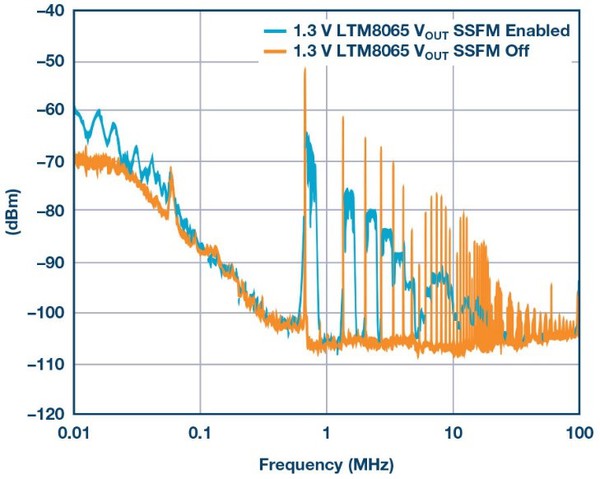

展頻調頻(SSFM)透過在從程式設計值直至高出該值約20%的範圍內連續改變切換開關頻率,降低了轉換器基波工作頻率下漣波的峰值幅度。SSFM在需要低峰值EMI/低漣波幅度的系統中最為實用。SSFM的優勢如圖10所示,它顯示了啟用了SSFM和關閉SSFM時LTM8065 1.3 V輸出的頻譜成分。基波頻率處的漣波峰值幅度降低約為10 dB至12 dB,並且諧波峰值明顯降低。

| 圖10 : SSFM啟用和關閉時的LTM8065 1.3 V電源軌的頻譜成分。 |

|

使用LTM8065直接為1.3 V電源軌供電(展頻關閉)會產生較高調變峰值,而發生二次諧波失真(如圖11所示)。

| 圖11 : SSFM禁用時LTM8065 1.3 V電源軌的1349 MHz類比輸入載波的詳細資訊。 |

|

測得的系統效率

基準電源和帶LC濾波器的LTM8065系統之間的效率比較如圖12所示。LTM8065電源解決方案的效率提高30%。

| 圖12 : 基線電源設計與基於LTM8065的系統(版本2)之間的效率比較。 |

|

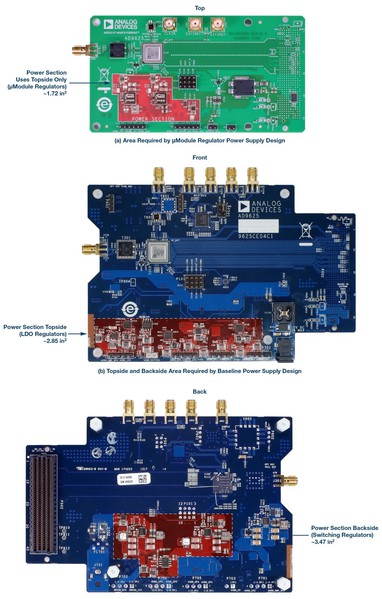

PCB尺寸比較

為了說明μModule穩壓器解決方案的尺寸優勢,我們在PCB上實現帶LC濾波器、基於LTM8065的解決方案。將其電源部分的面積與現成的EVAL-AD9625評估板(使用基準電源設計)的電源部分進行比較。

圖13顯示了EVAL-AD9625標準評估板(基準電源)和修訂版的AD9625評估板(帶LC濾波器的LTM8065 μModule穩壓器)的比較。使用LTM8065的電源解決方案的元件幾乎全部都位於PCB的正面,而現成EVAL-AD9625評估板的為分立解決方案,其電源元件則需分佈在正面(LDO穩壓器)和背面(切換開關穩壓器)兩邊。基於LTM8065的解決方案可減少70%以上的電源接腳佔位。

| 圖13 : 使用μModule Silent Switcher穩壓器替代傳統的控制器/穩壓器時,電源所需的面積大大減少。將(a)使用LTM8065的AD9625修訂版展示板與(b)現成的AD9625評估板進行比較。兩個系統的電源部分都均已突出顯示。 |

|

表2比較了基於LTM8065的系統和基準電源系統的元件總數和元件接腳佔位尺寸。LTM8065解決方案使用的元件總數減少一半以上,接腳佔位尺寸只有一半左右。

表2.不同方案的電源部分元件總數和接腳佔位總面積

|

?

|

帶LC濾波器的LTM8065

|

基準電源

|

|

元件(個)

|

元件面積(mm2)

|

元件(個)

|

元件面積(mm2)

|

|

切換開關穩壓器(IC/模組)

|

2

|

78

|

2

|

32

|

|

LDO IC

|

1

|

4

|

5

|

82

|

|

被動元件

|

21

|

58

|

58

|

159

|

|

總計

|

24

|

140

|

65

|

273

|

結論

LTM8065 μModule Silent Switcher穩壓器可為AD9625 GSPS ADC供電,相較於傳統的分立式解決方案具有明顯的改善,而且不必犧牲ADC的動態性能。透過使用LTM8065直接為AD9625的1.3 V和2.5 V電源軌供電,可以大幅減少元件數量與電源板尺寸。

而進行一些濾波更有幫助。當類比輸入頻率非常高時,會在類比輸入載波頻率和穩壓器輸出漣波頻率之間觀察到調變效應。由於這種調變效應,在類比輸入載波周圍出現邊帶雜散,並且在類比輸入頻率較高時更為明顯。

由於LTM8065穩壓器在切換開關頻率附近的低電源抑制,1.3 V電壓軌上的雜訊成為調變效應的罪魁禍首。雖然調變雜散的幅度不超過無雜散動態範圍規範,但最好使用簡單的LC低通濾波器來抑制雜散,以對輸出紋波進行衰減。如此方可產生更乾淨的數位化類比輸入載波,無邊頻調變。

Module穩壓器電源解決方案的系統效率達到78%,比現有的AD9625展示板提高了約30%。除了更高的效率(從而簡化了熱管理)之外,得益於LTM8065電源的獨立整合和精小特性,PCB板面積和元件數量也可大幅地減少。

參考文獻

[1] Eco,Jefferson和Aldrick Limjoco,“鐵氧體磁珠揭秘”,《類比對話》,2017年2月。

[2] Jayamohan,Umesh,“為GSPS或RF採樣ADC供電:切換開關與LDO”,《類比對話》,2016年2月。

[3] Jayamohan,Umesh,“高速ADC電源域 RAQ”,《類比對話》,2018年5月。

[4] Rob Reeder。“高速ADC的電源設計”,ADI公司,2012年2月。

[5] Scott, Kevin和Greg Zimmer,“通過擴頻調製 降低EMI”,ADI公司,2014年。

[6] Ye, Zhongming,“面向汽車和工業應用的 40 V輸入、3.5 A Silent Switcher μModule穩壓器”,ADI公司,2018年1月。

(本文作者Aldrick Limjoco1、Patrick Pasaquian2、Jefferson Eco3 為ADI菲律賓公司1應用經理、2設計與佈局工程組應用工程師、3應用開發工程師)