現今嵌入式視覺系統設計人員需要迎合眾多市場趨勢。例如,現在使用感測器設計的數量不斷增加,以便於收集更多資料或實現新的功能。比如在汽車市場,幾十年前汽車廠商在車輛上安裝一個備用攝影鏡頭就算是創新之舉,而現在已經開始將攝影鏡頭用於車道偏離監控、速度標誌牌辨別和許多其他智慧駕駛的應用。

同時,嵌入式視覺系統設計師正逐漸採用符合行動產業處理器介面(MIPI)聯盟標準的元件。MIPI起初是為行動市場開發的,定義了行動裝置的設計人員在建構高效能、高成本效益、可靠的行動解決方案時所需的硬體和軟體介面標準。在過去幾年中,MIPI已經成為開發嵌入式系統的主流標準。包括工業和汽車等領域的各類應用的設計人員都已經意識到這一點,並且開始尋找方法來利用行動元件提供高效能和規模經濟的優勢。

縮短上市時間帶來的壓力也提高對便於使用的嵌入式視覺解決方案的需求,只提供晶片的做法已經遠遠不夠了。這些壓力讓設計人員迫切地需要一個嵌入式視覺設計環境,能夠提供所有硬體、軟體、IP和參考設計,從而快速設計和開發終端產品。同時,當前的使用者希望他們的嵌入式顯示器能夠提供如消費性電子產品般反應迅捷的體驗。啟動緩慢的嵌入式顯示器會帶來視覺偽像,破壞使用者體驗。

全新的挑戰

這些快速發展的趨勢在創造機會的同時,也為嵌入式視覺設計師帶來嚴峻的挑戰。首先,許多嵌入式系統中使用的攝影鏡頭和顯示器與當今的應用處理器(AP)的介面類型或數量不匹配。AP上為感測器提供的I/O很有限,卻又要支援各類顯示器和感測器,更為棘手的是,各種應用的顯示大小和解析度也不盡相同。此外,由於工業顯示器使用壽命較長,許多尚在使用的顯示器最初是通過傳統介面連接的。因此當嵌入式應用的設計人員在設計中不得不使用傳統或專用的顯示器和感測器時,如何有效利用MIPI元件市場的優勢?

為了支援使用更多感測器和更有效地管理I/O資源,設計人員需要可程式設計的解決方案來彌補I/O限制性。理想狀況下,此解決方案具有整合感測器輸入能力,並且讓設計人員對資料進行預處理以減少處理器的負載。理想的解決方案還需要是可程式化設計的,能夠輕鬆地適應客製化的顯示器設計。以往設計師只能透過為每種顯示器類型開發專門的ASIC來支援不同的顯示器尺寸和解析度,然而可程式化設計的解決方案,讓設計人員能夠使用單個元件實現不同的顯示器要求。

CrossLink系列FPGA這款可程式化設計的影像橋接元件,支援連接行動圖像感測器和顯示器的各類協定和介面。為了滿足嵌入式影像市場不斷增長的需求,CrossLinkPlus為CrossLink的增強版本。為了滿足使用者對顯示器無縫啟動的需求,CrossLinkPlus新增2 Mbit的嵌入式快閃記憶體作為配置儲存體。搭載片上快閃記憶體的CrossLinkPlus能夠在10 ms內瞬時啟動,而人腦一般無法在15 ms內察覺圖像,因此不會產生偽像干擾使用者體驗。片上快閃記憶體可支援現場重新程式設計。

| 圖一 : CrossLinkPlus FPGA(source:萊迪思) |

|

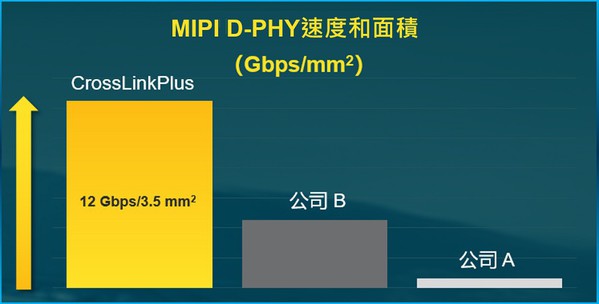

CrossLinkPlus擁有同尺寸FPGA中速度最快、功耗非常低的MIPI D-PHY。此款FPGA封裝尺寸僅為3.5 mm x 3.5 mm,一共支援12 Gbps D-PHY。除了高速MIPI D-PHY外,CrossLinkPlus還擁有6K LUT可程式化設計FPGA架構和靈活的高速I/O,支援MIPI CSI-2、MIPI DSI、LVDS、SLVS200、CMOS和Sub-LVDS等介面的影像橋接。CrossLinkPlus能夠連接這類顯示器和感測器,為設計團隊提供極大的設計靈活性。

為了解決產品快速上市的壓力,全新元件旨在協助開發團隊提升設計效率。例如針對接收器、轉換器和發送器等功能提供即時可用的預先驗證IP,使設計人員能專注於開發其設計的高附加價值特性。預先驗證的影像IP和參考設計不僅縮短設計週期,還能免費立即獲得。此外,這些IP在CrossLink和CrossLinkPlus產品系列均可重複使用。

萊迪思還提供便於使用的硬體和軟體工具來模擬功能表現、驗證系統級功能、加速產品開發。元件上的嵌入式快閃記憶體讓設計人員可以在現場更新位元流,滿足不斷變化的市場需求。優化的CrossLinkPlus能協助工程師解決嚴格的尺寸和功耗限制問題,同時避免使用外部快閃記憶體產生更多功耗。

| 圖二 : CrossLinkPlus FPGA不僅提供高效能的MIPI D-PHY,而且功耗極低(source:萊迪思) |

|

萊迪思為加速產品開發提供了大量支援。例如定期推出基於CrossLink和CrossLinkPlus的全新參考設計。這些參考設計都是為在全新或現有產品設計上實現具有高需求的影像橋接特性而定製的。

全新應用

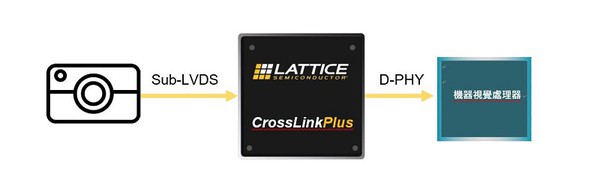

CrossLinkPlus的常見使用案例,顯示出它可以賦予設計人員高度的設計靈活性。圖三描述如何使用該元件橋接不同介面的感測器和處理器。此案例中,設計人員面臨到一個問題:一方面他們希望利用MIPI處理器的成本、效能和尺寸的優勢,但同時希望保留採用行業標準的現有攝影鏡頭。在圖三的機器視覺應用中,設計人員採用CrossLinkPlus來橋接Sub-LVDS介面的攝影鏡頭和D-PHY介面的MIPI處理器。

| 圖三 : 在此應用範例中,CrossLinkPlus FPGA在Sub-LVDS攝影鏡頭與機器視覺處理器的MIPI I/O之間起到橋接的作用(source:萊迪思) |

|

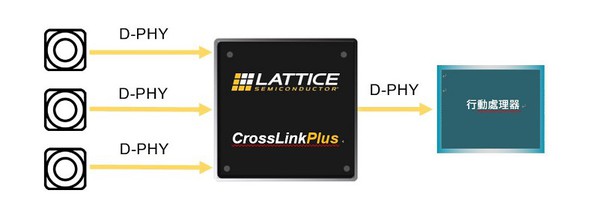

CrossLinkPlus的第二個潛在應用是整合多個感測器的輸入,並將其發送至應用處理器。例如,在圖四中,三個圖像感測器通過三個D-PHY埠與CrossLinkPlus元件連接。CrossLinkPlus將感測器資料整合,通過單個D-PHY輸出至處理器。設計人員可以透過這種整合功能優化使用處理器有限的I/O資源。

| 圖四 : CrossLinkPlus可以在一個埠上整合多個感測器訊號,節省處理器的I/O(source:萊迪思) |

|

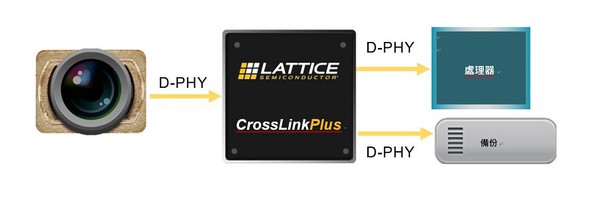

設計人員還可以使用CrossLinkPlus來實現MIPI分離訊號或複製。在圖五中,設計人員將來自感測器的訊號饋送到CrossLinkPlus元件中,然後將其輸出拆分或複製到兩個單獨的輸出中。萊迪思認為此方法應用於智慧汽車的ADAS或注重資料重複將會越來越多。

在此案例中,來自攝影鏡頭的訊號進入CrossLinkPlus元件,並被複製到兩個輸出流中。一個被發送到即時處理資料的應用處理器,另一個被存檔到本地或雲端進行資料記錄和備份,類似飛機的黑盒子。若發生故障或交通事故,調查人員可以查看資料備份,確定事故原因。

| 圖五 : 該ADAS視覺系統中,CrossLinkPlus FPGA複製攝影鏡頭訊號輸出,發送至應用處理器和資料備份處(source:萊迪思) |

|

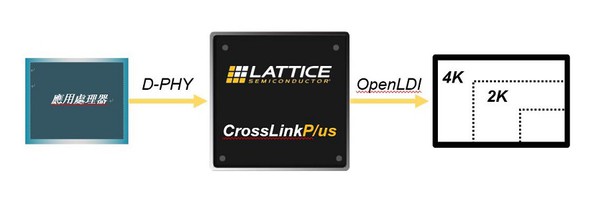

圖六展示設計人員如何使用CrossLinkPlus將傳統顯示器連接到全新高效能AP。由於OpenLDI顯示器通常比MIPI顯示器大很多,因此許多工業控制應用在連接OpenLDI介面的傳統顯示器和AP時,需要採用橋接元件。全新MIPI應用處理器透過D-PHY將資料傳送到CrossLinkPlus後,該元件使用OpenLDI橋接,將資料發送到傳統顯示器。此外,CrossLinkPlus可用於橋接非MIPI介面的圖像感測器和MIPI AP。

| 圖六 : 在該應用範例中,萊迪思CrossLinkPlus實現傳統顯示器和現代應用處理器之間的連接(source:萊迪思) |

|

CrossLinkPlus讓設計人員加速嵌入式視覺開發。透過將FPGA的可重複程式化設計特性引入嵌入式視覺系統,CrossLinkPlus讓設計人員可以利用MIPI元件提供的成本和效能優勢。其硬核D-PHY介面可提供先進的效能,而其嵌入式快閃記憶體可實現瞬時顯示的效能。該元件的運行功耗極低且尺寸小,有助於簡化散熱管理,對各類常用介面和傳統介面提供最大限度的設計靈活性。最後,全面、預先驗證並且擁有免費IP的CrossLinkPlus進一步加快開發速度,讓設計人員將更多時間用於設計最核心的部分—提升競爭優勢。