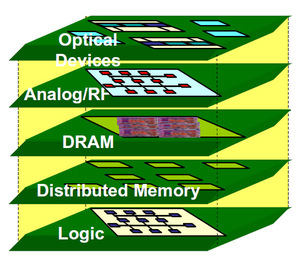

在晶片微型化的過程中,兼具效能是非常關鍵的目標。如何在更小的晶片尺寸中,塞進更多的功能,一直是半導體業者所努力的研發方向。而所謂的「3D IC」製程,也是在此前提下所產生的技術,除了邏輯電路的微型化之外,還企圖將記憶體、MEMS與射頻晶片等晶片也一併以3D堆疊的方式,整合至單一個晶片中,此法不但能縮小體積,在應用與性能上也超過傳統的晶片,也因此3D IC被認為是次世代的主流晶片技術之一。

|

| 所謂的「3D IC」製程,也是在此前提下所產生的技術,除了邏輯電路的微型化之外,還企圖將記憶體、MEMS與射頻晶片等晶片也一併以3D堆疊的方式,整合至單一個晶片中 |

然而,3D IC技術提出至今,除了在CMOS影像感應器和記憶體領域有初步的成果之外,在其它的市場上依然沒有任何商用的契機出現,而要推演至真正使用3D IC的系統產品上市,那更是遙遙無期。其中的關鍵點,除了生產設備商與晶片業者必須積極推動之外,EDA工具與量測廠的加入也關鍵至極。因此,相關上中下游的業者如何齊聚起來,並在短時間內催生一套實用的標準,將決定3D IC日後發展的盛與衰。

那3D IC究竟為什麼如此難以突破呢?目前的困難點不外乎幾個。首先,晶片3D堆疊的散熱問題仍難以克服。由於傳統的平面晶片可以著靠散熱片或者銅線來進行散熱,但當晶片必須堆疊的時候,散熱問題則會因堆疊的晶片彼此傳熱而加重,並造成封裝與系統設計上的困難。現在業界仍沒有一個適合商用的對策,因此也減緩了3D IC的發展。

再者,EDA工具商介入太少也是主因之一。現在檯面上有能力生產3D IC的廠商,幾乎都是in house的方式,屬於閉關練功的狀態。這些公司所使用的設計工具都是自行開發或者土法煉鋼,並沒有一套專為3D IC開發所設計的工具可用。多家從事3D IC的業者就指出,缺乏EDA工具是目前3D IC普及的一大障礙,若有一套專用的自動化工具,不但能大幅減少開發時間,也能建立起業者彼此溝通的平台。

其三,則是量測與驗證工具的缺乏。也同樣在業者各唱各調的狀況下,目前並沒有一套量測標準和測試驗證設備可為3D IC做背書,僅靠各家提出的產品數據,將難以取信客戶與市場;而沒有專屬的量測工具,對於生產流程和品質良率的建立也將是困難重重。以上這幾個問題都是3D IC想更進一步發展,所必須立即突破的障礙。

對於3D IC的製程也興趣濃厚的晶圓代工廠台積電就曾表示,3D IC在未來10年內將很難出現大規模普及。因要在單一個晶片內蓋出平房、樓房和地下室這絕非易事,而且這也不是單一業者可以做到,必須整個產業一起進行才有可能。加上還必須考慮到成本與市場的因素,因此短期間內難有作為。但台積電也指出,建立標準絕對是第一步。