Ramon的RC64多核處理器整合了64個CEVA-X1643 DSP,為衛星通訊、觀測和科學研究應用實現大規模的並行處理能力。

|

| /news/2015/06/15/1438391100S.jpg |

CEVA公司宣佈,擅長於為太空應用開發獨特抗輻射加固ASIC解決方案的無晶圓廠半導體供應商Ramon Chips公司已經獲得CEVA-X1643的授權許可,用於其瞄準高性能太空運算的RC64 64核並行處理器之中。Ramon將在RC64處理器中整合64個CEVA-X1643 DSP,為用於通訊、地球觀測、科學和其它許多應用的新一代衛星實現躍進式的運算能力。

RC64是一65nm CMOS並行處理器,提供384 GOPS、38 GFLOPS和60 Gbps資料率。除私有記憶體(private memory)和快取記憶體(cache)之外, 64 個CEVA-X1643內核中的每一個核也都可直接存取4MB共用記憶體,包括支援ECC。這些內核在執行時間由自動管理並行任務的硬體同步裝置進行管理,在各內核之間實現近乎完美的動態負載均衡,並且以非常高的速率和非常低的等待時間進行任務切換。

Ramon Chips執行長 Ran Ginosar教授表示:「近二十年以來,衛星處理器底層技術的演進幾乎是乏善可陳,導致目前處理密集型應用的性能較差。我們建基於CEVA-X1643 DSP的新型RC64處理器有望改變此一局面,為新一代衛星系統帶來卓越的性能、可程式設計性和可擴展性,實現許多最新衛星通訊、研究和觀測應用所需的大規模並行處理能力。」

CEVA公司行銷副總裁Eran Briman表示:「與Ramon Chips合作開發其RC64 64核DSP衛星處理器,這是我們DSP最大的多核使用案例之一。大規模並行處理是高性能太空運算的關鍵,而CEVA-X1643為Ramon所瞄準的嚴苛用例提供了出色的性能。」

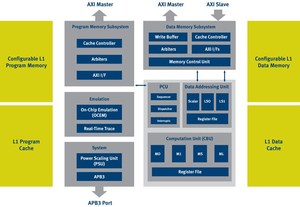

CEVA-X1643 DSP內核具有結合了單指令多資料(Single Instruction Multiple Data, SIMD)功能的超長指令字(Very Long Instruction Word, VLIW)架構,其32位元程式設計模式可支援高度的並行處理方式,包括每週期能夠處理多達8個指令,以及每週期實現16個SIMD運作。

CEVA-X1643具有建基於高性能AXI匯流排的記憶體子系統,採用完全快取式的(fully-cached)指令和具備ECC的資料記憶體,支援多核 (multi-core) 和眾核 (many-core) 架構,並且包括為動態和靜態功耗提供先進功率管理的創新性功率調節單元(PSU)。