三星电子今日宣布,已开发出业界首个12层的3D-TSV(Through Silicon Via)技术。此技术透过精确的定位,把12个DRAM晶片以超过6万个以上的TSV孔,进行3D的垂直互连,且厚度只有头发的二十分之一。

|

| /news/2019/10/07/2042046200S.jpg |

三星指出,该技术封装的厚度(720?)与目前的第二代8层高频宽记忆体(HBM2)产品相同,能协助客户推出具有更高性能与容量的次世代储存产品,且无需更改其系统配置。

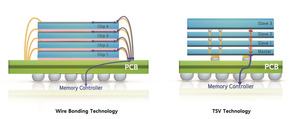

此外,新3D封装技术还具有比现有的引线键合技术短的晶片间数据传输时间,能显着提高速度并降低功耗。

三星电子TSP(测试与系统封装)执行??总裁Hong-Joo Baek表示,随着各种新的高性能应用的出现(如AI和HPC),能整合所有复杂的超高性能记忆体的封装技术变得越来越重要。随着摩尔定律达到其极限,预计3D-TSV技术的作用将变得更加关键。

此外,透过将堆叠层数从8个增加到12个,三星表示将很快能够量产24 GB高频宽记忆体,其容量是当今市场上8GB的三倍。